Цифровое устройство для ограничения чисел

Иллюстрации

Показать всеРеферат

А И

ОПИС Е

ИЗОБРЕТЕНИЯ

<)))767758

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву 9690477 с присоединением заявки ¹â€”

G 06 Г 7/52

Государствеииый комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 300980..Бюллетень № 36 (53) УДК 681.14 (088.8) Дата опубликования описания 3009)80 (72) Авторы изобретения

В.A.Êðèâåro, Э.А.Долинский и Л.А.Шабунина (71) Заявитель

/ (54) 1 ИфРОВОЕ УСТРОЙСТВО ДЛЯ ОГРАНИЧЕНИЯ

ЧИСЕЛ

2 выходы которого йодсбединены к информационным входам регистра операнда, а " управляющие входы регистра операнда и регистра результата соединены с шиной синхроимпульсов, выходы ре- гистра операнда через первый преобразователь кодов подсоединены к первым входам сумматора, а втЬрые входы первого преобразователя кодов соединены с выходом первого блока анализа знаков и младшим разрядом регистра результата, знаковые разряды регистра ограничителя и регистра операнда подключены соответственно к первым . и вторым входам первого блока анализа знаков и блока коррекции, второй преобразователь кодов и второй блок анализа знаков, выходы которого соединены соответственно со знаковыми, разрядами регистра операнда и регистра результата, выход второго блока анализа знаков через первый блок анализа знаков соединен с управляющим входом второго преобра- зователя кода, информационные входы ,которого соединены с выходами регистра операнда, а выходы - со вторыми входами сумматора.

Известное устройство решает задачу выделения заданной зоны чисел и огра1

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах цифровых вычислйтельных машин, работающих в системах управления и регу- 5 лирования, и является усовершенствованием известного устройства.

По основному авт.св. Р 690477 известно устройство ограничения, используемое преимущественно в ариф- )О метических устройствах управляющих цифровых вычислительных машин, работающих в контурах измерения различных параметров регулирующих систем.

Известное цифровое устройство or- 5 раничения по модулю, содержащее регистр операнда, регистр ограничителя, регистр результата, сумматор, первый преобразователь кодов, первый блок анализа знаков, блок коррекции,две 20 группы элементов И, группу элементов

ИЛИ и элемент И, управляющий вход которого соединен с выходом блока коррекции и управляющими входами первой группы элементов И, информацион- 25 ные входы первой и второй групп элементов И соединены с выходами сумматора, а их выходы через группу элементов ИЛИ соединены с информационными входами регистра результата,30 (22) Заявлено 060178. (21) 2568019/18-24 (51)

767758 ничения этой зоны чисел по модулю заданного числа, содержащегося в ячейке А запоминающего устройства

ЦВМ, определяемой командой DBM (" ограничитель ), засылаемоИ в регистр ограничителя В1 устройства ограничения. Далее в соответствии с. временной диаграммой реализуется математическая зависимость:

R, если /R С/ /а A 7/

А, если) .А 1/ />

Недостатками известного устройства являются сравнительно ограниченные функциональные возможности и сравнительно. низкая точность его работы в,"особых" точках вычислений, требующие введения дополнительных программных затрат ЦВМ для их повышения. Например, при работе на rpaнице разрядной сетки за счет дискретйости измерений возможны перепол- 25 нения разрядной сетки и тогда результат от предыдущей:.операции: т.е. содержимое регистра Р, являющееся операндом в операции ограничения, будет переполненным, но ложно удов- 3Q летворяющим условиям математической зависимости (1}, что приведет к неправильному выполнению закона регу- лирования, осушествляемрго ЦВМ. С целью устранения ошибок регулирова- 35 ния, т.е. повышения точности работы ЦВМ, следовательно, и устройства ограничения, в рабочую программу

ЦВМ вводится подпрограмма анализа разряда переполнения (Р ) и принятия соответствующего решения.

Кроме того, при отработке некото- рых законов управления требуется выделение зоны нечувствительности, аппаратно выражающееся в обнулении резУльтатов предыдущих вычислений 45 как ошибочных, в зависимости от анализа иа заданную константу. Данная операция до сих пор проводилась программным путем, требующим определенных программных затрат, и, 50 соответственно, времени для ее выполнения.

Цель изобретения - повышение точности устройства и расширение его функциональных возможностей. 55

Это достигается тем, что устройство ограничения содержит элемент НЕ-И,,триггер переполнения и дополнительный элемент ИЛИ, причем вы ходы знакового разряда и разряда переполнения регистра результата подключены к первому и второму входам элемента НЕ-И, выход которого связан с входом установки триггера переполнения, вход сброса которого является входом устройства, а выход триггера переполнения подключен к первому входу дополнительного элемента ИЛИ, второй вход которого связан со знаковым разрядом регистра результата, а выход дополнительного элемента ИЛИ связан с первым блоком анализа знаков.

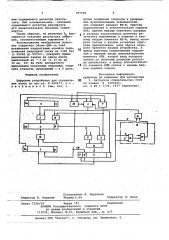

На чертеже представлена структурная схема устройства.

Устройство содержит регистр 1 операнда, регистр 2 ограничителя, регистр результата, сумматор 4, первый пребраэователь 5 кодов, первый блок б анализа знаков, блок 7 коррекции, группу элементов 8 И прямой передачи кодов, группу элементов 9 И передачи кодов со сдвигом влево, группу элементов 10 ИЛИ, элемент 11 И, второй преобразователь 12 кодов, второй блок 13 анализа знаков, дополнительный блок 14 анализа знаков, блок 15 анализа переполнения разрядной сетки, содержащий элемент 16

НЕ-И и триггер 17 переполнения.

Регистр 1 операнда (Р„ ) осуществляет промежуточное хранение ограничиваемых величин. Регистр 2 ограничителя (p ) предназначен для запоминания числа-ограничителя, котормм определяется зона чисел в операции

"ограничитель" н зона нечувствительности в операции "выделить зону нечувствительности". Регистр 3 результата (Р ) предназначен для хранения операнда, т.е. результата предыдущей операции или вводимой ив ЗУ ограничиваемой величины. Фиксирует значение результата исполнения текущей операции.

Сумматор 4 (СМ) совместно с преобразователями 5 и 12 кода предназначен для преобразования исходной информации в результат текущей операции.

Блоки б, 13, 14 анализа знаков и блок 15 анализа переполнения разрядной сетки предназначены для определения алгоритма исполнения операции сумматора. Груп элементов 8 и 9 И передачи кодов и группа элементов 10 ИЛИ осуществляют прямую или со сдвигом влево передачу результата на вход регистра 3 результата. Элемент 11 И осуществляет подачу единицы в младший (И-ый) разряд сумматора 4 в случаях обращения кода из прямого в дополнительный.

Устройство осуществляет функции ограничения и выделения зоны не- чувствительности, интерпретация которых заключается в следующем.

Ограничение — содержимое регистра результата остается без изменения, если оно по модулю меньше ограничителя, и разряд переполнения регистра результата равен

767758 (К, если (0, если

Ь (Р

К/С (A) (3) Устройство при выполнении функции ограничения работает следующим образом.

Ограничиваемое число заносится в регистр 3, оно не может быть результатом предыдущей операции. Модуль ограничителя заносится в регистр ограничителя 2. Числа считаются положительными, если их знаковйе старшие левые разряды находятся в состоянии нуля и отрицательными, если в состоянии единицы. При передаче первого синхроимпульса ограничиваемое число переписывается из 40 регистра 3 в регистр 1. Для определения большего по модулю из чисел, подготовленных в регистрах 1 и 2, на вход первого слагаемого сумматора

4 через группу элементов И прямой 4 передачи кодов 5 поступает содержимое регистра 2. На вход второго слагаемого сумматора 4 через преобразователь 12 кодов поступает содержимое регистра 1 в прямом коде, если О оно отрицательное, или в обратном коде, если оно положительно. Анализ знаков в этом случае ведется первым блоком б анализа знаков, он же выбирает соответствующие сигналы, управляющие работой преобразователей

5 и 12.

В случае передачи первый или второй входы сумматора обратного (инверсного) кода одного из слагаемых через элемент 11 И в цепь переноса младше- 4() го разряда сумматора 4 с блока 7 коррекции синхронно суммированию этих чисел подается единица. Анализ знака содержимого регистра 1 операнда осуществляется вторым блоком 13 ана- у

i нулю (т.е. переполнение разрядной сетки не имело места). В случае, если модуль содержимого регистра результата больше содержимого ограничителя или признак переполненйя регистра результата равен единице (т.е. в предыдущей операции имело место переполнение разрядной сетки), то на регистре результата фиксируется модуль значения ограничителя со знаком результата. Выделение зоны нечувствительности — содержимое регистра результата остается без изменения, если оно по модулю меньше ограничителя, в случае, если модуль содержимого регистра результата больше содержимого ограничителя, то регистру результата присваивается нулевое значение.

Математическая запись алгоритмов операции "ограничение": й, если /К/((A) и Р =0

РзфР,если/8/7 (Р7 или Ф 1 (2) выделение зоны нечувствительности: лиза знаков, который является дополнительным к первому блоку б анализа знаков.

Блоки анализа знаков представляют собой набор логических элементов И, ИЛИ, вырабатывающих управляющие сигналы для управления преобразователями 5 и 12 кодов.

Результат вычитания модулей содержимого регистра 2 ограничителя и регистра 1 операнда записывается через группу элементов И 8 и ИЛИ 10 в регистр 3 результата.

Новое значение регистра 3 результата анализируется по знаку результата вторым блоком 13 анализа знаков и дополнительным блоком 14 анализа знаков, представляющем собой логический элемент ИЛИ.

Алгоритм анализа определяется также состоянием блока переполнения разрядной сетки, т.е. состоянием знакового разряда и триггера 17 переполнения, который устанавливается по концу предыдущей операции при наличии единицы на выходе схемы 16 сравнения знакового разряда и разряда переполнения регистра результата.

Если знак результата положительный, то модуль содержимого регистра 2 (ограничитель) при вычитании был больше, если знак отрицательный, то меньше.

В первом случае (при положительном знаке Р ) в следующем такте на вход первого слагаемого поступает нуль, на вход второго слагаемого через вентили прямой передачи преобразователя 12 кода поступает содержимое операнда 1, т.е. происходит сложение с нулями содержимого регистра 1 операнда и перепись его (ограничиваемого числа) в регистр 3 результата.

Во втором случае (при отрицательном знаке Р ) или наличий переполнения разрядной сетки, что фиксируется на блоке .15, в следующем такте на вход слагаемого сумматора

4 через элементы И 5 поступает содержимое регистра 2 ограничителя при положительном знаке ограничителя или инверсия содержимого регистра

2 ограничителя с прибавлением .единицы в младшйй разряд сумматора 4 при отрицательном знаке ограничителя. На вход второго слагаемого сумматора 4 поступает "0". Результат с сумматора переписывается через группу элементов И 8 и ИЛИ 10 в регистр 3 результата.

Таким образом, на регистре Р> фиксируется значение результата, соответствующее выражению(2).

Ход выполнения алгоритма идентичен операции ограничения. При анализе знака результата Р>, если он положителен, производится обнуле8

767758

Формула изобретения

Составитель В. Березкин

Техред А.Aч Корректор Л. Иван

Редактор T. Портная,Заказ 7228/54 Тираж 751 ПодписноЕ

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ние содержимого регистра результата. При положительном значении содержимого регистра результата

его первоначальное значение сохраняется.

Таким образом, на регистре Р фиксируется значение результата операции, соответствующее выражению 3

Йспользование изобретения позволит сократить объем ЦВМ за счет исключения подпрограмм анализа пере, полнения разрядной сетки на 1300 бит (с 52000. до 50700); ускорйть"время выполнения задачи иа одном цикле вычислений на 3 мс (с 33 мс до

30 мс, 9:э) за счет аппаратного выполнения указанных операций; повысить точность вычислений - в 2 раза.

Цифровое устройство для ограничения чисел по авт.св. Ф 690477, о т: л и ч а ю.щ е е с я тем, что, с целью повышения точности и расширения функциональных возможностей, оно содержит элемент НЕ-И, триггер переполнения и дополнительный элемент

ИЛИ, причем выходы знакового разряда

5 и разряда переполнения регистра результата подключены к первому и второму входам элемента НЕ-И, выход кото рого связан с входом установки триггера переполнения, вход сброса которого является входом устройства, а выход триггера переполнения подключен к первому входу дополнительного элемента ИЛИ, второй вход которого связан со знаковым разрядом регист- . ра результата, а выход дополнительно15 го элемента HJIH связан с первым блоком анализа знаков.

Источники информации„ принятые во внимание при экспертизе

20 1. Авторское свидетельство СССР по заявке Р 2490421, кл. G 06 F 7/39, 1977 (прототип).