Устройство для контроля схем сравнения

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii 767767

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски н

Социалистическин

Республик

Ф

1 (61) Лонолнительное к аЖ. свил-ву (22) Заявлено 28.08.78 (2 I ) 2661590/18-24 (5l)M. Кл.

GO6 F 11/22 с присоединением заявки ¹ (23) Приоритет—

Государственный комитет по делам изобретений н открытий

Опубликовано 30.09.80 Бюллетень №36

Jl,àòà опубликования описания 03. 10.80 (53) УДК 681, .326.7 (088.8) Ю. А. Кипецкий и А Ф. Теслюк (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СХЕМ

СРАВНЕНИЯ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств проверки электронных блоков дискретной автоматики и вычислительных машин.

Известно устройство для проверки схем сравнения, содержащее два двоичных счетчика, выходы разрядов которых подклю— чены ко входам проверяемой схемы срав10 нения, триггер, элемент неравнозначности и индикатор (1 ). В этом устройстве входы переполнения двоичных счетчиков соединены со входами триггера, один из выходов которого и выход проверяемой схе15 мы сравнения связаны со. входами элемента неравнозначности, выход которого подключен ко входу индикатора, причем входы обоих двоичных счетчиков соединены с шиной тактовых сигналов, а вход одного из них — с входной шиной предварительной установки.

Недостаток такого устройства в том, что схема сравнения не проверяется на разность двух чисел, участвующих в срав нения, причем для этой неполной проверки требуется 2 " тактовых сигналов, где тт - разрядность схемы сравнения.

Наиболее близким техническим решением к изобретению является устройство для проверки схем сравнения, содержащее триггеры, блок формирования сигнала ошибки, два счетчика, входы которых через соответствуюшие элементы И соединены с тактовым входом устройства, а выходы подключены ко входам проверяемой схемы сравнения(2 1.

K недостатку известного устройства относится большое время проверки схемы сравнения, которое равняется 2т +, где — разрядность схемы сравнения.

Цель изобретения повышение производительности работы устройства.

Поставленная цель достигается тем, что в устройство для контроля схем сравнения, содержащее блок формирования сигнала ошибки, первый, второй и третий триггеры, первый и второй элементы

767767 сигналу, поступающему по входу 11, в регистрах 2, 3 производится сдвиг информации на один разряд вправо. За tl тактов, где и — разрядность схемы сравнения, логические единицы проходят поочередно все разряды регистров сдвига. При этом числа "в регистрах сдвига равны, что соответствует нулевым состояниям триггеров 5,6. Блок 8 выдает 0 на выход 12 сигнал "ИСПРАВНО" при .наличии сигнала 1(нли сигнал HE1

ИСПРВНО при отсутствии сигнала X q

При сдвиге логических единиц в последние разряды регистров сдвига (p -й

15 тактовый сигнал) триггеры 4,7 по счетным входам устанавливаются в, единичные состояния, На вход первого разряда первого регистра 2 сдвига через первый элемент

И-ИЛИ 9 поступает логическая единица, а на вход первого разряда второго регистра 3 сдвига с выхода второго элемента И-ИЛИ 10 — логический нуль. Работа . элементов И-ИЛИ 9, 10 описывает-.

25 ся следующими уравнениями: о

I о п@1 и С 21

Ь =а„81ч Ь„42, - --И-ИЛИ, причем единичный выход первого триггера соединен с единичным входом второго триггера и с первым входом первого элемента И- ИЛИ, нулевой выход первого триггера связан с первым входом второго элемента И-ИЛИ, единичный выход второго триггера — с первым входом блока формирования сигнала ошибки, выход которого является выходом устройСтва, выход контролируемой схемы срав нения — со вторым входом блока формир вания сигнала ошибки, третий вход которо го подключен к единичному выходу третье го триггера, а тактовый вход устройства соединен с тактовыми входами второго и третьего триггеров, введены первый и второй регистры сдвига и четвертый триг гер. При этом выходы первого и второго элементов И-ИЛИ соединены с информационными входами первого и второго регистров сдвига соответственно, информационные выходы первого и второго региг ров сдвига — с первым и вторым входами контролируемой схемы сравнения, а выход переполнения первого регистра сдвига— со счетным входом первого триггера и с вторыми входами первого и второго элементов И-ИЛИ. Выход переполнения второго регистра сдвига соединен с тре-. тьими входами первого и второго элемен- тов И-ИЛИ и со счетным входом четвертого триггера, нулевой выход которого связан с четвертыми входами первого и второго элементов И-ИЛИ, а единичный выход четвертого триггера — со входом третьего триггера, тактовый вход устройства подключен к тактовым входам первого и второго регистров сдвига.

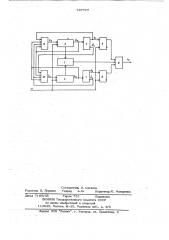

Схема устройства представлена на чертеже.

Она содержит контролируемую схему 1 сравнения, первый 2 и второй 3 регистры сдвига, первый 4, второй 5, третий 6 и четвертый 7 триггеры, блок 8 формирования сигнала ошибки, первый 9 и второй 10 элементы И-ИЛИ, вход 11 — такговый вход устройства.

Устройство работает следующим образом.

Перед началом проверки схемы сравне- .

50 ния триггеры 4 — 7 сбрасываются в нулевое состояние, в первые разряды регистров 2, 3 сдвига записываются логические единицы, а остальные разряды обнуляются (цепи начальной установки устройства не показаны). Схема 1 сравнения выдает на блок 8 сигнал X< (А =-3). где A и 3 — числа в регистрах 2 и 3 соответственно. По каждому тактовому где 4g, Ьо — выходы первого и второго ! элементов И-ИЛИ соответетвенно;

0 h, t)> — выходы последних разря дов первого и второго регистров сдвига соответ.ственно;

G, Оj — прямые выходы первого и второго триггеров соответственно;

Q„, Ц вЂ” инверсные выходы первого и второго триггеров соответственно.

По (1 ) -му тактовому сигналу в третий 6 и.четвертый 7 триггеры и в первый разряд первого регистра 2 сдвига записывается логическая единица, а в первый разряд второго регистра 3 сдвига - логический нуль. Схема 1 сравнения выдает на блок 8 сигнал Х (А19), Тактовые сигналы от (й +1)-го до (2 И )-ro сдвигают логическую единицу в регистре 2 сдвига,в регистре 3 в сдвиге участвуют нули во всех разрядах. При этом числа А В, что соответствует единичным состояниям триггеров. По (2 n )-му тактовому сигналу первый триггер 4 опрокидывается по счетному входу и логическая единица с выхода последнего разряда регистра сдвига 2 б изобретениъ

5 7677 через второй элемент И-ИЛИ 10 поступает на вход первого разряда регистра 3 сдвига, а на вход первого разряда регистра 2 .сдвига с выхода первого элемента И-ИЛИ

9 подается логический нуль.

По (2И +1)-му тактовому сигналу в первый разряд регистра 3 сдвига заносится логическая единица, а в первый разряд регистра 2 сдвига — нуль. Одновременно в триггеры 5 и 6 записывают- >0 ся логические 0" и 1 соответственно.

Схема 1 сравнения выдает на блок 8 сигнал Х (Д (В ). Тактовые сигналы от (2п+1)-го до (3 О )-го сдвигают логическую единицу в регистре 3 сдвига, в, Н регистре 2 в сдвиге участвуют нули во всех разрядах. При этом числа А< В, что соответствует нулевому состоянию второго триггера 5 и единичному состоянию третьего триггера 6. По {3 И )-му рр тахтовому сигналу четвертый триггер 7 опрохидывается в нулевое состояние, а на входы первых разрядов регистров 2, 3 сдвига с выхода последнего разряда регистра 3 сдвига через элементы И-ИЛИ 2з

9 и 10 поступают логические единицы.

По истечении ЗИ тактовых сигналов устройство подготовлено к следующему циклу проверки схемы сравнения.

Блок 8 формирования сигнала ошибки зо строится в соответствии со следующей таблицей состояний

6 7

Форм ул а

4S

1. Авторское свидетельство СССР

М 473180, кл. 506 F 7/04, 1973.

2. Авторское свидетельство СССР

М 583436, кл. Q 06 Р 1 1/00, 1976 (прототип) .

2" +"

А=—

5Н

О 1 О 0 АВ

1 О 1 О А>В

1 О 0 1 A<8

Таким образом, в связи с тем, что проверха схемы сравнения осуществляется эа 3 и тахтов, где p — разрядность схемы сравнения, время проверки схемы сравнения при помощи предлагаемого устройства сокращается по сравнению с временем проверхи устройства прототипа в

iq раэ, где

Устройство для контроля схем сравнения, содержащее блок формирования сигнала ошибки, первый, второй и третий триггеры, первый и второй элементы

И-ИЛИ, причем единичный выход первого триггера соединен с единичным входом второго триггера и с первым входом первого элемента И-ИЛИ, нулевой выход первого триггера соединен с первым входом второго элемента И-ИЛИ, единичный выход второго триггера соединен с первым входом блока формирования сигнала ошибки, выход которого является выходом устройства, выход контролируемой схемы сравнения соединен со вторым входом блока формирования сигнала ошибки, третий вход которого. соединен с единичным выходом третьего триггера, тактовый вход устройства соединен с тактовыми входами второго и третьего триггеров, о т л и— ч а ю щ е е с я,тем, что, с целью повышения производительности, в устройство введены первый и второй регистры сдвига и четвертый триггер, причем выходы первого и второго элементов И-ИЛИ соединены с информационными входами первого и второго регистров сдвига соответственно, информационные выходы первого и второго регистров сдвига соединены с первым и вторым входами кочтролируемой схемы сравнения, выход переполнения первого регистра сдвига соединен со счетным входом первого трМггера и со вто- рыми входами первого и второго элементов И-ИЛИ, выход переполнения второго регистра сдвига соединен с третьими входами первого и второго элементов

И-ИЛИ и со счетным входом. четвертого триггера, нулевой выход которого соединен с четвертыми входами первого и второго элементов И-ИЛИ, единичный выход четвертого триггера соединен со входом третьего трштера, тактовый вход устройства соединен с тактовыми входами первого и второго регистров сдвига.

Источники информации, принятые во внимание при экспертизе

767767

Составитель И. Сигалов

Редактор И. Груэова Техред А.Ач Корректор Ю. Макаренко

Заказ 7196/45 Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР йо делам изобретений и открытий

113038, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4