Число-импульсный функциональный преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

««767770

Ф

1 а (61) Дополнительное к авт. свид-ву (22) Заявлено 24.07.78 (21) 2648451/l8-24 с присоединением заявки ¹.3 (51)М. Кл.

606 F 15/Зс

Государственный комитет

СССР по пенам изобретений и открытий (23) Приоритет

Опубликовано 30.09.80. Бюллетень № 36

Дата опубликования описания 02.10.801 (53) УДК 681.3 (088,8) (72) Автор изобретения

А. Г. Шевяков

Рязанский радиотехнический институт (71) Заявитель (5 4) ЧИСЛО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано либо в качестве автономного устройства для обработки число-импульсной информации, либо в составе цифровых интегрирующих машин или в других специализированных вычислительных устройствах.

Известно устройство, содержащее ,счетчйк приращений аргумента, счетчик отрезков, дешифратор — шифратор, блок .число-импульсного умножения, состоящий из элементов И, ИЛИ и линейных преобразователей, а также дополнительных елемелтое И, ИЛИ и линии задержки 11).

Недостатком его является невозможность воспроизведения функций„ для которых выполняется соотношение „ 7 1,,"(е. т.е, функций, имеющих первую роизводную больше единицы.

Из известных устройств наиболее близким к изобретению по технической сущности яв.цяется устройство, содержащее счетчик приращения функции, блок

2 памяти и блок умножения, потенциаль; ные входы которого соединены с выходами блока памяти (2).

К недостатку устройства следует отнести невозможность воспроизведения

5 фуиклии е области у 1, т.е. и об1Дч

1с3 х ласти, где модуль производной превышает единицу.

Цель изобретения — расширение функ l0 циональных возможностей преобразователя путем вычисления функции в области (-Ą— - т 1.

Указанная цель достигается тем, что в устройство, содержащее счетчикк приращения функции, блок памяти и блок умножения, потенциальные входы которого соединены с выходами блока памяти, дополнительно введены два ключа, триггер, два элемента И и два элемента ИЛИ. При этом первые входы ключей и первого элемента И подключены к выходу дополнительного разряда ячейки блока памяти, вторые входы первого ключа и первого ,элемента И - ко входу кода аргумента

767770

3 устройства. Выход первого элемента И соединен с единичным установочным входом триггера, нулевой устапвочный вход которого связан с выходом блока умножения и вторым входом второго ключа, выход которого подхлючен к первому входу перво о элемента ИЛИ, вторым входом соединенного с выходом второго элемента И и с первым входом второго элемента ИЛИ. Первый вход второго элемента И соединен с выходом триггера, а второй вход является входом опорной частоты устройства, выход первого хлюча подключен ко второму входу второго элемента ИЛИ, выход которого соединен с импульсным входом блока умножения. Выход первого элемента ИЛИ является выходом приращения функции устройства и соединен со входом счетчика приращения функции, выходы которого подключены- ко ,входам блока памяти.

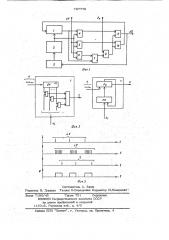

На фиг. 1 и 2 представлены схемы .предлагаемого устройства; на фиг. 3— диаграммы его работы.

Она содержит блок 1 умножения, блок

2 памяти, счетчик 3 приращения фунхции, ключи 4,5, элемент И 6, триггер 7, элемент И 8, элементы ИЛИ 9,10.

В функциональном преобразователе формирование приращения функции A, 3 по заданному приращению аргумента ЛХ осуществляется с использованием хусочнолинейной аппроксимации. При этом величина приращения ь У вычисляется в соответствии с моделирующими зависимостями, которые для 1 -го участка разбиения функции по оси имеют вид

ЬХ М1

ЬХ 2

ЬЧ = Р., (2)

И„11 где ЬХ, ЬЧ приращения аргумента и функции, представленные числом импульсов;

М1 коэффициент,определяющий наклон воспроизводимой функции„ когда ее первая производная ау (1 ° коэффициент, определяющий наклон той же функции в области, где 1;

ЙУ

N C (0,2 — 1) — козффииненты, раИ1 нимые в блоке 2 памяти ф м — разрядность блока число-импульсного умножения;.

О, если „ (1, — достояние дополЗу нительного старР.

1, если — )1 шего разряда выходного кода блока памяти коэффициентов,характеризующее величину производной функ. ции.

Рассмотрим работу устройства в двух режимах, выбор которых определяется состоянием Р1 дополнительного разряда выходного кода блока 2 памяти.

Выражения (1) и (2) реализуются с помощью блока 1 умножения, который может быть построен либо на основе двоичного умножителя, либо на основе накапго ливаюшего сумматора. На один вход блока 1 подается параллельный код Й1, на второй — число импульсов, равное И . При этом величина У. связана с И н М соотношением N u

1 2Фи (3)

Следует заметить, что, Ц представляет

1 собой двоичный код числа, которое может принимать значения от 0 до 2 и — 1.

ЗО Поэтому Z в результате всегда меньше

Предположим, что Р„"- О. В этом случае Р.; разрешает прохождение импульсов приращения ЬХ через ключ 5 и

35 далее через элемент ИЛИ 1 О на вход блока 1 умножения, на другие входы которого поступает код Й1 с выхода бфюка 2 памяти. С выхода блока 1 импульсы, количество которых определяется

4р соотношением (3), поступают через ключ

4 и элемент ИЛИ 9 на выход устройства и на вход счетчика 3 приращения функции.

В рассматриваемом режиме выражение

4S (3) аналогично (1) при И=ЬХ,поэтомуприращение функции М меньше приращения аргумента 6Х, так как всегN1 да меньше единицы,-Таким образом, при Р1 = 0 устройством, о формируется приращение ЬУ функции Ч(Х); для которой В g 1. йх

В другом режи,ме, когда P "- 1, ключи

4,5 заперты и импульсы приращениями .

Поступают через элемент И 6 на единичный установочный вход триггера 7, который предварительно установлен в 0".

Первый импульс приращения Ь.Х переводит

5 7677 триггер 7 в состояние 1". Потенциал Ц триггера 7 разрешает через элемент

И 8 прохождение частоты Fo на элемент ИЛИ 10 и далее на вход блока умножения. С выхода элемента И 8 импульсы частоты Fp через элемент ИЛИ 9 поступают на выход устройства и являются импульсами приращения функции ЬЧ

Первый же импульс, который появится 10 с выхода блока 1 после импульса аХ, установит триггер 7 по нулевому установочному входу в исходное состояние и прекратит подачу Fp на выход устройства.

Затем процесс повторяется для всех вновь 15 приходящих импульсов. приращения h, X .

При этом на выходе блока умножения 1 будет сформировано количество импульсов 7. = д Х ° Кроме того, учитывая (3) можно записать, что 20 дч й„rZYvI (4) так как в рассматриваемом режиме на вход блока умножения приходит количество импульсов, равное приращению функции Д3. 25

Таким образом, при Р1 " 0 устройство обеспечивает аппроксимацию участка функции с -д — <1, а при Р =1 — аппроксимацию функции с 1. дх

Выбор соответствующих коэффициен -" ЗО тов 8< иэ блока памяти 2 осуществляется с помощью счетчика 3, в котором накапливаются приращения д, образуя значения функции 3

Предложенный число-импульсный функциональный преобразователь имеет более широкие функциональные возможности чем прототип, простую структуру и легко может быть реализован на современной элементной базе цифровой техники. щ

Формула изобретения

Число-импульсный функциональный преобразователь, содержащий счетчик прира70 6 щения функции, блок памяти и блок умножения, потенциальные входы которого соединены с выходами блока памяти, о т— л и ч а ю шийся тем, что, с целью расширения функциональных воэможностей путем выполнения функции в .области 1 1,:в него введены два клю-! ча, триггер, два элемента И и два элемента ИЛИ, причем первые входы ключей и первого элемента И соединены с выходом дополнительного разряда ячейки блока памяти, вторые входы первого Фй>ча и первого элемента И подключены ко входу кода аргумента устройства, выход первого элемента И соединен с единичным установочным входом триггера, нулевойустановочный вход которого соединен с выходом блока умножения и вторым вхо-. дом второго ключа, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и с первым входом второго элемента ИЛИ, первый вход второго элемента И соединен с выходом триггера, а второй вход является входом опорной частоты устройства, выход первого ключа подключен ко второму входу второго элемента ИЛИ, выход которого соединен с импульсным входом блока умножения, выход первого элемента ИЛИ является выходом приращения функции устройства и соединен со входом счетчика приращения функции, выходы которого подключены ко входам блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 208349, кл. 606 7 3/00, 1970.

2. Авторское свидетельство СССР

¹ 428413, кл. 606 У 3/00, 1971 (прототип) .

Фиг,1 фиг,3

Составитель А. Зорин

Редактор И. узова Техред H.Барадулина Корректор 10.Макаренко "

Заказ 7196/45 Тираж 75 1 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и, открытий

1130д5, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4