Устройство для умножения

Иллюстрации

Показать всеРеферат

,1тно-тс.х нич !".. .

"" ."" эт- н 1 МГ /., (1I)767779

ОП ИКАНИЕ

Союз Советских

Социалистических

Республик

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВЙДВТИЛЬСТВУ (61) Дополнительное к авт. свид-ву г (22) Заявлено 01.08,76 (21) 2392283/18 — 24 с присоединением заявки № (2;3) Приоритет (51 ) М. Кл.

G 06 G 7/16

Гасударственный квинтет

СССР ва делам изобретений н открытий (53) УД К681.335 (088.8) Опубликовано 30.09.80. Бюллетень ¹ 36

Дата опубликования описания 30.09.80 (72) Автор изобретения

А. M. Косолапов

Куйбыйевский политехнический институт им. В. В. Куйбышева (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

Изобретение относится к области вычислительной и измерительной техники, может быть применено в измерительных устройствах для измерения мощности, расхода газа, в коррелометрах.

Известно устройство для умножения, содержащее реверсивные счетчики, цифроаналоговые преобразователи, нуль-органы, переключатели (1).

Это устройство отличается большой сложностью.

Наиболее близким техническим решением к изобретению является устройство, содержащее уэкодиапазонный блок умножения (2) .

Такое устройство не обеспечивает достаточной точности.

Цель изобретения — повышение точности устройства.

Поставленная цель достигается тем, что устройство содержит амплитудный анализатор, источник опорного напряжения, дискретно-изменяемые резисторы, сумматоры, причем первый вход устройства соединен со входом амплитудного анализатора и первым входом первого

" сумматора, второй вход которого через первый дискретно-изменяемый резистор связан с источником опорного напряжения, второй вход уст-. ройства — с первым входом узкодиапазонного блока умножения, второй вход которого соединен с выходом первого сумматора, а выхбд— с первым входом второго сумматора, второй вход которого через второй дискретно-изменяемый резистор соединен со вторым входом устройства, а выход второго сумматора является выходом устройства, выход амплитудного анализатора подключен к управляемым входам дискретно-изменяемых резисторов.

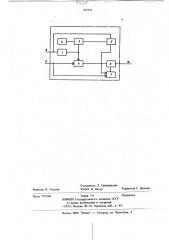

На чертеже приведена структурная схема устройства.

Преобразователь содержит амплитудный анализатор 1; источник 2 опорного напряжения, дискретно-изменяемые резисторы 3 и 4, сумматоры 5 и 6, узкодиапаэонный блок 7 умножения, входные 8 и 9 и выходную 10 клеммы.

Пуинцип действия предложенного устройства следующий.

Входной сигнал U@y,,поступающий на клемму 8, вызывает появление на его выходе соответствующих сигналов. Вследствие этого уста-

67779

25 нологии.

К = Ооп К41 навливаются определенные значения дискретноизменяемых резистороЬ 3 и 4, На выходе сумматора 5 формируется разность входного сигнала О т, и сигнала, поступающего от опор1 ного источника 2

U Ц,„-И „К„, 1 где U — сигнал на выходе сумматора 5;

Q „— сигнал на выходе источника 2;

t.

К4 — коэффициент передачи сумматора для сигнала от источника 2, зависящий от значения дисректно-изменяемо1 . го резистора 3.

Узкодиапазонный блок умножения перемножает сигналы с выхода сумматора 5 и с клеммы 9 (второй входной сигнал Ugg.2), так что на выходе второго сумматора 6 получается сигнал в соответствии с выражением

О =К И К, ), )„° ч sa где К вЂ” коэффициент передачи сумматора 6, определяемый значением дискретноизменяемого резистора 4;

K — коэффициент передачи множительного

Ъ блока 7.

Если выбрать соотношения между коэффициентами такими, чтобы

30 то И = ОЬ7,.1 Ug следовательно, выполняется операция умножения без методической погрешности.

Предложенное устройство позволяет существенно повысить точность по сравнению с исполь зуемым простейшим блоком умножения. Так при погрешности блока 7фт"-10 — 1% и И =5 пороговых элементов в амплитудном анаАизаторе 1 погрешность предложенного устройства получается соответственно 2 — 0,2% (= — ).

И 40

Погрешность устройства практически не зависит от стабильности характеристик пороговых элементов, что является существенным преимуществом предложенного устройства по сравнению с известным, где уровни квантования, 4 задаваемые с помощью преобразователей коднапряжение, должны устанавливаться с высокой степенью точности.

Для достижения еще более высокой точности выполнения операции умножения осуществля50, ется каскадное включение устройств, выполненных по предложенной схеме. При этом первое иэ них строится с применением известного простейшего множительного блока, а для второго в качестве множительного блока при55 меняется первое.

При каскадном включении точность повыШается в И,1.È2. ИЬ, где И, Vl> и g> — число пороговых элементов в первом, втором и третьем устройствах для умножения для трехкаскадной схемы построения, При каскадном включении требуется меньшее число пороговых элементов (в анализаторе), чем для однокаскадной схемы той же точности

Для изменения входных сигналов в широком диапазоне на обоих входах множительного устройства целесообразно такое соединение каскадов, когда на каждом входе включается амплитудный анализатор и дискретно-изменяемое сопротивление.

Например, для двухкаскадной схемы выход первого сумматора первого каскада подключается к дискретно-изменяемому сопротивлению и одному входу множительного устройства низкой точности второго каскада, а вход первого каскада, соединенный с дискретно-изменяемым сопротивлением первого каскада,— к амплитудному анализатору и первому сумма.тору второго каскада.

Предложенное устройство позволяет повысить точность в 10 и более раз по сравнению с известными быстродействующими множительными устройствами, также, как прототип, оно может быть реализовано методами интегральной техФормула изобретения

Устройство для умножения, содержащее узкодиапазонный блок умножения, о т л ич а ю щ е е с я тем, что, с целью повышения точности, оно содержит амплитудный анализатор, источник опорного напряжения, дискретно-изменяемые резисторы, сумматоры, причем первый вход устройства соединен с входом амплитудного анализатора и первым входом первого сумматора, второй вход которого через первый дискретно-изменяемый резистор соединен с источником опорного напряжения, второй вход устройства соединен с первым входом узкодиапазонного блока умножения, второй вход которого соединен с выходом первого сумматора, а выход — с первым входом второго сумматора, второй вход которого через второй

1 дискретно-изменяемый резистор соединен со вторым входом устройства, а выход второгб сумматора является выходом устройства, выход амплитудного анализатора соединен с управляемыми входами дискретно-изменяемых резисторов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР No 435530, кл. G 06 G 7/16, 1973.

2: Шило В. Л. Линейные интегральные схемы.

"Советское радио", 1974, с. 162-163 (прототип).

767779

Составитель Л. Снимщикова

Техред М. Петко Корректор С. 111екмар

Редактор И. Грузова

Заказ 7197/46

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4

Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5