Устройство для считывания информации из матричного накопителя

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Веслублик (is) 767834 (61) Дополнительное к авт. саид-ву

Р1)М. Кл. (22) 3аявлено . 2401 8 (21) 2573117/18-24 с присоединением заявки Ио

G 11 С 7/00

Госурарственный комитет

СССР но деяам нзобретеннй н открытий (23) Приоритет (5Ç) УД< 681. 3П..67 (088. 8) Опубликовано 300980, рюллетень М 36

Дата опубликования описания 30.09. 80 (72) Авторы изобретения

В.Ц.Глушков, A.Ã.ßåìåéöåâ и В.А.Милошевский

ПТБ

Йс ц 1 .!" ßÜ (71) Заявитель

{541 УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ

ИЗ МАТРИЧНОГО НАКОПИТЕЛЯ

Изобретение относится к вычислительной технике.и может быть использовано при построении интегральных постоянных запоминающих устройств.

Известно устройство для считывания информации из матричного HcLKo пителя, содержащее транзисторы выборки и дешифраторы 11l.

При считывании информации ток, протекающий через запоминающий эле- 10 мент перезаряжает паразитные емкости, подключенные как к стоку, так и к истоку открытого транзистора выборки, что ограничивает быстродействие. данного запоминающего устрой-15 ства.

Известно устройство для считывания информации, содержащее два дешифратора, транзисторы выборки, а также запоминающие элементы, организо- 20 ванные в виде матрицы (2l .

При считывании информации, хранимой в некотором запоминающем элементе, ток, протекающий через этот эле- 25 мент йерезаряжает паразитные емкости, I подключенные как к стоку, так и к истоку открытого транзистора выборки,что ограничивает быстродействие запоминающего устройства. 30

Из известных устройств наиболее близким по технической сущности является устройство для считывания . информации из матричного наКопителя, используемое в интегральном запоминающем устройстве (3).

Указанное запоминающее устройство содержит информационные транзисторы, организованные в матрицу, а также транзисторы„ соединяющие информаци-онные транзисторы с выходом разрядной шины и выполняющие функции ключей.

На затворы .информационных транзисторов сигналы подаются с выходов первого дешифратора. Затворы ключей транзисторов подключены к выходам второго дешифратора. При считывании информации, хранимой s некотором запоминающем элементе, если этому элементу соответствует информационный транзистор (записана 1 ),ток, протекающий через этот транзистор, заряжает паразитные емкости, подключенные как к стоку.так и к истоку ключевого транзистора, что уменьшает быстродействие этого запоминающего устройства.

Целью изобретения является увеличение быстродействия устройства.

767834

Поставленная цель достигается). тем, что в устройство для считывания информации иэ матричного нако.пителя, содержащее ключевые транзис торы, стоки которых подключены,к шине считывания, истоки — к соответствующим разрядным шинам накопителя, а затворы - к соответствующим управляющим шинам, шины выборки и нулевого .потенпиала, введены элемент задержки и шунтирующий транзистор, сток которого подключен к шине счйтывания, исток — к шине нулевого потенциала, а затвор через элемент задержки— к шине выборки.

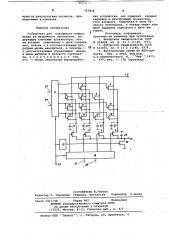

На чертеже показана схема предлагаемого устройства для случая, когда информационные транзисторы организованы в матрицу, имеющую -четыре строки и четыре столбца.

Предлагаемое устройство содержит ключевые транзисторы 1-4, информационные транзисторы 5-16, дешифраторы 17 и 18, элемент задержки 19, а также шунтирующий транзистор 20, Затворы информационных транзисторов, . расположенных в каждой строке в соответствии с кодируемой информацией, объединены между собой и подключены к выходам дешифратора 17.

Например, в первой строке закодирована информация 0101, во второй—

1110 и т.д. Истоки scex информационных транзисторов 5-16 объединены и подключены к шине источника питания. Стоки информационных транзисторов, расположенных в каждом столбце, . объединены и подключены к истоку соответствующего транзистора-ключа.

Затворы транзисторов-ключей подключены к выходам дешифратора 18, а стоки их объединены и соединены с шиной 21 считывания, исток — с шиной нулевого потенциала, а затвор через элемент задержки 19 соединен с шиной

22 выборки, которая также подключена к дешифраторам 17 и 18. Ко входам дешифраторов подключены также адресные шины 23 и 26.

Предлагаемое устройство функционирует следующим образом.

При наличии на шине 22 потенциала, близкого к E, потенциал на всех выходах дешнфратора 17 близок к нулю, потенциал всех выходов дешифратора

18 и затвора транзистора 20 близок к Е . В результате этого все ключевые транзисторы эакрйты,а шунтирующий транзистор 20 открыт и потенциал шины

21 считывания близок к нулю. Все информационные транзисторы 5-16 открыты и потенциал истока каждого транзистора ключа близок к . По приходу управляющего сигнала (нулевого потенциала) на шину 22 потенциалы всех, кроме выбранного, выходов дешифратоа 17 повышаются до E.. .Потенциал р выбранного выхода дешифратора 1 ос

17 оста ется близким к нулю. Потенциал выбранного выхода дешифратора 18 понижается до нуля и подключенный к нему ключевой транзистор 1 открывается, а потенциалы остальных выходов этого дешифратора не изменяются. При этом если на пересечении выбранных э столбца и строки отсутствует информационный транзистор(соответствует 0 двоичной информации), то после поступления нулевого потенциала на шину 22 и срабатывания дешифраторов : 17 и 18

® вышеописанным образом емкость .27 выбранного столбца разряжается через открытый транзистор-ключ, причем в течение времени прохождения Ф сигнала через элемент задержки 19 разряд идет

15 на заземленйый полюс источника питания через открытый транзистор 20, и

s это время шина 21 имеет потенциал, близкий к нулю, а остальное время после закрытия транзистора 20 остав2О шийся заряд на шине перераспределяется между емкостями 27 и 28, При этом время выбирается таким, чтобы напряжение на выходной шине 21 в конечном итоге не достигало порога срабатывания выходной схемы. Если же на пересечении выбранных строки и столбца матрицы информационных транзисторов имеется информационный транзистор (что соответствует 1 двоичной информации), то он открыт и

ЗО протекающий через него ток стремитcÿ сохранить потенциал E на шине емкости 27 и, кроме того, обеспечивает поступление тока на шину 21 считывания ° Через время 1 после начала дешифрации транзистор 20 закрывается, после чего начинает расти потенциал на шине 21 и по достижении величины порога срабатывания выходной схемы последняя срабатывает, завер4О шая процесс считывания 1 информации запоминающего устройства. За счет того, что параэитная емкость

27 выбранного столбца предварительно заряжена до напряжения Е и за время ь разрядилась незначительно, время от момента срабатывания дешифраторов до срабатывания выходной схемы заметно уменьшается по сравнению с прототипом.

50 Как следует из расчетов при пороге срабатывания выходной схемы, равном Ц2, и времени задержки 1 =30 нс, ;предлагаемое устройство по сравне;нию с прототипом имеет на 40% мень55 шее время считывания 1 . При этом сигналы 0 и 1 s предлагаемом устройстве отличаются по амплитуде не менее, чем в 2,5 раза, что обеспечивает надежное различение сигналов 1 и 0 в выходной схеме уст1 ройства.

Таким образом, предлагаемое запоминающее устройство имеет более высокое быстродействие, чем известное

65 запоминающее устройство, что подтвер767834

Формула изобретения

Составитель Ю.ушаков

Редактор Т. Горячева Техреду. Щепанская Корректор .О.Билак

Заказ 7211/48 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г, Ужгород, ул. Проектная, 4.ждается результатами расчетов, приведенными в описании.

Устройство для считывания информации из матричного накопителя, содержащее ключевые транзисторы, стоки которых подключены к шине считывания, истоки — к соответствующим разрядным шинам накопителя, а эатворы к соответствующим управляющим шинам, и шины выборки и нулевого потенциала, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства, оно содержит элемент задержки и шунтирующий транзистор, сток которого подключен к шине нулевого потенциала, а затвор через элемент задержки подключен к шине выборки.

Источники информации, принятые во внимание нри экспертизе

1. Авторское свидетельство СССР

Р 458036, кл. G 11 С 11/40, 1975. 2 ° Авторское свидетельство СССР

Р 523455, кл. G 11 С ll/40, 1976.

3. Интегральные схемы на МДП-приборах. Пер. с англ. под ред.

A.Н.Кармазинского. М., Мир,1975, с. 439, рис. 7. llб (прототип) .