Формирователь выходных сигналов для запоминающего устройства на кмдп-транзисторах

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистических

Республик (») 767835

Ж

° (61) Дополнительное к авт. свид-ву— (22) Заявлено 29.09.78 (21) 2668723/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) M. Кл з

G 11 С 7/00

Государственный комитет

СССР ио делам нообретеиий н открытой

Опубликовано 30.09.80. Бюллетень № 36

Дата опубликования описания 05.10.80 (53) УДК 681.327.

67 (088.8) В. В. Баранов, Ю. М. Герасимов, А. Н. Кармазинский и Э. П. Савостьянов (72) Авторы изобретения (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ВЫХОДНЫХ СИГНАЛОВ

ДЛЯ ЗАПОМИНАЮЩЕГО УСТР01 1СТВА

НА КМДП-ТРАНЗИСТОРАХ

Изобретение относится к вычислительной технике и может быть использовано при построении микромощных интегральных запоминающих устройств на КМДП-транзисторах, имеющих выходы с тремя состояниями.

Известны формирователи выходных сигналов для запоминающих устройств на

КМДП-транзисторах, содержащие "выходные транзисторы, соединенные с шиной питания, шиной нулевого потенциала и выходами логических элементов управления (1), (2) и (3), Основной недостаток — сложность конструкции.

Наиболее близким техническим решением к данному является формирователь выходных сигналов для запоминающего устройства на КМДП-транзисторах, содержащий четыре инвертора, два элемента ИЛИ-НЕ, элемент И-НЕ и элемент согласования, выход которого соединен с выходом формирователя, а первый, второй и третий входысоответственно с выходами элемента И-HE и первого и второго элементов ИЛИ-НЕ, первый вход элемента И-НЕ соединен с выходом первого инвертора и с входом второго инвертора, выход которого соединен с первыми входами элементов ИЛИ-НЕ, второй вход первого элемента ИЛИ-НЕ соединен со вторым входом элемента И-НЕ и с выходом третьего инвертора, второй вход второго элемента ИЛИ-НЕ соединен с выходом четвертого инвертбра, входы первого, третьего и четвертого инверторов соединены с

- " соответствующйми информационными и управляющими входами формирователя.

Кроме того, элемент согласования выпол10 нен на двух последовательно включенных

МДП-транзисторах р-типа и двух параллельно включенных МДП-транзисторах п-типа, образующих выходной каскад с тремя состояниями (4).

Недостаток этого формирователя — возможность прохождения ложных сигналов на выход при подаче управляющих сигналов раньше информационных сигналов, считываемых с разрядной шины запоминающего устройства, что происходит при выходе из уп режима хранения информации. Кроме того, этот формирователь чувствителен к помехам на разрядных шинах.

Цель изобретения — повышение надежности формирователя за счет исключения

767835

4 прохождения ложного сигнала и чувствительностй к помехам.

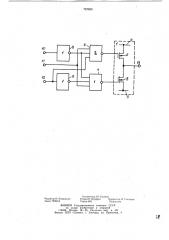

Поставленная цель достигается тем, что в формирователе выходных сигналов для запоминающего устройства на КМДП-транзисторах, содержащем два инвертора, элемент И-НЕ, элемент ИЛИ-HE и элемент согласования, выход которого соединен с выходом формирователя, а первый и второй входы — соответственно с выходами элементов И-НЕ и ИЛИ-НЕ, первый вход элемента ИЛИ-НЕ соединен с выходом первого инвертора, вход которого соединен с первым информационным входом формирователя, управляющий вход которого соединен со входом второго инвертора, первый вход элемента И-HE соединен с выходом первого инвертора, в-.орой вход элемента И-НЕ со1S единен со входом второго инвертора, выход которого "оединен со вторым входом элемен- т" ИЛИ-НЕ, третий вход которого соединен с третьпм входом элемента И-НЕ и вторым информационным входом формирователя.

Кроме гого, предпочтительно выполнять элемент согласования на МДП-транзисторе р-типа и МДП-транзисторе п-типа, затворы которых соединены с первым и вторым входами, стоки — с выходами, исток МДПтранзистора р-типа подключен к шине питания, а исток МДП-транзистора п-типа к шине нулевого потенциала.

На чертеже приведена электрическая схема формирователя, который содержит элемент 1 согласования, выполненный на

МДП-транзисторах п-типа 2 и и-типа 3, шине 4 питания и шине 5 нулевого потенциала, элемент 6 И-НЕ, элемент 7 ИЛИ-НЕ, первый 8 и второй 9 инверторы, первый 10 и второй 11 информационные входы, управ- д ляющий вход 12 и выход 13.

Информационные входы 10, 11 подключаются к первой и второй разрядным шинам запоминающего устройства.

Г ыходной каскад работает в режимах

"запрета г, считывания логических нуля или ед;гг ицы. В режиме запрета на управляющий вход 12 подан уровень логического нуля н нс".àâèñèìo от логических уровней на информационных входах 10, 11 на затворах транзисторов 2 и 3 устанавливаются соответствсггчг уровни логической единицы и лоп носко.о нуля, запирающие оба эти транзисторьг. В результате на выходе 13 устаггавливастся третье состояние, когда каскад

""ймеет высг кое выходное сопротивление.

Режим знпрста соответствует режиму хране- »О ння (отсу1ствию обращения) и режиму записи, ксг да формирователь отключается в запоминающем устройстве.

В режиме считывания на управляющий вход 12 подан уровень логической единицы.

Если ча первом информационном входе 10

" уровень соответствует логическому нулю (едннице), а на втором информационном входе 11 — логической единице (нулю), то на выходах элементов 6 и 7 установятся уровни логического нуля (единнцы).

В результате открывается (закрывается) транзистор 2 и закрывается (открывается) тра. зистор 3 элемента 1. Выход 13 устанавливается в состояние логической единицы (нуля).

На информационных входах 10, 11 в режиме хранения устанавливаются одинаковые уровни, поэтому при наличии разрешающего уровня на входе 12 элемент 1 будет находиться в третьем состоянии до тех пор, пока на информационных входах 10, 11 не появится считанная из запоминающего элемента информация, приводящая к установлению разноименных уровней на входах 10, 11.

Данный формирователь устраняет прохождение ложного сигнала с информацИон-ных входов 10, 11 на выходе 13 и повышает надежность работы запоминающего устройства в целом.

Формула изобретения

1. Формирователь выходных сигналов для запоминающего устройства на КМДПтранзисторах, содержащий два инвертора, элемент И-НЕ, элемент ИЛИ-НЕ и элемент согласования, выход которого соединен с выходом формирователя, а первый и второй входы — соответственно с выходами элементов И-НЕ и ИЛИ-НЕ, первый вход элемента ИЛИ-НЕ соединен с выходом первого инвертора, вход которого соединен с первым информационным входом формирователя, управляющий вход которого соединен с входом второго инвертора, отличающийся тем, что, с целью повышения надежности формирователя, первый вход элемента И-НЕ соединен с выходом первого инвертора, втот рой вход элемента И-НЕ соединен со входом второго инвертора, выход которого соединен со вторым входом элемента ИЛИ-НЕ, третий вход которого соединен с третьим входом элемента И-НЕ и вторым информационным входом формирователя.

2. Формирователь выходных сигналов

- по п. 1, отличающийся тем, что элемент согласования выполнен на МДП-транзисторе р-типа и МДП-транзисторе п-типа, затворы которых соединены с первым и вторым входами, стоки — с выходом, исток

МДП-транзистора р-типа подключен к шине питания, а исток МДП-транзистора п-типа— к шине нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1. Ж. «Electronic Design», ч. 21, 1973, №5, р.66 — 70:

2, Патент США № 3906255, кл. 340-172, 5, 1975.

3. Авторское свидетельство СССР по зая вке № 2501719/18-24, кл. G 06 F 3/04; —29.06.77.

4. Каталог фирмы NOTODOLA 1975, МС14502 (прототип) .

767835

Составитель Ю. Ушаков

Редактор И. Ковальчук Техред К.Шуфрич Корректор H. Гр горук

Заказ 7009/18 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и от крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <<Патент», г. Ужгород, ул. Проектная, 4