Многоустойчивый динамический запоминающий элемент

Иллюстрации

Показать всеРеферат

ОПИСЛНИК

ИЗО6РETEHИЯ

Союз Советскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 100577 (21} 2483128/18-24 (51) М. Кя. с присоединением заявки 89 (23) Приоритет

G 11 С 11/40

Государственный комитет

СССР но делам нзобретеннй н открытнй

Опубликовано300980, Бюллетень М Зб

Дата опубликования описания 3009,80 (5З} 4К 681.327. . б 7 (088. 8) (72) Авторы изобретен и я

A. И.Стоянов и В.С. Хорошунов

Bg(Т5 (71) Заявитель (54) МНОГОУСТОЙЧИВ11Й,ЦИНАМИЧЕСКИЙ ЗАПОМИНМй, ИЙ

ЭЛЕМЕНТ

Изобретение относится к вычислительной технике. и может использоваться при построении оперативных заломинаюших устройств.

Известны многоустойчивые фазоиипульсные запоминающие элементы, содержащие запоминающий конденсатор, два диода, узел заряда, разряда .и считывания информации.

Недостатками их являются сложность.10 конструкции и невозможность произвольной выборки.

Известны другие запоминающие эле.менты, сод1ьряащие полевой транзистор с. двойным затвором; один из зат- 15 воров является изолированным и служит для хранения заряда, а другой является управляющим. Такая конструкция позволяет хранить заряды различных величин, что повышает информаци- 20 онную емкость запоминающего элемента.

Этот запоминающий элемент, однако, имеет большое время записи и сложную конструкцию.

Наиболее близким техническим решением к предлагаемому изобретению. является динамический запоминающий элемент, содержащий информационный транзистор, затвор которого соединен 30 с первым выводом запоминающего конденсатора и с истоком транзистора записи, сток информационного транзистора соединен с истоком транзистора считывания, сток которого соединен со стоком транзистора записи и подключен к разрядной шине, затворы транзисторов записи и считывания подключены соответственно к шинам записи и считывания, а второй вывод запоминающего конденсатора и исток информационного транзистора соединены с шиной нулевого потенциала.

Недостатком этого запоминающего элемента является малая информационная емкость, так как он позволяет хранить всего 1 бит. информации.

Целью изобретения является увеличение информационной емкости запоминающего элемента за счет обеспечения хранения нескольких бит информации.

Это достигается тем, что в предлагаемый динамический запоминающий элемент введена шина опорного потенциала, которая соединена с истоком информационного транзистора.

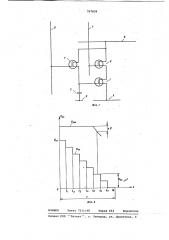

На фиг. 1 приведена электрическая схема предлагаемого многоустойчивогс динамического запоминающего элемента;

7б7839

Формула изобретения на фиг. 2 — временная диаграмма процесса считывания (Upi — напряжение на разрядной шине Оеп — напряжение на шине подачи опорного напряжения).

Иногоустойчивый динамический запоминающий элемент содержит информациойный транзистор l,òðàíçèñòoð считывания 2,.шину 3 опорного потенциа;ла,транзистор записи 4,запоминающий ,кондейсатор 5,разрядную шину б,шины считывания 7 и записи 8, шину 9 нулеsoro потенциала.

Нормальное функционирование за:ломинающего элемента обеспечивается при выполнении режимов записи информации, хранения информации, считывания и регенерации.

В режиме записи информации на шину

7 считывания информации подается низкий уровень, на шину 8 записи — высокий уровень, а на разрядную шину б — уровень напряжения, подлежащий записи в ячейку. Транзистор записи

4 открывается, и запоминающий кон.денсатор 5 заряжается. до уровня . напряжения, соответствующего записы ваемой информации и пропорционального пороговому напряжению транзисторов.

По окончании цикла записи на шину 8 записи подается низкий уровень, транзистор записи 4 закрывается и запоминающий элемент переходит в режим хранения информации, который характеризуется также запертым состоянием транзистора считывания 2.

В режине хранения информаций запоминающий конденсатор 5 изолирован от разрядной шины б и информация хранится в форме заряда, величина которого пропорциональна записанному напряжению. Для восьмиустойчивогб запоминающего элемента на запоминающем конденсаторе 5 хранится один иэ восьми уровней напряжения; например, при хранении первого уровня напряжения его значение равно утроенному значению порогового напряжения транзисторов.

В режиме считывания информации разрядная шина 6 предварительно заряжается до высокого уровня, на шину 3 опорного потенциала подается наивысший опорный потенциал, а на шину 7 считывания высокий уровень напряжения. Затем опорный потенциал уменьшается по ступенчатому закону, а информационный транзистор 1 открывается только в момент превышения хранящегося уровня напряжения опорного потенциала на величину, большую порогового напряжения транзисторов.

Этот момент фиксируется усилителем считывания, и информация распознается по промежутку времени, в котоf5 рый открываются транзисторы 1 и 2 (cM. фиг.2).

В режиме регенерации информации, котОрая осуществляется в два этапа, сначала производится считывание щ хранимой информации, а затем ее повторная запись.

Многоустойчивый динамический за- поминающий элемент, содержащий информационный транзистор, затвор которого соединен с первым выводом эапоминаюцего конденсатора и с истоЗ0 ком транзистора записи, сток информационного транзистора соединен с истоком транзистора считывания, сток которого соединен со стоком транзистора записи и подключен к разрядной

З5 шине, затворы транзисторов записи и считывания подключены соответственно к шинам записи и считывания,второй вывод запоминающего конденсатора соединен с шиной нулевого потен40 циала, отличающийся тем, что, с целью увеличения информационной емкости элемента, в него введена шина опорного потенциала, соединенная с истоком информационного транзистора.