Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

у 1ЪР 1 . I Р. б

t;:

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ () 767840

Союз Советских

Социалистических

Республик

Ф

« .л

Ф (61) Дополнительное к ав. свид-ву— (22) Заявлено 27.05.77 (21) 2490276/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) M. Кл.

G 11 С 17/00

Гооударстееиимй комитет

СССР

Опубликовано 30.09.80. Бюллетень №36 ао делам иэобретеиий и открытий (53) УДК 681 327

6 (088.8) Дата опубликования описания 05.10.80 (72) Авторы иЗобретения

А. И. Беляков, А. Н. Пресняков и А. И. Журавлев

Особое конструкторское бюро вычислительной техники

Рязанского радиотехнического института (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано при построении постоянных запоминающих устройств (ПЗУ).

Одно из известных ПЗУ содержит узел постоянной памяти, состоящий из m модулей, узел сменной информации, выходное устройство, схемы ИЛИ и блок блокировки, при этом вход первого канала выходного устройства соединен с выходом узла сменной информации, а вход второго канала соединен с выходом блока блокировки, вход которого соединен с выходом узла постоянйой памяти и с выходом схем ИЛИ, входы узла постоянной памяти и узла сменной информации объединены (1}.

Недостаток известного устройства ограниченная возможность коррекции за-писанной информации.

Наиболее близким техническим решением к данному изобретению является постоянное запоминающее устройство, содержащее m основных запоминающих модулей, адресные входы которых объединены (2).

Недостаток этого устройства — ограниченная возможность коррекции заййсайной информации, так как программирование запоминающего модуля производится путем пережигания плавких вставок микросхем памяти, входящих в состав запоминающего модуля. При этом в случае записи «1» в каком-либо разряде слова производится пережигание соответствующей плавкой вставки, при записи <е0» пережигание не производится. Из этого ясно, что при коррекции информации в модуле имеется возможность вместо «О» записать «1», т. е. пережечь соответствующую вставку, восстановить

10 плавкую вставку нельзя, т. е. нельзя записать «О» вместо «1», что приводит к необходимости замены модуля.

Цель изобретения — обеспечение коррекции записанной информации в устройствеДля достижения этой цели устройство содержит дополнительный запоминающий модуль, элементы И и коммутаторы по числу основных- запомйнающих модулей, при этом выходы каждого основного запоминающего модуля соединены" соответственно с первыми входами соответствующих коммутаторов и входами элемента И, выходы дополнительного запоминающего модуля подключены к соответствующим вторым входам коммута767840 выходами соответствующих элементов И.

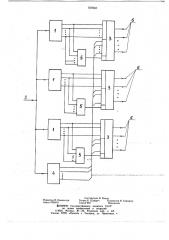

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит m основных запоминающих модулей 1, адресные входы которых объединены и подключены к входным шинам адреса 2, m коммутаторов 3, дополнительный запоминающий модуль 4, m элементов 5 И.

Устройство работает следующим образом.

Код адреса по адресным шинам 2 пода- so ется на основные запоминающие модули 1 и дойолнительный запоминающий модуль 4.

При этом с каждого основного запоминающего модуля 1 и с дополнительного запоминающего модуля 4 по соответствующему адресу считывается и-разрядное число. Если по данному адресу не производится коррек4О

45 подключение вторых своих входов к выходным шинам 6. На вторых входах коммутатора 3 имеется информация, считанная по этому адресу из дополнительного запоминающего модуля 4. Таким образом, на выходные шины коммутатора поступит информация, которая была считана с дополни- 55 тельного запоминающего модуля 4 и которая

- соответствует правильной информации.

3 торов, третьи входы которых соединены с ция информации, то и-разрядное число с выходов основных запоминающих модулей 1 поступаег саответственно на первые входы соответствующих коммутаторов 3 и далее на выходные шины, так как на третьи входы коммутаторов 3 в этом случае с выходов соответствующих элементов 5 И подается нулевой управляющий сигнал, разрешающий йрохождение информации с первых входов на выходные шины коммутаторов 3.

Предлагаемое устройство позволяет произвести коррекцию информации по несовпадающим адресам каждого из m основных запоминающих модулей 1. Это означает, что по данному адресу возможна коррекция информации одного из m основных запоминающих модулей 1. При этом предварительно по данному адресу в основной запоминающий модуль 1 заносится единичная информация, а в дополнительный запоминающий модуль 4 по тому же адресу заносится правильная информация.

Рассмотрим как работает устройство в этом случае, По определенному адресу в одном из основных запоминающих модулей 1 записаны все единицы. При считывании информат1йи "с "этого модуля на входы соответствующего элемента 5 И поступят все единичные сигналы. Одновременно на соответствующие первые входы соответствующего коммутатора 3 поступит та же информация.

На выходе данного элемента 5 И появится единичный сигнал, который поступит на третий вход соответствующего коммутатора 3. В этом случае коммутатор 3 производит

2S

4

Из рассмотрения работы ясно, что коррекция информации какого-либо основного запомйнающего модуля 1 возможна лишь в случае, если по данному адресу в других основных запоминающих модулях 1 ие записан единичный и-разрядный код. В противном случае на выходах нескольких элементов 5 И появится единичный сигнал, по которому соответствующие коммутаторы 3 подключают к выходным шинам выходы дополнительного запоминающего модуля 4, в котором записана информация лишь одного корректируемого основного запоминающего модуля 1.

В случае, если по одному и тому же адресу в основных запоминающих модулях 1 записана во всех разрядах единичная информация и ее не нужно корректировать, то для правильной работы устройства необходимо предварительно по этому адресу в дополнительный запоминающий модуль 4 записать и-разрядный единичный код. Тогда при считывании информации на выходных шинах соответствующих коммутаторов 3 появится единичная информация, соответствующая той, которая записана по данному адресу в каждом основном запоминающем модуле 1.

Таким образом, данное устройство позволяет осуществить коррекцию записанной информации без замены модуля, в котором произошла ошибочная запись информации.

Формула изобретения

Постоянное запоминающее устройство, содержащее m основных запоминающих модулей, отличающееся тем, что, с целью осуществления коррекции записанной информации в устройстве, оно содержит дополнительный запоминающий модуль, элементы И и коммутаторы по числу основных запоминающих модулей, при этом выходы каждого основного запоминающего модуля соединены соответственно с первыми входами соответствующих коммутаторов и входами элемента И, выходы дополнительного запоминающего модуля подключены к соответствующим вторым входам коммутаторов, третьи входы которых соединены с выходами соответствующих элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 264465, кл. G 11 С 17/00, 1968.

2. Микроэлектроника и полупроводниковые приборы . Сб. статей под -ред. А. А. Васанкова и Я. В. Федотова. Вып. 1, М., «Сов. радио», 1976, с. 54. рис. 3 (прототип):

767840

Составитель В. Вакар

Редактор И. Ковальчук . Техред К. Шуфрич Корректор Н. Григорук

Заказ 7009/18 Тираж 662 Подписное

5НИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП Патент> г. Ужгород, ул. Проектная, 4