-разрядное счетно-сдвиговое устройство

Иллюстрации

Показать всеРеферат

ЬСЕСО1с.зифЛ

А;

Ррт ъйтнв-тех й! 14есклчт рл767842

0 -п.,и-с A и и е

Союз Советских

Социалистнческ их

Республик

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 070176 (21) 2312029/18-24 с присоедикеиием заявки Йо (23) Приоритет (5!)М. Кл.з

G 11 С 19/00

Н 03 К 23/02

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 3009,80 Бюллетень Мо36 (53) УДК 681. 325 (088. 8) Дата опубликования описания 3009.80 (72) Авторы изобретения

В.A.ОРехов,A.Ô.Герцовский и И.П.Врызгалов (71 ) За яв и тель (54) 11-РАЗРЯДНОЕ СЧЕТНО-СДВИГОВОЕ УСТРОЙСТВО

/ I, Изобретение относится к вычислительной технике и может быть использовано в автоматике, телемеханике, ядерном приборостроении;

Известны и -разрядные счетно-сдвиговые устройства, применяемые в вычислительной технике (Щ2).

В известных устройствах для осуществления операции рода работы: счета и сдвига — логические элементы, переключаемые при изменении режима работы устройства, обслуживают (коммутируют) отдельно каждый триггер (разряд) счетно-сдвигового устройства.

Из известных П --разрядных счетносдвиговых устройств наиболее близким по технической сущности к изобретению является устройство, представляющее собой комбинированный регистр счета и сдвига двоичных ° чисел (2).

Недостаток этого устройства заключается в том, что в нем логические элементы, переключаемые при изменении режима работы устройства, обслуживают каждый триггер (разряд регистра); это усложняет устройство и снижает его надежность.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что и -разрядное счетно-сдвиговое устройство, содержащее n/2 счетных блоков, причем каждый счетный блок имеет двухразрядный регистр, первый счетный блок содержит, кроме того, элемент И- НЕ и элемент НЕ, а каждый 1-й счетный блок (g =2,..., n/2) — два элемента 2И-ИЛИ-НЕ, 1 причем вход установки в нуль каждого двухразрядного регистра подключен к управляющей шине обнуления

15 устройства, управляющая шина счета устройства — к первому входу элемента И-HE первого счетного блока и первым входам первых групп входов первого и второго элементов 2И-ИНИ20 НЕ каждого j --го счетного блока устрой ства, первые входы вторых групп входов которых соединены с управляющей .шиной разрешения сдвига устройства, тактовый вход устройства через элемент НЕ подключен ко входу синхронизации двухразрядного регистра, nepaoro счетного блока, а также соединен со вторым входом второй группы входов второго элемента 2И-ИЛИ-НЕ

З0 каждого j --го счетного блока, выход

767842

Вход

5О 0

5 бО б

65 8 которого связан со входом синхронизации двухразрядного регистра того же блока, второй вход второй группы входов первого элемента 2ИИЛИ-НЕ и второй вход первой группы входов второго элемента 2И-ИЛИНЕ g-го счетного блока соединены с выходом двухразрядного регистра (j-1) -ro счетного блока, а второй вход первой группы входов первого элемента 2И-ИЛИ-НЕ 1-го счетного блока подключен-к выходу двухразрядного регистра j --го счетного блока, информационный вход которого подсоединен к выходу первого элемента

2И-ИЛИ-НЕ -го счетного блока, выход элемента И-НЕ первого счетного блока соединен с информационным входом двухразрядного регистра пер" вого счетного блока, выход двухразрядного регистра первого счетного блока — со вторым входом элемента

И-НЕ первого счетного блока.

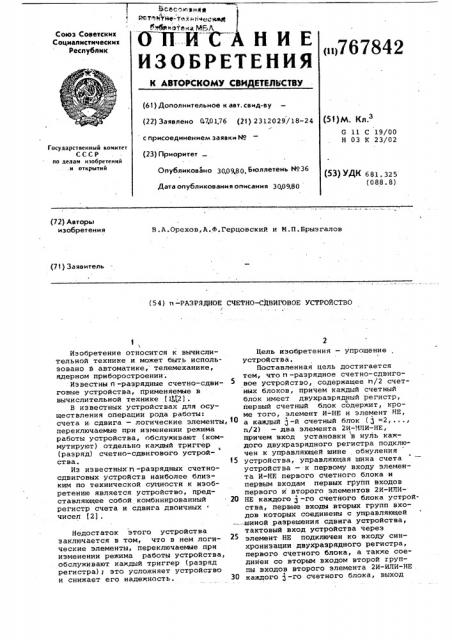

На фиг. 1 представлена блок-схема и -разрядного счетно-сдвигового устройства; на фиг.2 и на фиг.3 показаны варианты построения двухразрядного регистра íà T -К-триггерах и

Р-триггерах соответственно.на фиг.4 представлена схема преобразователя кода.

П-разрядное счетно-сдвиговое устройство содержит и/2 счетных блоков 1, каждый из которых содержит двухразрядный регистр 2 (регистр сдвига). Первый счетный блок 1 содержит, кроме того, элемент И-НЕ 3 и элемент НЕ 4, каждый 3 -й счетный блок 1 (3= 2,..., n/2) — элементы 2ИИЛИ-НЕ 5 и б. Управляющая шина 7 обнуления подключена ко входу установки в нуль каждого двухразряднаго регистра 2. Управляющая шина 8 счета подключена к первым входам первых групп входов элементов 2И-ИЛИ-HE

5 и б и первому входу элемента И-HE

3, управляющая шина 9 разрешена сдвига — к первым входам вторых групп входов элементов 2И-ИЛИ-НЕ 5 и 6.

Тактовый вход 10 устройства через элемент НЕ 4 подключен ко входу синхронизации регистра 2 первого счетного блока 1, а также соединен со вторым входом группы входов элемента

2И-ИЛИ-НЕ 6 g-ro счетного блока 1.

Выход регистра 2 каждого g -го счетного блока 1 соединен со вторым входом второй группы входов элемента

2И-ИЛИ-HE б (+1)-ro счетного блока 1 и со вторым входом первой группы входов элемента ?И-ИЛИ-НЕ 5 g-ro счетного блока 1, выход регистра 2 первого счетного блока — с входом элемента 2И-ИЛИ-НЕ 6 и вторым входом второй группы входов элемента 2ИИЛИ-НЕ 5 второго счетного блока 1, а также со вторым входом элемента

И-НЕ 3 первого счетного блока 1.

Регистр каждого счетного блока

1 может быть выполнен с помощью двух Ê -триггеров 11 и 12 и элемента НЕ 13 (фиг. 2) или с помощью двух D -триггеров 14 и 15 (фиг.3) °

Устройство работает следующим

5 образом.

На вход 10 разрядного счетносдвигового устройства поступают импульсы для счета или тактовые импульсы сдвига. На управляющие шины 9 или

1О 6 подается сигнал разрешения рода работы устройства: сдвиг или счет соответственно.

При подаче разрешающего сигнала на управляющую шину 9 тактовые им1Я пульсы через соответствующие элементы 2И-ИЧИ-НЕ б поступают одновременно на С -входы двухразрядных регистров

2 g --x счетных блоков 1, а на Ъ-входы этих регистров через элементы

2О 2И-ИЛИ-НЕ 5 проходят сигналы с двухразрядных регистров 2 (g-1)-х счетных блоков 1.

При подаче разрешающего потенциала на управляющую шину 8 импульсы поступают только на (..-вход двухраз рядного регистра 2 первого счетного блока 1 (через элемент НЕ 4) . При этом С -входы двухразрядного регистра

2 каждого 1-го счетного блока l через свой элемент 2И-ИЛИ-НЕ 6 подЗО ключаются к восходу двухразрядного регистра 2 (j -1) -го счетного блока.l.

Ь-вход j --го счетного блока 1 через свой элемент 2И-ИЛИ-НЕ 5 соединяется со своим выходом.

35 Таким образом, при подаче разрйшающего сигнала на управляющую шину 9 происходит сдвиг записанного числа, как в обычных сдвиговых регистрах, а при подаче разрешающего сиг40 нала на управляющую шину 8 — счет поступивших на вход устройства импульсов. Счет осуществляется в двоично-четвертичной системе счисления в коде, который приведен в табл. 1;

Т а б л и ц а 1

767842

Продолжение табл. 1

Формула изобретения

12 триггера

0 1

2 0 1

3 g 1

4 1 0

5 1 0

6 1 0

7 1 0

8 0 1

55

9 1 0 1 1

10 1 1 1 1

0 1 1 1

0 0 0 1

13 1 0 0 1 10

l4 1 1 0 1

15 0 .1 0 1

I5

Работа устройства в данном коде отличается лучшей помехоустойчивостью, так как уровень помех в два раза ниже, чем при работе счетчика в обычном коде.

При необходимости перевести полученный код в обычный двоичный на выходе данного устройства ставится преобразователь кода, например такой, какой изображен на фиг. 4. При выводе числа из устройства через данный пре- 25 образователь из последнего выходят числа в позиционном двоичном коде, т.е. в коде обычного двоичного счетчика. В табл.2 приведены числа, состоящие из всех возможных комбинаций по группам: 00,01,11,10, которые объясняют выход числа из устройства с данным преобразователем.

Т а блица 2

Такт Выход щ-ур Выход Я Выход триггера ТТ

Данное устройство выгодно отличается от известных более простыми связями, меньшим количеством конструктивных узлов, меньшим потреблением 60 мощности.

При построении счетно-сдвигового устройства по данному варианту затраты электронного оборудования на логические элементы, управляющие режимом работы, сокращаются не менее чем на

50Ъ, следовательно, возрастает на:дежность и экономичность всего устройства. и -разрядное счетно-сдвиговое устройство, содержацее n/2 счетных блоков, причем каждый счетный блок содержит двухразрядный регистр, первый счетный блок содержит, кроме того, элемент И-НЕ и элемент НЕ, а каждый

3-й счетный блок (1=2,..., и/2) — два элемента 2И-ИЛИ-НЕ, причем вход установки в нуль каждого двухразрядного регистра подключен к управляюц1ей шине обнуления устройства, управляющая шина счета устройства подключена к первому входу элемента И-НЕ первого счетного блока и к первым входам первых групп входов первого и второго элементов 2И-ИЛИ-HE каждого g --ro счетного блока устройства, первые входы вторых групп входов которых соединены с управляющей шиной разрешения сдвига устройства, тактовый вход устройства через элемент.HE подключен ко входу синхронизации двухразрядного регистра первого счетного блока, а также соединен со вторым входом второй группы входов второго элемента 2И-ИЛИ-НЕ каждого -го счетного блока, выход которого соединен со входом синхронизации двухраэрядного регистра того же блока, о т л ич а ю щ е е с я тем, что, с целью упрощения устройства, второй вход второй группы входов первого элемента

2И-ИЛИ-НЕ и второй вход первой группы входов второго элемента 2И-ИЛИ-HE

„ -го счетного блока соединены с выходом двухразрядного регистра (j -1) -го счетного блока, а второй вход первой группы входов первого элемента 2И-ИЛИ-НЕ -го счетного блока подключен к выходу двухразрядного реги"тра 3 -го счетного блока, информационный вход которого подключен к выходу первого элемента 2ИИЛИ-НЕ g -ro счетного блока, выход элемента И-НЕ первого счетного блока соединен с иноормационным входом двухразрядного регистра первого счетного блока, выход двухразрядного регистра первого счетного блока соединен со вторым входом элемента

И-НЕ первого счетного блока.

Источники информации, принятые во внимание при экспертизе

1, Патент Великобритании 1264181, кл. Л 4 А, 1971.

2. Алексеенко А.Г. Основы микросхемотехники. М., Сов.радио, 1971, с.186 (прототип) .