Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛВСТВУ

<н767844 (61) Дбполнительиое к авт. свид-ву (22) Заявлено 0601 .78 (21) 2567983/18-24 (511М. К„.3 с присоединением заявки ¹

G 11 С 27/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 3p р 9 8 р0, Бюллетень ¹ 36 (5З) УДК 681. 327.. 66 (088. 8) Дата опубликования описания ЗЦ0980

1 (72) Авторы изобретения

Ю.B.Òèìêèí и Е.В,Финогенова (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к электроизмерительной и вычислительной технике и может применяться в устройствах автоматики и аналого-цифровых вычислительных машинах. 5

В частности, изобретение может быть использовано в быстродействующих аналого-цифровых т(реобразователях (АЦП) для расширения их динамического диапазона, уменьшения динамической погрешности AOJI при квантовании сигналов с широким спектром, а также в других устройствах,,использующих выборку и хранение знаЧений аналоговых сигналов с временем за- !5 поминания и хранения порядка нескольких сотен наносекунд.

Известны аналоговые запоминающие устройства (1),(2), содержащие операционный усилитель, накопительный 20 элемент, электронный ключ, буферный усилитель, шину управления. В режиме запоминания устройства охватываются отрицательной обратной связью.

В схеме аналога (1) в режиме запо-25 минания транзистор второго каскада усилителя может заходить в область насыщения. Это приводит к увеличению времени запоминания. Кроме того„ его динамическая входная емкость шунтиру-30

2 ет нагрузочный резистор дифференциального каскада, что также приводит к снижению быстродействия за счет сужения полосы пропускания.

При переходе к режиму хранения ,накопительный конденсатор заряжается продиффереицированным коммутационным сигналом, прошедшим через емкость база-коллектор транзистора второго каскада и прямо включенный диод, что снижает точность устройства.

Схема аналога (2) имеет недостаточно высокое быстродействие, так как входной дифференциальный усилитель с высоким внутренним сопротивлением, что ограничивает зарядный ток накопительного конденсатора. Высокое внутреннее сопротивление обусловлено необходимостью задания на его выход в режиме хранения выходного напряжения через регулятор уровня и электронный ключ (с целью сохранения заряда конденсатора при конечном сопротивлении зарядного ключа в разомкнутом состоянии).

Кроме того, в режиме хранения при большой скорости измерения входного сигнала возникают ошибки, снижающие точность устройства, вызванные прохождением изменений сигнала с

767844 выхода дифференциального усилителя через проходную емкость зарядного ключа на накопительный конденсатор.

Наиболее близким к предлагаемому из известных устройств по технической сущности является аналоговое запоминающее устройство (3), содержащее корректирующую цепь, выполненную на. резисторе и конденсаторе, операционный усилитель, эмиттерный повторитель, ключ на комплементарных

МОП-транзисторах, истоковый повторитель, используемый в качестве накопительного элемента конденсатор, одна из обкладок которого соединена через резистор с шиной питания, пассивные элементы, к общей точке кото- !5 рых подключен выход ключа на МОПтранзисторе.

Быстродействие устройства достигается.тем, что в режиме хранения информации, когда ключ разомкнут, 20 ключ замыкают через резистор цепь отрицательной обратной связи операционного усилителя и предохраняет его каскады.от насыщения. Входной сигнал подается через резисторы одновременно на инвертируюций и неинвертирующий входы операционного усилителя. При таком способе напряжение на выходе усилителя к следующему моменту запоминания (выборки) равно входному сигналу.

Точность запоминания устройства обеспечинается тем, что в режиме запоминания устройство охвачено отри„цательной обратной связью через операционный усилитель с высоким коэффициентом усиления.

Высокое входное сопротивление истокового повторителя, а также высокое сопротивление ключа в разомкнутом состоянии позволяют получить малую 40 скорость разряда накопительного конденсатора, т.е. хорошую точность хранения информации.

Однако этот метод построения имеет недостатки. Так, при работе с 45 сигналами широкого спектра приращения входного сигнала они будут проходить на накопительный конденсатор через паразитную емкость стокисток ключа и емкость монтажа. 50

Этот недостаток особенно заметен при малых значениях емкости накопительного конденсатора, т.е ° в аналоговых запоминающих устройствах высокого быстродействия.

Наличие двух .фаэосдвигающих цепочек в прототипе, с одной стороны, улучшает динамическую устойчивость системы, но в то же время сужает полосу пропускания устройства, так как граничные частоты этих цепочек, 60 должны быть разнесены во избежание наложения фазовых сдвигов. При этом параметры цепочки, состоящей из резистора и конденсатора, должны удовлетворять также условию динамичес- 5 кой устойчивости устройства в режиме, когда операционный усилитель охвачен отрицательной обратной, связью через замкнутый ключ, что требует достаточно большой емкости конденсатора. Ввиду того, что эта цепочка остается в контуре обратной связи также и в режиме запоминания, постоянная времени цепочки, образованной внутренним сопротивлением ключа и накопительного конденсатора, должна быть существенно больше постоянной времени, образованной конденсатором и эквивалентным сопротивлением резисторов цепи инвертирующего входа операционного усилителя.

Это приводит к значительному сужению полосы пропускания устройства и уменьшению его быстродействия.

Если операционный усилитель не охватывает через ключ отрицательной обратной связью, как это осуществляется в прототипе, то можно исключить корректирующую цепочку и существенно уменьшить постоянную времени цепи заряда накопительного конденсатора, т.е. существенно повысить быстродействие устройства. При этом необходимо предпринять меры против насыщения каскадов усилителя.

Целью изобретения является увеличение быстродействия аналогового запоминающего устройства.

Это достигается тем, что в аналогпаое запоминающее устройство, содержащее дифференциальный усилитель, один иэ нходов которого соединен с входом устройства, выход дифференциального усилителя подключен к входу первого буфферного усидителя, выход которого соединен с одним из входов первого ключа, другой вход первого ключа подсоединен к первой шине управления, выход первого ключа соединен с входом второго буфферного усилителя и накопительным элементом, например, одной из обкладок конденсатора, другая обкладка которого через пассивный элемент соединена с шиной нулевого потенциала, выход второго буфферного усилителя соединен с выходом устройства и другим входом дифференциального усилителя, нторой ключ и вторую шину управления, введены ограничитель напряжения и шины отрицательного и положительного напряжения ограничения, подключенные к соответствующим входам ограничителя напряжения, выход которого подсоединен к входу первого буферного усилителя и одному их входов второго ключа, другбй вход второго ключа соединен с второй шиной управления, выход второго ключа соединен с шиной нулевого потенциала, причем дифференциальный усилитель содержит усилительный каскад, выполненный на четырех и -p-й-.транзисторах, включенных по каскадной схеме, трех ге767844 нераторах тока, первый из которых выполнен на Р -n-p-транзисторе и резисторе, а второй и трети — соответственно íà и -p-и-транзисторе и резисторе, стабилитрон и нагрузочный элемент, например резистор, через который коллектор первого р --р-и и -транзистора усилительного каскада соединен с пОложительной шиной питания, коллектор второго tl --p-Птранзистора усилительного каскада соединен с коллектором р --0-р-транзис- 0 тора первого генератора тока и через стабилитрон с выходом дифференциального усилителя и коллектором п -р-hтранзистора второго генератора тока, коллектор п -р-и-транзистора третьего генератора тока соединен с эмиттерами третьего и четвертого и -p-отранзисторов усилительного каскада, базы которых соединены соответственно с входами дифференциального усилителя, эмиттеры транзисторов второго и третьего генераторов тока соединены соответственно через резисторы с отрицательной шиной питания, а эмиттер транзистора первого генератора тока соединен через резистор с положительной шиной питания.

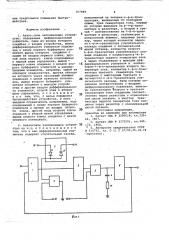

На фиг. 1 приведена функциональная схема предлагаемого аналогового запоминающего устройства; на фиг;2 электрическая схема дифференциального усилителя °

Устройство содержит дифференциальный усилитель 1, ключи 2,3, накопительный элемент, например конденсатор

4 буферные усилители 5,6 ограничитель напряжения 7, выполненный на диодах

8,9 шины 10,11 отрицательного и.положительного напряжения ограничения, шины 12,13 управления, пассивный элемент 14. 40

Дифференциальный усилитель содержит усиленный каскад 15, выполненный на четырех Р -p-h-транзисторах 16-19, три триггера тока 20,21,22, первый иэ которых выполнен на р -П-р-транзис- 4S торе 23 и резисторе ?4, стабилитрон

25, резистор 26; второй и третий генераторы тока выполнены соответственно на и --р-и-транзисторе 27 и резисторе

28 и и -р-П-транзисторе 29 и резисторе

30; 31 и 32 — входы усилителя.

Устройство работает следующим образом.

Входной сигнал, подлежащий запоминанию, подается на клемму 31, в режиме запоминания ключ 2 открыт, а ключ 3 закрыт. Цепь обратной связи замыкается через буфферный усилитель

5, ключ 2, буфферный усилитель 6, клемму 32.

Важным для получения высокого быс- ф() тродействия является применение в устройстве однокаскадного дифференциального усилителя 1 с токовым выходом, линейный режим, а следовательно,. быстродействие, которое в момент пере- Я хода из режима хранения в режим запОминания до замыкания обратной связи поддерживается благодаря введению ограничителя на диодах 8,9, а исключение насыщения дифференциального усилителя

1 в режиме хранения информации осуществляется введением ключа 3.

Для согласования дифференциального усилителя с последующими каскадами служат стабилитрон 25 и генератор тока 21.

Быстродействие устройства зависит от быстродействия всех его каскадов, а наиболее инерционным звеном здесь является уилитель 1, поэтому быстродействие усилителя 1 в первую очередь определяет быстродействие всего устройства.

Благодаря каскадному построению дифференциального усилителя 1 осуществляется удачная развязка входных и выходных цепей усилителя,-что увеличивает его быстродействие.

Наличие динамической нагрузки в выходном каскаде усилителя также повышает быстродействие усилителя.

Скорость нарастания сигнала на выходе усилителя 1 равна 4=3 )С, где 3; половина тока генератора тока 22; суммарная емкость на выходе усилителя 1.

1(оэффициент усиления усилителя благодаря динамической нагрузке достаточно большой К=1000, что обеспечивает высокую точность запоминания.

Высокая точность устройства в режиме хранения обеспечивается благодаря включению ключа 3, так как при т этом исключается погрешность,вызываемая прохождением фронта входного сигнала через паразитные емкости ключа 2.

В быстродействующих аналоговых запоминающих устройствах время хранения незначительно — сотни наносекунд, поэтому утечкой заряда конденсатора

4 через закрытый ключ 2 можно пренебреч.

Технико-экономический эффект предлагаемого устройства заключается в с ; щественном повышении быстродействия и точности, обусловленном отсутстви-ем прохождения сигнала на конденсатор 4 в режине хранения.

Это открывает возмояность построения аналоговых запоминающих устройств наносекундного диапазона, работающих в условиях меняющегося с большой скоростью сигнала.

Построение дифференциального усилителя по схеме с токовым выходом и динамическими нагрузками в виде генератора тока позволяет построить усилитель по однокаскадной схеме с малыми задержками распространения сигнала, что создает дополнитель767844 ные предпосылки повышения быстродействия.

Формула изобретения

1. Анало.овсе запоминающее устройство, содержащее дифференциальный усйлитель; один из входов которого соединен с входом устройства, выход дйфференциального усилителя подключен к входу первого буфферного усилйтеля выход которого соединен с одним из входов первого ключа, другой вход первого ключа подсоединен к первой шине управления, выход -.

-первого ключа соединен с входом второго буфферного усилителя и накопи " " тельным элементом, например» одной из обкладок конденсатора, другая обклад- ка которого через пассивный элемент соединена с шиной нулевого потенциала, выход второго буферного уси лителя соединен с выходом устрой- ства и другим входом дифференциального усилителя, второй ключ и вторую шину управления, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройства, в него введены ограничитель напряжения; подсоединенный к входу первого буферного усилителя и одному иэ входов второго ключа; другой вход второго ключа соединен с второй шиной управления, выход: второго ключа соединен с шиной — †-нулевого потенциала.

Р

2. Аналоговое запоминающее устройство по п.l, о т л и ч а ю щ е е с я тем, что в нем дифференциальный усилитель содержит усилительный каскад, выполненный на четырех р-р-h-транзисторах, включенных по каскадной схеме, трех генераторах тока, первый из которых выполнен на р-о-р-транзисторе и резисторе, а второй и третий — собтветственно на и-р-и-транзисторе и резисторе, стабилитрон и нагрузочный элемент, например резистор, через который коллектор первого h -р-П-транзистора усилительного каскада соединен с положительной шиной питания, коллектор второго и -p-h-транзистора усилительного каскада соединен с коллектором p --n-ртранзистора первого генератора тока и через стабилитрон с выходом диф15 ференциального усилителя и коллектором h-p-0-транзистора второго генератора тока, коллектор h --р-h-транзистора третьего генератора тока соединен с эмиттерами третьего и

20 ÷åòâåðòoãî и -р-h-транзисторов усилительного каскада, базы которых соединены соответственно с входами дифференциального усилителя, эмиттеры транзисторов второго и третьего генераторов тока соединены соответ25 ственно через резисторы с отрицательной шиной питания, а эмиттер тран- зистора первого генератора тока соединен через резистор с положительной шиной питания.

ЗО Источники информации, принятые во внимание при экспертизе

1. Патент США Р 3309618, кл.330 .

69, 1967.. . 2. Патент США Р 3375501, кл.340.

35 173, 1968.

3. Авторское свидетельство СССР

Р 510752, кл. G 11 С 27/00» 25. 10. 74 (прототип);

76i7844 (Ðèã. 2

Составителв A.Âîðoíèé

Редактор Е.Караулова Техред А. Цуепанская Корректор Г.Решетник

Заказ 72ll/48 Тираж 662 Подписное

ВНЛИПИ Государственного комитета СССР по делам изобретений и открытий

113035, 53ссква, а-35, РаЯУискак каб., 31. 4/5

Филиал ППП Патент г. Ужгород, ул.Проектная,4