Устройство для выделения синхросигнала

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<л767994

Ф г гг

К АВТОРСКОМУ -СВЫДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 11. 09. 78 (21) 2662953/18-09 с присоединением заявим ¹ (23) Приоритет

Опубликовано 3009.80, Бюллетень ¹ 36

Дата опубликования описания p21p8p (51)М. Кл, .

H L 7/08

Государственный комитет

СССР по делам изобретений и открытий (531 УДК 621 ° 394 ° .662(088.8) (72) Авторы изобретения

Ф. А. Хараев, В..Ф. Лещенко, Л. К. Биглов, И. И. Бриденко и A. В. Бормисов

Специальное конструкторское бюро "Трансавтоматика"

Кабардино-Балхарского транспортного управления (71) За яв и тель (54) УСТРОЙСТВО ВЫДЕЛЕНИЯ СИНХРОСИГНАЛА

Изобретение относится к устройствам передачи данных и может использоваться для фазового пуска аппаратуры при передаче двоичных последовательностей. 5

Известно устройство выделения синхросигналаг содержащее последовательно соединенные приемник и нако- питель, выходы разрядов которого через блок элементов И подключены к IO соответствующим входам селектора, при этом сигнальный вход приемника объединен с первым входом блока обработки сигнала $1) .

Однако точность выделения синхро сигнала известным устройством недостаточна.

Целью изобретения является повышение точности выделения синхросигнала. 20

Для этого в устройство выделения синхросигнала, содержащее последовательно соединенные приемник и накопитель, выходы разрядов которого через блок элементов И подключены к 25 соответствующим входам селектора, при этом сигнальный вход приемника объединен с первым входом блока обработки сигнала, введены последовательно соединенные блок суммирующих Щ

2 усилителей, вычитающий блок, дискриминатор и управляемый делитель частоты, при этом выход управляемого делителя частоты подключен к управляющему входу накопителя, выходы дополнительных разрядов которого подключены к соответствующим входам блока суммирующих усилителей, а выход селектора подключен к соответствующему входу дискриминатора и к второму входу блока обработки сигнала, к управляющему входу которого подключен дополнительный выход управляемого делителя частоты.

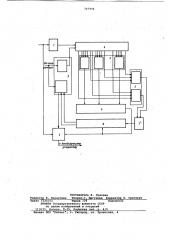

На чертеже изображена структурная электрическая схема предлагаемого устройства выделения синхросигнала..

Устройство выделения синхросигнала содержит приемник 1, накопитель 2, блок 3 элементов И, селектор 4, блок.

5 обработки сигналов, блок 6 суммирующих усилителей, вычитающий блок 7, дискриминатор 8, управляемый делитель 9 частоты.

Устройство выделения синхросигнала работает следующим образом.

В приемнике 1 осуществляется прием сигнала по огибающей. С выхода приемника 1 сигнал, имеющий один из двух уровней — высокий или низкий ("1"

767994 нли "0") — поступает на информационный вход накопителя 2, выполненного, например, в виде регистра сдвига. В накопителе 2 каждый символ сигнала синхронизации записывается в виде нескольких двоичных знаков "0" или "1"

Такая последовательность двоичных знаков "продвигается" по накопителю 2. При поступлении .сигнала синхронизации в момент его согласования с дискретным фильтром, образованным накопителем 2, блоком 3 и селектором

4, с выхода селектора 4 выдается им- пульс. Сигналы с выходов накопителя

2, смежных с выходами, соединенными с входами блока 3, поступают на входы блока 6 суммирующих усилителей.

Сигналы на выходе блока 6 характеризуют ошибку соответственно опережения или запаздывания момента выявления сигнала синхронизации, обусловленную действием помех, случайным рассогласованием по фазе между приходящим сигналом и сигналом тактовой частоты приемной части, а также не.стабильностью генераторов. Величина и направление ошибки определяются пу. тем вычисления разности сигналов с выходов блока б и вычитающего блока 7. В дискриминаторе 8 величина ошибки преобразуется в число импульсов, которые нужно добавить (или вычесть) в последовательность, поступающую на управляемый делитель 9.

Тактовые импульсы с управляемого делителя 9 поступают. на вход блока 5 обработки сигнала, в котором осуществляется задержка входного сигнала, и по сигналу селектора 4 — синхронный йрием полезных сигналов.

Использование предлагаемого устройства выделения синхросигнала в системах передачи коротких сообщений позволяет уменьшить время передачи одного сообщения, увеличить точность выделения синхросигнала и сократить энергетические и аппаратурные затраты на синхронизацию.

Формула изобретения!

6 устройство выделения синхросигнала, содержащее последовательно соеди ненные приемник и накопитель, выходы разрядов которого через блок элементов И подКюйьчены к соответствующим входам селектора, при этом сигнальный

15 вход приемника обьединен с первым вхо- дом блока обработки сигнала, о т л ич а ю щ е е с я тем, что, с целью повышения точности выделения синхро,сигнала,, введены последовательно соединенные блок суммирующих усилите- . лей, вычитающий блок, дискриминатор и управляемый делитель частоты, при этом выход управляемого делителя частоты подключен к управляющему входу накопителя, выходы дополнительных разрядов которого подключены к соответствующим входам блока суммирующих усилителей, а выход селектора подклю. вен к соответствующему входу дискриминатора и к второму входу блока обработки сигнала, к управляющему входу которого подключен дополнительный выход управляемого делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9,543183, кл. Н 04 L 7/08. 1973. чяототип).

767994 усщюиам/у

Составитель H. Грачева

Редакто Е. Ка а лова . Тех С ИИг нова Ко ект Н. Григорук

Заказ 7220/52 Тираж 72 Подписное

ВНИИПИ Государственного комитета СССР о делам изобретений и открытий

113035 Москва, Ж-35 Ра бшская наб. д. 4 5

Филиал ППП "Патент, г.. Ужгород, ул. Проектная, 4