Многоканальный цифровой фазовый демодулятор

Иллюстрации

Показать всеРеферат

оигзнал патентно-тех ничеснал б. блноте"а р

ОП ИС

ИЗОБРЕТЕН ИЯ

) 768001

Союз Советских

Социалистических

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.10.78 (21) 2674514/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М. К .

Н 04 L 27/22

Гооудвротвенный комитет

СССР (53) УДК 621.394..62 (088.8) Опубликовано 30.09 80. Бюллетень №36

Дата опубликования описания 05.10.80 во делам изобретений н открытий (72) Авторы изобретения

Е. Н. Мохов, Н. В. Мазуро и И. А. Оболонин (71) Заявитель

Новосибирский электротехнический институт связи (54) МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ ФАЗОВЫЙ ДЕМОДУЛЯТОР

Изобретение относится к электросвязи и может использоваться в многоканальных системах передачи данных с фазо- или частотно-модулированными несущими при синхронных между собой каналах.

Известен многоканальный цифровой фазовый демодулятор, содержащий в каждом канале последовательно соединенные полосовой фильтр, усилитель-органичитель и формирователь импульсов, к второму входу которого подключен первый выход блока задающих генераторов, и последовательно соединенные генератор тактовых импульсов и блок управления, второй вход и выход которого соединены соответственно с первым выходом блока задающих генераторов и первым входом формирователя выходного сигнала (1).

Однако известный демодулятор имеет недостаточную помехоустойчивость.

Цель изобретения — повышение помехоустойчивости.

Для этого в многоканальный цифровой фазовый демодулятор, ссодержащий в каждом канале последовательно соединенные полосовой фильтр, усилитель-ограничитель и формирователь импульсов, к второму входу которого подключен первый выход блока задающих генераторов, и последовательно соединенйые генератор тактовых импульсов и блок управления, второй вход и выход которого соединены соответственно с первым выходом блока задающих генераторов и первым входом формирователя выходного сигнала, введены основной и промежуточный блоки памяти, арифметический блок и измерительный счетчик, выход которого подключен к первому входу промежуточного блока памяти, второй вход которого соединен с первым входом основного блока памяти и первым дополнительным выходом блока управления, второй дополнительный выход которого подключен к первому входу арифметического блока, выходы которого соединены соответственно с вторым входом формирователя выходного сигнала и вторым входом основного блока памяти, выход которого подключен к второму входу арифмтического блока, третий вход которого сое динен с выходом промежуточного блока памяти, соответствующие входы которого соединены с выходами формирователей импульсов каждого канала, при этом второй выход блока задающих генераторов подключен к

768001 входу измерительного счетчика, а блок задающих генераторов содержит два генератора, регенератор и делитель частоты, вход которого соединен с выходом первого генератора и первым входом регенератора, к второму входу которого подключен выход второго генератора, причем выход делителя и выход регенератора являются выходами блока задающих генераторов.

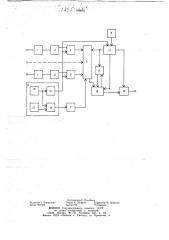

На чертеже представлена структурная электрическая схема предлагаемого демодулятора.

Демодулятор содержит в каждом канале полосовой фильтр 1, усилитель-ограничитель 2 и формирователь 3 импульсов, а также содержит блок 4 задающих генераторов, измерительный счетчик 5, основной блок 6 памяти, промежуточный блок 7 памяти, арифметический блок 8, генератор 9 тактовых импульсов, формирователь 10 выходного сигнала и блок 11 управления. Блок

4 содержит генераторы 12 и 13, делитель 14 частоты и регенератор 15.

Демодулятор работает следующим образом.

Сигнал каждого канала, имеющий частоты fq, подводится к входу канала и проходит через полосовой фильтр 1, который ослабляет действие помех и соседних каналов. Усилитель-ограничитель 2 устраняет изменения амплитуды сигнала и придает ему вид прямоугольного колебания . Формирователь 3 с помощью импульсов, получаемых от блока 4 задающих генераторов, создает на выходе импульсы, соответствующие одному из фронтов прямоугольного колебания и совпадающие по ширине и положению с импульсами от блока 4. Такие импульсы подаются на адресный вход промежуточного блока 7 памяти.

Измерительный счетчик 5 построен как двоичный счетчик, на вход которого поступают от задающего генератора импульсы частоты 2" f <. На — и;разрядном выходе измерительного счетчика 5 возникают кодовые числа, соответствующие текущим значениям фазы колебания с частотой fq. Кодовые числа подведены к входу записи промежуточного блока 7 памяти. При пос туплении импульсов на адресный вход происходит запись кодового числа в соответствующую строку блока памяти. Блок 7 памяти допускает одновременную запись кодового числа во все те строки, на адресных входах которых возникли импульсы. Кодовое число, записанное в строке, обновляется каждый раз с приходом импульса на адресный вход строки.

Считывание информации из промежуточного блока 7 памяти производится один раз в течение посылки по командам от блока ! 1 управления, поступающим на другой адресный вход. Обращение к строкам при этом производится поочередно с помощью вхо. ящих в блок 7 дешифратора и коммутатора строк. Скорость работы арифметического блока 8 обычно недостаточна для обработки всех каналов за короткое время, соответствующее средней части посылки. Поэтому перед началом вычислений информация из блока 7 памяти переносится при участии арифметического блока 8 в основной блок

6 памяти, откуда извлекается по мере проведения вычислений.

Обмен информацией между арифметическим блоком 8 и основным блоком 6 памяти производится по командам, поступающим с

<о выхода блока 11 управления. Эти команды определяют вид операций над кодовыми числами и порядок их выполнения. Блок 11 управления имеет в своем составе память, в которой хранится программа реализации алгоритмов обработки сигналов всех каналов, предусматривающая операции получения опорного колебания, принятия решения о передававшемся сигнале и декодирования относительности. Очередность обработки сигналов каналов также задается блоком управления. В процессе реализации алгоритмов информация о фазе принимаемого колебания в виде кодового числа поступает из блока 6 памяти в арифметический блок 8, а вычисляемая информация о фазе опорного колебания и об отклонении фазы принятого колебания от фазы опорного колебания направляется в блок 6 памяти с тем, чтобы быть использованной в следующей посылке. Для каждой из величин в основном блоке памяти имеется зона, число строк в которой соответствует числу каналов.

Решение о передававшемся символе (или символах при многократной манипуляции) принимается в арифметическом блоке 8. Символ с выхода арифметического блока 8 переносится в формирователь 10 по команде, и подаваемой на его стробирующий вход от блока !1. Чтобы сформировать синхронную последовательность символов на выходе формирователя 10 в блоке 11, наряду с последовательностью тактовых импульсов, используется последовательность импульсов с частотой в m N раз больше (N — число каналов; m — крагность манипуляции). Обе последовательности вырабатываются генератором 9 тактовых импульсов. Программа реализации алгоритмов привязана к этим импульсам. При многократной манипуляции часть символов должна поступить на формирователь 10 с задержкой. Для этого они направляются из арифметического блока 8 в основной блок 6 памяти, откуда возвращаются в арифметический блок 8 перед тем, как подать команду на формирователь 10.

Построение алгоритмов и приоритет в выполнении операций подчинены двум целям; во-первых, необходимости получения синхронных сигналов на выходе формирователя

10, и, во-вторых, необходимости считывания .. информации из промежуточного блока 7 па,мяти в средней части посылки.

Генератор 13 имеет частоту импульсов

2 !в. В простейшем случае эти импульсы

768001 используются также для подачи на стробирующие входы формирователя 3 и на вход блока 11. Если по каким-либо соображениям задающая частота 2 ад не может быть использована как задающая частота блока 11 управления, то используется второй генератор 12, который имеет частоту, не менее чем в два раза выше частоты генератора

13. Делитель 14 частоты снижает частоту вдвое, после чего она используется в формирователях импульсов сигнала и в блоке управления.

Частоты 2 fo от генератора 13 подается на регенератор 15, к стробирующему входу которого подведены импульсы от генератора

12. В результате импульсы частоты 2 f0 на выходе регенератора 15 имеют фронты, совпадающие с фронтами импульсов на выходе делителя 14. Регенерированные импульсы подаются на вход измерительного счетчика 5. Тем самым обеспечивается безошибочная совместная работа блоков устройства в частности становится возможным производить одновременно запись и считывание в промежуточном блоке 7 памяти.

Если в каналах используются неодинаковые частоты f0, то блоки 13, 15 и 5 выполняют, ся по числу используемых частот, а выход измерительного счетчика 5 подводится к соответствующим строкам промежуточного блока 7 памяти.

Формула изобретения

1. Многоканальный цифровой фазовый демодулятор, содержаший в каждом канале последовательно соединенные полосовой фильтр, усилитель-ограничитель и формирователь импульсов, к второму входу которого подключен первый выход блока задаюших генераторов, и последовательно соединенные генератор тактовых импульсов и блок управления, второй вход и выход которого соединены соответственно с первым выходом блока задаюших генераторов и первым входом формирователя выходного сигнала, отличающийся тем, чтп, с целью повышения помехоустойчивости, введены основной и промежуточный блоки памяти, арифметический блок и измерительный счетчик, выход которого подключен к первому входу промежуточного блока памяти, второй вход которого соединен с первым входом основщ ного блока памяти и первым дополнитель.ным выходом блока управления, второй дополнительный выход которого подключен к первому входу арифметического блока, выходы которого соединены соответственного с вторым входом формирователя выходного сигнала и вторым входом основного блока памяти, выход которого подключен к второму входу арифметического блока, третий вход которого соединен с выходом промежуточного блока памяти, соответствуюшие входы которого соединены с выходами фор мирователей импульсов каждого канала, при этом второй выход блока задающих генераторов подключен к входу измерительного счетчика.

2. Демодулятор по п. 1, отличающийся

2s тем, что, блок задающих генераторов содержит два генератора, регенератор и делитель частоты, вход которого соединен с выходом первого генератора и первым входом регенератора, к второму входу которого подключен выход второго генератора, причем выход делителя частоты и выход регенератора являются выходами блока задающих генераторов.

Источники информации, 3s принятые во внимание при экспертизе

1. Бухвинер В. Е. Дискретные схемы в фазовых системах радиосвязи. М., «Связь», 1969, с. 80 — 88, 126 †1 (прототип).

Редактор Е. Караулова

Заказ 7221/53

Составитель Е. Погиблов

Техред К. Шуфрич Корректор М. Шароши

Тираж 729 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4