Преобразователь двоично-десятичного кода "12222" в последовательный код

Иллюстрации

Показать всеРеферат

О П И-С- А Н -И Е

ИЗОБРЕТЕН ИЯ 769530

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное ас авт. свид-ву— (22) Заявлено 06.10.78 (21) 2671067/18-24 с присоединением заявки— (23) Приоритет— (43) Опубликовано 07.10.80. Бюллетень № 37 (45) Дата опубликования описания Оо.02.81 (51) М.Кл.з б 06 F 5/04

Государственный комитет по делам изобретений и открытий (53) УДК 681.325 (088.8) (72) Авторы изобретения

А. И. Журавлев и С. Б. Цакоев (71) Заявитель (54) ПPЕОБРАЗОВАТЕЛЬ

ДВОИЧНО-ДЕСЯТИЧНОГО КОДА «12222>

В IIOCJIEgl,OBATEJlbHbIA КОД

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении устройств для преобразования информации.

Известен преобразователь параллельно- S го двоично-десятичного кода в унитарный код (1), содержащий регистр хранения кода, элементы И, элементы ИЛИ и элементы задержки.

Недостатком этого преобразователя яв- 10 ляются невысокое быстродействие, а также большое число внешних связей, что усложняет управление преобразователем.

Наиболее близким по технической сущности к изобретению является преобразо- IS ватель двоично-десятичного кода 12222 в последовательный код (2), содержащий входной регистр, первую группу элементов

И, первый второй и третий элементы ИЛИ, группу элементов ИЛ И, группу элементов 20

НЕ и элементы задержки. Выход первого элемента И первой группы соединен с. первым входом первого элемента ИЛИ, выходы остальных элементов,И первой группы — со входами второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента ИЛИ. Единичные выходы разрядов входного регистра соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы ко- З0 торых соединены с выходами соответствующих элементов И группы, выходы элементов ИЛ И группы соединены с первыми входами соответствующих элементов

И первой группы и со входами третьего элемента,ИЛИ. Вторые входы элементов И первой группы соединены между собой и являются входом опроса устройства. Выход с-го (i = 1 —:4) элемента ИЛИ группы через -й элемент НЕ группы соединен с третьим входом (i+1)-го элемента И первой группы.

Недостаток этого преобразователя состоит в том, что для получения равномерного распределения импульсов в пачке выходного кода необходимо жестко фиксировать величину сдвига между импульсами опроса, что не позволяет произвольно изменять частоту. следования импульсов опроса.

Целью изобретения является повышение надежности преобразователя и обеспечение возможности равномерного распределения импульсов в пачке.

Эта цель достигается тем, что преобразователь двоично-десятичного кода 12222 в последовательный код, содержащий входной регистр, первую группу элементов И, первый, второй и третий элементы ИЛИ, группу элементов ИЛ И, группу элементов

76953Î

l0

НЕ, выход первого элемента И первой группы соединен с первым входом первого элемента ИЛИ, выходы остальных элементов И первой группы — со входами второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента ИЛИ, единичные выходы разрядов входного регистра соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И первой группы, выходы элементов NJIiN группы соединены с первыми входами соответствующих элементов И первой группы н со входами третьего элемента NJIiN, вторые входыэлементов И первой группы соединены между собой и являются входом опроса устройства, выход i-го (= 1 -:-4) элемента ИЛИ группы через -й элемент НЕ группы соединен с третьим входом (i+1)-го элемента

И первой группы, дополнительно содержит вторую группу элементов И, счетный триггер, единичный выход которого соединен е первыми входами элементов И второй группы. Второй вход -го элемента И второй группы соединен с выходом (i+1)-го элемента И первой группы, а выход i-го элемента И второй групы — с нулевым входом (i+1)-го разряда входного регистра. Вход счетного триггера соединен с выходом второго элемента ИЛИ. Выходы первого и третьего элементов:ИЛИ соответственно являются информационными и сигнальным выходами преобразователя.

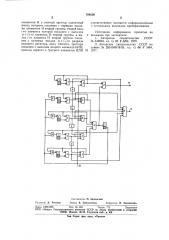

На чертеже представлена структурная схема преобразователя.

Он содержит входной регистр 1, состоящий из триггеров, группу элементов ИЛИ

2, первую группу элементов И 8, группу элементов .НЕ 4, первый и второй элементы ИЛ И 5 и б, счетный триггер 7, третий элемент ИЛ И 8 и вторую группу элементов

И 9.

Преобразователь работает следующим образом.

Если в триггер с весом «2 », соответствующий разряду входного регистра 1, записана «1», то при поступлении первого импульса опроса по входу .10 на второй вход элемента iN первой группы соответствующего разряда на выходе элемента

ИЛИ 5 формируется одиночный импульс, который поступает на информационный выход 11. При этом второй элемент,И 8 первой группы по третьему входу закрыт на время действия тактового импульса опроса сигналом с первого элемента НЕ 4 группы. Импульс, сформированный на выхо де первого элемента И 8 первой группы, обнуляет триггер первого разряда. Если этот триггер в исходном состоянии сброшен, а взведен следующий триггер с весом «2», то по первому тактовому импульсу срабатывает второй элемент И 8 первой группы.

При этом по заднему фронту тактового импульса срабатывает счетный триггер..Сигнал с единичного выхода триггера открывает по первому входу соответствующий элемент И 9 второй группы. Следующий тактовый импульс также проходит на выход элемента И 8 первой группы и через соответствующий элемент И 9 второй группы сбрасывает второй триггер входного регистра и по заднему фронту обнуляет счетный триггер, При этом элементы И 9 второй группы закрываются по первому входу. Таким образом, на выход элемента И 8 первой группы с весом «2» проходят два тактовых импульса, которые через элементы ИЛИ б и Б поступают на информационный выход 11 устройства. Опрос следующих элементов И 8 первой группы проводится аналогично.

Выходной код выдается в виде пачки импульсов, равномерно распределенных во времени, После опроса последнего элемента И 8 первой группы, когда входной регистр примет нулевые значения во всех разрядах, на выходе третьего элемента N JIM 8 фор м ируется сигнал < Конец преобразования», который поступает непосредственно на сйгнальный выход 12 преобразователя.

Таким образом, устройство позволяет получать на выходе последовательный код в виде пачки импульсов, равномерно распределенных во времени при любой произвольной частоте поступающих на вход «Мпульсов опроса.

Формула изобретения

Преобразователь двоичпо-десятичного кода Ii22i22 в последовательный код, содержащий входной регистр, первую группу элементов И, первый, второй и третий элементы ИЛИ, группу элементов ИЛИ, группу элементов HiE, выход первого элемента

И первой группы соединен с первым входом первого элемента ИЛИ, выходы остальных элементов И первой группы соединены со входами второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента ИЛИ, единичные выходы разрядов входного регистра соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И первой группы, выходы элементов ИЛ И группы соединены с первыми входами соответствующих элементов И первой группы и со входами третьего элемента ИЛИ, вторые входы элементов И первой группы соединены между собой и являются входом опроса преобразователя, выход г-го (i = 1 —:-4) элемента ИЛИ группы через -й элемент НЕ соединен с третьим входом (i+1)-ro элемента И первой группы, о т л ич а ю шийся тем, что, с целью повышения надежности, он содержит вторую группу

769530

Составитель М. Аршавскнй

Техред И. Заболотмова Корректор И. Осииовская

Редактор Л. Утехина

Заказ 1289/!295 Изд. № 484 Тираж 772 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений н открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Тня. Харьк. фил. пред. <Патент> элементов И и счетный триггер, единичный выход которого соединен с первыми входами элементов И второй группы, второй вход

/-го элемента которой соединен с выходом (i+1)-го элемента И первой группы, а вы- 5 ход i-ro элемента И второй группы соединен с нулевым входом (i+1) -го разряда входного регистра, вход счетного триггера соединен с выходом второго элемента ИЛИ, выходы первого и третьего элементов ИЛИ 10 соответственно являются информационным и сигнальным выходами преобразования.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 549803, кл. G 06 F 5/04, 1975.

2. Авторское свидетельство СССР по заявке Л 2551548/18- 24, кл. G 06 F 5%4, 1977.