Усилитель считывания

Иллюстрации

Показать всеРеферат

(»! 7696)7

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 28.12.78 (21) 2703059/18-24 с присоединением заявки № (51) М. К .

G 11C 7/00 (53) УДК 681.327.6 (088.8) по делам изобретений (43) Опубликовано 07.10.80. Бюллетень № 37 и открытий (45) Дата опубликования описания 07.10.80 (72) Авторы изобретения

В. Д. Мещанов и Н. А. Телицын (71) Заявитель (54) УС ИЛ ИТЕЛ Ь СЧ ИТЪ|ВАН ИЯ

ГосУдаРственный комитет (23) Приоригег

Изобретение относится к вычислительной технике и может быть использовано в интегральных полупроводниковых динамических ЗУ с произвольной выборкой информации.

Для восстановления информации в элементах памяти и ее считывания используется дифференциальный усилитель считывания (1, 2), ко входам которого подсоединены разрядные шины матрицы. Основу усилителя составляет триггер, нагрузочные и балансный транзисторы.

Недостатком таких усилителей является их низкая надежность.

Целью изобретения является повышение надежности усилителя считывания.

Эта цель достигается тем, что в предложенный усилитель введены транзисторы регенерации, конденсаторы и дополнительные шины управления. Сток первого транзистора регенерации подключен к первой входной шине, сток второго — ко второй входной шине, затворы транзисторов регенерации — к первой дополнительной шине управления, а истоки транзисторов регенерации через конденсаторы соединены со второй дополнительной шиной управления.

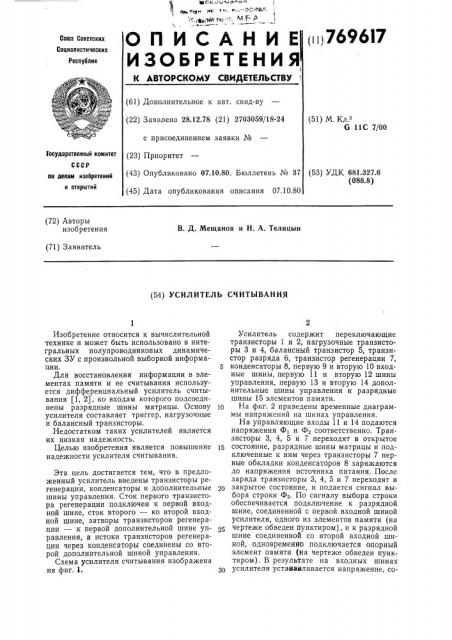

Схема усилителя считывания изображена на фиг. l.

Усилитель содержит переключающие транзисторы 1 и 2, нагрузочные транзисторы 3 и 4, балансный транзистор 5, транзистор разряда 6, транзистор регенерации 7, конденсаторы 8, первую 9 и вторую 10 входные шины, первую 11 и вторую 12 шины управления, первую 13 и вторую 14 дополнительные шины управления и разрядные шины 15 элементов памяти.

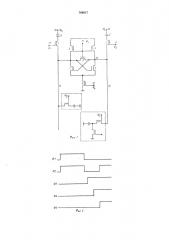

На фиг. 2 приведены временные диаграммы напряжений на шинах управления.

На управляющие входы 11 и 14 подаются напряжения Ф, и Ф2 соответственно. Транзисторы 3, 4, 5 и 7 переходят в открытое д состояние, разрядные шины матрицы и подключенные к ним через транзисторы 7 первые обкладки конденсаторов 8 заряжаются до напряжения источника питания. После заряда транзисторы 3, 4, 5 и 7 переходят в закрытое состояние, и подается сигнал выбора строки Фз. По сигналу выбора строки обеспечивается подключение к разрядной шине, соединенной с первой входной шиной усилителя, одного из элементов памяти (на чертеже обведен пунктиром), и к разрядной шине соединенной со второй входной шиной, одновременно подключается опорный элемент памяти (на чертеже обведен пунктиром) . В результате на входных шинах усилителя устанавливается напряжение, со769617 ответствующее хранившейся в элементе памяти информации, На время выбора строки отключается конденсатор 8 от разрядной шины. После установления напряжения на входных шинах усилителя на затвор транзистора 6 подается напряжение Ф» и через открывшийся транзистор 6 происходит разряд одного из плеч усилителя:в зависимости от хранившейся в элементе памяти информации. При >р этом если в элементе памяти хранился «0», будет разряжено левое плечо усилителя, если в элементе памяти хранилось «1»,— правое плечо усилителя.

После разряда одного из плеч дифферен- д циального усилителя для восстановления уровня логической единицы на дополнительные шины управления 14 и 15 подаются напряжения Фр и Ф соответственно.

Напряжение Ф создает на первой об- 20 кладке конденсатора 8 уровень напряжения, превосходящий уровень напряжения на разрядной шине. Избыточный заряд с первой обкладки конденсатора 8 через открытый транзистор 7 проходит на разрядную шину. 25

Заряд, пришедший на разрядную шину с еднничной информацией, восстанавливает уровень логической единицы, заряд, пришедший на второе (открытое) плечо усилителя, через открытые транзисторы 2 и 6 зО проходит на шину нулевого потенциала, не изменяя потенциала разрядной шины.

Формула изобретения

Усилитель считывания, содержащий два переключающих транзистора, сток первого из которых соединен с затвором второго переключающего транзистора и первой входной шиной, сток второго переключающего транзистора соединен с затвором первого переключающего транзистора и второй входной шиной, два нагрузочных транзистора, стоки которых объединены, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора и первой входной шиной, сток — с истоком второго нагрузочного транзистора и второй входной шиной, а затвор — с затворами нагрузочных транзисторов и первой шиной управления, разрядный транзистор, сток которого соединен с истоками переключающих транзисторов, исток — с шиной нулевого потенциала, а затвор — с второй шиной управления, отличающийся тем, что, с целью повышения надежности устройства, оно содержит транзисторы регенерации, конденсаторы и дополнительные шины управления, причем сток первого транзистора регенерации подключен к первой входной шине, сток второго — ко второй входной шине, затворы транзисторов регенерации — к первой дополнительной шине управления, истоки транзисторов регенерации через конденсаторы соединены с второй дополнительной шиной управления.

Источники информации, принятые во внимание при экспертизе

1. «Электроника», Re 13, 1973, с. 43 — 51.

2. «Электроника», Ne 4, 1976, с. 44 — 52 (прототип).