Ячейка памяти для регистра сдвига

Иллюстрации

Показать всеРеферат

Q n И С A H И E (ii 76963I

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Св1иалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 24.01.77 (21) 2446083, 18-24 с присоединением заявки ¹â€” (23) Приоритет (51) М. Кл.з

С 11С 19/28

Государственный комитет (43) Опубликовано 07.10.80. Бюллетень № 37 (53) УДК 681.327.67 (088.8) ло делам изобретений

Н CTKPblTHM (45) Дата опубликования описания 07.10.80 (72) Автор изобретения

П. А. Лебедев (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении различных запоминающих устройств, в частности регистров сдвига, проектируемых в интегральном исполнении.

Известны ячейки памяти для регистров сдвига, содержащие элементы памяти, соединенные последовательно (1) — (4) .

Однако они обладают ограниченной областью применения при построении программно-управляемых регистров.

Наиболее близкой к изобретению по технической сущности является ячейка памяти, содержащая элемент И, элемент ИЛИ и последовательно соединенные элементы памяти, входы управления которых подключены в тактовой шине (5).

Недостатками такой ячейки памяти являются ограниченная область применения и отсутствие возможности построения регистров сдвига, управляемых программно по количеству разрядов.

Целью изобретения является расширение области применения ячейки памяти за счет программного управления сю.

Это достигается тем, что в ячейку памяти для регистра сдвига, содержащую последовательно соединенные элементы памяти, входы управления которых подключены к тактовой шине, вход первого элемента памяти соединен с выходом первого элемента И, первый вход которого соединен с шиной управления, а выход последнего элеб мента памяти соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым выходом ячейки, введены второй элемент ИЛИ, второй и третий элементы И и инвертор, вход которого соеди10 нен в шиной управления, а выход — с первыми входами второго и третьего элементов

И, выходы которых соединены соответственно со вторым выходом ячейкп памяти и со вторым входом первого элемента ИЛИ, вто15 рой вход второго элемента И соединен с первым входом ячейки памяти н с первым входом второго элемента ИЛИ, второй вход которого соединен со вторым входом ячейки памяти и со вторым входом третьего элемента И, выход второго элемента ИЛИ соединен со вторым входом первого элемента И.

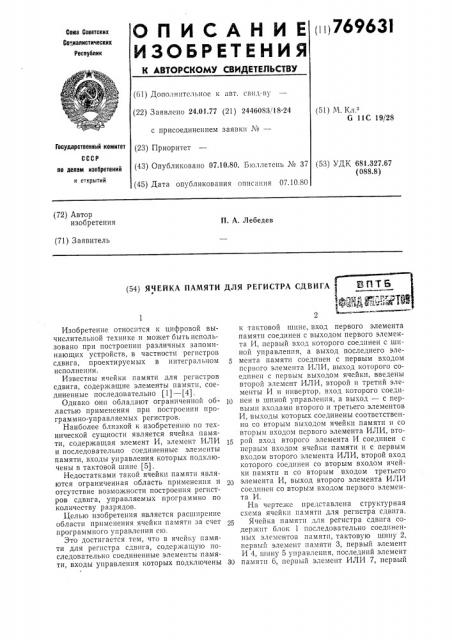

На чертеже представлена структурная схема ячейки памяти для регистра сдвига.

25 Ячейка памяти для регистра сдвига содержит блок 1 последовательно соединенных элементов памяти, тактовую шину 2, первьш элемент памяти 3, первьш элемент

И 4, шину 5 управления, последний элемент

30 памяти б, первый элемент ИЛИ 7, первьш выход 8 5Iчейки НВМНТН, второй

ИЛИ 9, второй элемент И 10, третий элемент И 11, инвертор 12, второй выход 13 ячейки памяти, первый вход 14 ячейки памяти, второй вход 15 ячейки памяти. ячейка памяти работает следующим образом.

По тактовой шине 2 поступают непрерывно тактовые сигналы Т (сдвигающне импульсы) на угравляющие входы последовательно соединенных элементов памяти блока 1. Информация, которая хранится в элементах памяти по каждому поступакпцсму такту Т передается (сдвигается) нз одного элемента памяти в последующий. Сигнал, который хранится в последнем элсilc! ITO памяти 6, по каждому такту передается через первый элемент ИЛИ 7 на первый выход 8 ячейки памяти. Сигнал, поступающий с выхода первой схемы IЛ - 1, по кaæдому такту записывается в первый элемент памяти 3 последовательно сс.: — дпнеипых элементов памяти блока 1 и хранится там один такт. Таким образом, поступивший сигнал на вход элемента памят,l 3 по каждому такту продвигается к выходу послсд0вательно соединенных элсмснтог. памяти блока 1 и далее через элемент ИЛИ 7 на первый выход 8 ячейки памяти.

Если информационный сигнал и HH;lc логической «1» поступает на второй вход 15 ячейки памяти, а на пшну 5 управления подается логическая «1», то информационный сигнал со второго входа 15 ячейки памяти через вторую схему ИЛИ 9 и первую схему И 4, на которой происходит совпадение .(вух логических «1», передастся па вход первого элемента памяти 3 после,lîвательно соединенных элементов памяти блока 1. Через определенное количество тактов Т информационный сигнал с последнего элемента памяти 6 через элемент ИЛИ

7 появится на первом выходе 8 ячейки r амяти. Следовательно, выходной сигнал ячейки памяти на выходе 8 будет иметь задержку информационного сигнала по отношению к сигналу на втором входе 15 ячейки памяти на количество тактов, которос определяется количеством последовательно соединенных элементов памяти блока 1.

В то же время логическая «1», поступающая по шине 5 управления, через инвсртор

12 запрещает прохождение информационного сигнала со второго входа 15 ячейки памяти через третий элемент И 11 на элс»ент

ИЛИ 7, поэтому входной сигнал со входа

15 через элемент И 11 не пройдет на Нервый выход 8 ячейки памяти. Логическая

«1» на шине 5 управления через инвертор

12 запрещает прохождение информационного сигнала, поступающего по первому входу

14 ячейки памяти, через второй элемент И

10 на второй выход 13 ячейки памяти.

Если по шине 5 управления поступает логический «0», то он запрещает на элементе

25 зо

Зэ

-15

И

6::

И 4 прохождение информаииот ных -игналов, поступающих с первого 14 и ьторого 15 входов, через элемент ИЛИ 9. Таким обраB0i информационные сигналы через элемент И 4 не пройдут на последовательно соединенные элементы памяти блока 1. В то же время логический «О», поступающий по шине 5 управления, через инвертор 12 логической «1» разрешает прохождение информационного сигнала со второго входа

15 через третий элсttснт И 11 и первый элемент IЛ IH 7 на первый вы. од 8 ячейки паltsIT!t oсз задержк на какое-либо число тактоь по отношению к «ходпому cltãíà-у.

Логический «О», поступаюпп|й по шине 5 управления, через ипвертор 12 разрешает прохождение информационного сигнала со входа 14 ячейки памяти через второй элемент И 10 на второй выход 13 ячейки памяти без задержки.

Таким 06paanki, по шипе 5»правления логическим сип-:алом мо;кно управлять я чей кОй памяти д, IH с, lBHГОВОГО реГHcTp а, -,. c, информационный сигнал, поступающий на вход 1 II;IH 13XO,I ) 5, !In>HHO IICpC,JBT!> HEI вы гэд 8 ячейки памяти задержанным на определе шос количество тактов на послс;loHBTcльпо соединенных элемсlITBi; памяти блока 1, если по !НННС 5 управле.t«ÿ поступает сигнал логической «1», или без задержки, сслп по шине 5 управления поступает сигнал логического «О». На второй выход 13 ячейки памяти информационный сигнал со входа 14 поступает без задержки, если по шине 5 управления поступас-. сигнал логического «0». Если же по Hl»: е

5 управления поступает сигнал логической

«1», то на второй выход 13 ячейки памяти информационный сигнал со входа 14 не пройдет.

Для построения управляемого регистра сдвига ячсйк t памяти должны соединяться

IIoc;IcjoBBTcëI H0: первый выход 8 предыдущей ячейки памяти подключается ко второму входу 15 последующей ячейки памяти, а второй выход 13 предыдущей ячейки памяти подключается к первому входу 14 последующей ячейки памяти.

Прн последовательном соединении п таки;х ячеек памяти получается регистр сдвига, управляемый программно извне по количеству разрядов, или регистр сдвига с перепрограммируемым числом разрядов.

Наиболее удачный «арпапт регистра сдвига получается при последовательном соединения и ячеек памя1и, при котором каж.laH ячейка памяти содержат 2 — последовательно соединенных элементов памяти, где

i — порядковый номер ячейки памяти от входа регистра. При этом код, поступающий по шинам 5 управления в ячей.сн памяти регистра. определяет разрядность регистра. Разрядность регистра находится в прямой зависимости от кода, поступающего

»о шинам 5 управления, В этом случае мак769631 симальная емкость регистра сдвига по числу разрядов будет тогда, когда на все и ячеек памяти по шинам 5 управления подается сигнал логической «1».

Максимальная емкость Ж„„кс по числу разрядов регистра сдвига будет определяться следующим выражением: и макс—

1=1 где n — число последовательно соединенных ячеек памяти в регистре сдвига;

i — порядковый номер ячейки памяти от входа регистра сдвига.

При таком соединении ячеек памяти на одном общем выходе регистра сдвига можно получить регистр сдвига на любое желаемое число разрядов в пределах Л „,„, т. е. универсальный регистр по числу разрядов за счет программного управления ячейками памяти. На одном общем выходе при одном общем входе регистра сдвига можно получить задержку входного сигнала на количество тактов, определяемое натуральным рядом чисел в пределах Л,„„.„ благодаря управлению ячейками памяти по шинам 5 управления.

Код, поступающий по шинам 5 управления на ячейки памяти, определяет заданное количество разрядов регистра сдвига. 3адаННОЕ ЧИСЛО раЗрядОВ рЕГИСтра СдВИГа Л1а определяется по следующему выражению: и

Л а = В,.21 —, i=1 где В, — сигнал, поступающий по шине 5 управления 1-той ячейки памяти, принимающий значение логического «О» или логической «1».

Таким образом, задавая определечные сигналы по шинам 5 управления в каждой последовательно соединенной ячейке памяти можно получить программно управляемый на всевозможное число разрядов регистр сдвига. Особенно это имеет большое значение при проектировании сдвиговых регистров в интегральном исполнении, когда регистр выполняется в одном корпусе на одном кристалле и изменению не подлежит.

Следовательно, изменить разрядность регистра сдвига можно только программно по шинам управления. В этом случае на одном

j0

З0

50 и том же выходе можно получить задержку информационного сигнала на всевозможное число разрядов, управляя программно, что значительно расширяет область применения ячейки памяти.

Формула изобретения

Ячейка памяти для регистра сдвига, содержащая последовательно соединенные элементы памяти, входы управления которых подключены к тактовой шине, вход первого элемента памяти соединен с выходом первого элемента И, первый вход которого соединен с шиной управления, а выход последнего элемента памяти соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым выходом ячейки, отличающаяся тем, что, с целью расширения области применения ячейки памяти за счет программного управления ею, в нее введены второй элемент

ИЛИ, второй и третий элементы И и инвертор, вход которого соединен с шиной управления, а выход — с первыми входамп второго и третьего элементов И, выходы которых соединены соответственно со вторым выходом ячейки памяти и со вторым входом первого элемента ИЛИ, второй вход второго элемента И соединен с первым входом ячейки памяти и с первым входом второго элемента ИЛИ, второй вход которого соединен со вторым входом ячейки памяти и со вторым входом третьего элемента И, выход второго элемента ИЛИ соединен со вторым входом первого элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ne 427387, кл. G 11C 19, 00, 1974.

2. Лвторское свидетельство СССР

Ма 432602, кл. G 11С 19/00, 1974.

3. Валиев К. Л. и др. Цифровые интегральные схемы на МДП-транзисторах.—

М.; Советское радио, 1971, с. 285.

4. Бузунов Ю. Л., Вавилов Е. Н. Принципы построения цифровых вычислительных машин. — К; Техника, 1972, с. 125.

5. Пухальскпй Г. И. Логическое проектирование цифровых устройств радиотехнических систем. — Л.; ЛГУ, 1976, с. 171, рис. 4.5.1 (прототип) .

Редактор Т. Клюкина

Составитель Г. Веременко

Техред А. Камышникова Корректор P. Беркович

Заказ 1998/11 Изд. № 496 Тираж 673 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4, 5

Типография, пр. Сапунова, 2