Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ („)769642 (61) Дополнительное к авт. свид-ву (22) Заявлено 26,01.79 (21) 2717999/18-24 (51)М. Кл 3

6 11 С 29/00 с присоединением заявки №вЂ”

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 0710,80, бюллетень ¹ 37

Дата опубликования описания 07,10,80 (53) УДК 681. 327 (088.8) (72) Авторы изобретения

Н.И. Вариес, Б.Е. Гласко и A.Ê. Култыгин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к области запоминающих устройств.

Известны устройства для контроля памяти (1Q, (2) .

Одно из известных устройств содержит схему пуска-останова, счетчик адресов, схему сравнения адреса и схему формирования кода чисел (11 .

Недостатком этого устройства является отсутствие контроля взаимного влияния информации, записанной в одном разряде всех адресов накопителя.

Из известных устройств наиболее близким техническим решением к изобретению является устройство для контроля памяти, содержащее формирователь адресных сигналов, схему сравнения адресов, блок пуска-останова, имитатор ввода конечного адреса, имитатор ввода начального адреса, формирователь числовых сигналов, схему сравнения чисел, блок управления, причем первый и второй входы схемы сравнения адресов соединены соответственно с выходами формирователя адресных сигналов и имитатора ввода конечного адреса, а выход с первыми входами блока управления и формирователя числовых сигналов, 2 второй вход которого подключен к первому выходу блока управления и первому входу формирователя адресных сигналов, второй вход которого соеди5 нен с выходом блока. пуска-останова, третий вход — с третьими входами блока управления и формирователя числовых сигналов, четвертый вход с выходом имитатора ввода начально10 го адреса, а пятый вход — со вторым входом блока управления, четвертый вход формирователя числовых сигналов соединен со входом устройства и первым входом, а выход — со вторым

15 входом схемы сравнения чисел, третий вход которой подключен ко второму выходу блока управления 21

Недостатками этого устройства является то, что в нем требуется руч20 ная установка каждой проверяемой комбинации чисел, а также невозможность выявления этапов проверки, на которых произошел сбой, и проверки на хранение информации, что снижает

25 функциональные возможности устройства и его быстродействие.

Целью изобретения является ïîâûшение быстродействия и расширение функциональных возможностей устройст30

769642

Поставленная цель достигается тем, что предложенное устройство содержит счетчик, триггер, дешифратор, два элемента И, элемент ИЛИ. Выход счетчика соединен со входом дешифратора, выход которого подключен ко входу триггера, выход и вход которого и входы двшифратора и счетчика соединены соответственно со вторым, третьим и четвертым входами и первым выходом блока управления, первый и третий выходы которого подключены к первым входам элементов И, вторые входы которых соединены с первым выходом схемы сравнения чисел, четвертый вход которой подключен к выходу первого элемента И, а второй выход — к первому входу элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и входом блока пускаостанова.

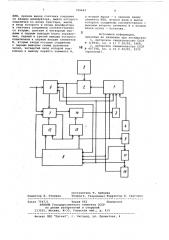

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит формирователь адресных сигналов 1, схему сравнения адресов 2, блок пуска-останова 3, имитатор ввода начального адреса

4, имитатор ввода конечного адреса

5, формирователь числовых сигналов

6, схему сравнения чисел 7, блок управления 8, счетчик 9, триггер 10, дешифратор 11, первый 12 и второй

13 элементы И и элемент ИЛИ 14.

Первый и второй входы схемы сравнения адресов 2 соединены соответственно с выходами формирователя и имитатора ввода конечного адреса 5, а выход — с первыми входами формирователя 6 и блока управления 8. Первый вход формирователя 1 подключен ко второму входу формирователя б, первому выходу блока управления 8, первому входу второго элемента И 13 и входу счетчика 9, второй вход — к выходу блока пуска-останова 3, третий вход — к третьим входам формирователя б и блока управления 8 и входу триггера 10, четвертый вход — к выходу имитатора ввода начального адреса 4, а пятый вход — ко второму входу блока управления 8 и выходу счетчика 9. Четвертый вход формирова теля 6 соединен со входом устройства и первым входом, а выход — со вторым входом схемы сравнения чисел

7, третий вход которой подключен ко второму выходу блока управления 8.

Выход счетчика 9 соединен с четвертым входом блока управления 8 и входом дешифратора 11, выход которого подключен ко входу триггера 10. Третий выход блока управления 8 соединен с первым входом элемента И 12.

Вторые входы элементов И 12 и 13 под ключены к первому выходу схемы сравнения чисел 7, четвертый вход которой соединен с выходом элемента И 12 а второй выход — с первым входом

В эти моменты блок управления 8 запрещает изменение состояния формирователя 1 . Таким образом, происходят 2 тактов записи ("долбление") по конечному адресу, в котором остался формирователь 1 после первоэлемента ИЛИ 14, второй вход которого соединен с выходом элемента И 13, а выход — co входом блока пуска-останова 3.

Устройство работает следующим образом.

Первоначально формирователь 1, триггер 10, счетчик 9 устанавливаются в нуль(цепи обнуления не показаны), В работе устройства различают два

1Р цикла работы.

В первом цикле при пуске устройства формирователь 1 производит перебор всех адресов, начиная от начального адреса, устанавливаемого имитатором ввода начального адреса 4, до конечного адреса, устанавливаемого имитатором ввода конечного адреса 5. Блок управления 8 формирует сигналы записи, поступающие в накопитель, по що всем адресам, а формирователь б формирует число "нуль". Таким образом, в первом цикле происходит запись "0" по всем адресам каждого разряда накопителя. При достижении формирователем

1 конечного адреса на выходе схемы сравнения адресов 2 формируется сигнал, по которому блок управления

8 формирует сигналы считывания и управляет работой формирователя 1, обеспечивая повторный перебор всех адресов накопителя. Считанные сигналы из накопителя поступают на вход устройства и на первый вход схемы сравнения чисел 7, а на второй вход сигналы с формирователя б. Результат сравнения поступает со схемы сравнения чисел 7 на второй управляющий вход элемента И 13, по первому управляющему входу которого поступает разрешение на контроль первого

4Р цикла, формируемое блоком управления 8. При наличии ошибки при считывании нулей по адресам накопителя элемент И 13 формирует сигнал, поступающий "а вход. элемента ИЛИ 14, 45 выходной сигнал которого, поступая на вход блока пуска-останова 3, прерывает работу устройства.

Если ошибки в считанной информации не было в первом цикле работы устройства, то начинается второй цикл работй устройства, называемый долблением .При этом блок управления 8 подготавливает формирователь

1 к реверсу и одновременно запускает п-разрядный счетчик 9. При этом триггер 10 по второму входу блока управления 8 разрешает формирование сигнала записи, который формируется в течение всех 2 тактов заполнения счетчика 9.

769642 го цикла работы. Формирователь 6, управляемый сигналом с выхода дешиф— ратора 11 и первого выхода блока управления 8, формирует число "1".

Таким образом, происходит "долбление" единицей по конечному адресу накопителя.

При достижении счетчиком 9 состояния, равного 2", на выходе дешифратора 11 формируется сигнал, который поступает на пятый вход формирователя 1 и разрешает изменение адреса 30 на "1" и одновременно меняет состояние триггера 10, сигнал с выхода которого, поступая на второй вход блока управления 8, совместно с сигналом, поступающим на четвертый вход блока 15 управления 8 со счетчика 9, разрешает формирование блоком управления 8 сигнала "считывание 1" по нулевому остоянию счетчика 9 и "считывание по конечному состоянию счетчика 9. ;щ

Таким образом, по сигналу "считывание 1" из (2 - 1) адреса, где N количество проверяемых адресов накопителя, из накопителя считывается

"нуль", который был .записан ранее в первом цикле, а по сигналу "считывание 2" происходит повторное считывание по тому же (2 - 1) адресу накоN пителя, т. е. повторное считывание происходит через некоторый промежуток времени, что позволяет проверить режим хранения информации в vaкопителе. В режиме "считывание 1" .теста "долбления" сигнал с выхода блока управления 8, поступая на первый управляющий вход элемента И 12 одновременно с сигналом ошибки, формируемым схемой сравнения чисел 7, запоминается схемой сравнения чисел

7 и не приводит к останову работы устройства, и только в режиме "счи- 40 тывание 2" сигнал со второго выхо-. да блока управления 8, поступая на третий вход схемы сравнения чисел 7, опрашивает ее. Если ранее была обнаружена ошибка при "считывании 1" 4 или при "считывании 2", то схема сравнения чисел 7 формирует сигнал, поступающий на первый управляющий вход элемента ИЛИ 14, который прекращает работу устройства. При этом индицируется неисправный адрес, разряд, исло "долбления", момент возникновения ошибки при долблении: при

"считывании 1" или после хранения информации "по считыванию 2" (цепи индикации не показаны).

Если останов при долблении по 2 адресу не произошел, то цикл работы устройства повторяется, только "долбление" единицей происходит по адресу (2 - 1), а считывание нуля из d0 (2" — 2) адреса и т.д. до нулевого (начального) адреса формирователя 1.

К этому моменту во всем накопителе по всем адресам записаны "1". При этом схема сравнения адресов 2 при 65 достижении нулевого (начального) адреса формирователем 1 вырабатывает сигнал сравнения на первом входе блока управления 8 и подготавливает формирователь к реверсу, и цикл работы повторяется, но при этом формирователь 6 формирует число "0" на запись при долблении нуля, так как схема сравнения адресов 2 изменяет его состояние.

Таким образом после "долбления"

"1" по всем адресам накопителя, начиная со старшего и до нулевого (начального), повторяется цикл "долбления" нулем также по всем адресам, начиная с нулевого (начального) до старшего адреса накопителя.

Технико-экономические преимущества описываемого устройства заключаются в том, что оно исключает ручную установку чисел накопителя при проверке взаимного влияния информации, записанной в одном разряде всех адресов, позволяет выявить этапы проверки, на которых произошел сбой, и индицировать неисправный адрес, а также обеспечивает проверку на хранение информации в памяти, что повышает быстродействие и расширяет функциональные возможности устройства.

Формула изобретения

Устройство для контроля памяти, содержащее формирователь адресных сигналов, схему сравнения адресов, блок пуска-останова, имитатор ввода конечного адреса, имитатор ввода начального адреса, формирователь числовых сигналов, схему сравнения чисел, блок управления, причем первый и второй входы схемы сравнения адресов соединены соответственно с выходами формирователя адресных сиг— налов и имитатора ввода конечного адреса, а выход — с первыми входами блока управления и формирователя числовых сигналов, второй вход которого подключен к первому выходу блока управления и первому входу формирователя адресных сигналов, второй вход которого соединен с выходом блока пуска-останова, третий вход — с третьими входами блока управления и формирователя числовых сигналов, четвертый вход — с выходом имитатора ввода начального адреса, а пятый вход со вторым входом блока управления, четвертый вход формирователя числовых сигналов соединен со входом устройства и первым входом, а выход — со вторым входом схемы сравнения чисел, третий вход которой подключен ко второму выходу блока управления, о т л ич а ю щ .е е с я тем, что, с целью повышения быстродействия устройства, оно содержит счетчик, триггер, дешифратор, два элемента И, элемент

769642!

Составитель Т. Зайцева

Редактор Л. Утехина Техред Е. Гаврилешко Корректор Н. Григорук

Заказ 7547/1 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r ужгород, ул. Проектная, 4

ИЛИ, причем выход счетчика соединен со входом дешифратора, выход которого подключен ко входу триггера, выход и вход которого и входы дешифратора и счетчика соединены соответственно со вторым, третьим и четвертым вхо-, дами и первым выходом блока управления, первый и третий выходы которого подключены к первым входам элементов

И, вторые входы которых соединены с первым выходом схемы сравнения чисел, четвертый вход которой подключен к выходу первого элемента И, а второй. выход — к первому входу элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и входом блока пуска — останова.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 318946, кл. G 11 С 29/00, 1968.

2. Авторское свидетельство СССР

9 407398, кл..G 11 С 29/00, 1972 (прототип).