Устройство для формирования последовательности импульсов заданной длительности

Иллюстрации

Показать всеРеферат

Союз Севетскмх

Сецкалкстнчвскмх

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СЬИ ЕТЕЛЬСТВУ (1)769709 (61) Дополммтельное к авт. сеид-ау (22) Заявлено 140277 (2 ) 2451863/26-21 с присоедмнеммем заявим Но (23) Приоритет

Опубликовано 07.1030. Бюллетень Йо 37

Дата опублмкованмя опмсенмя 10.1030 (51)М. Кл.з

H 03 K 3/017

Государственный комитет

СССР ио аелам изобретений н открытий (53) УДК 621. 373. .5(088.8) (72) Авторы мзобретения

Т. М. Алиев, Р. Г. Джагупов, Г. С. Вайсман и Э. К. Тагиев (71) Заявитель

Азербайджанский институт нефти и химии им. M. Азизбекова (54) УСТРОИСТВО ДЛЯ ФОРМИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТИ

ИМПУЛЬСОВ ЗАДАННОИ ДЛИТЕЛЬНОСТИ

Изобретение относится к импульсной технике.

Известны устройства для формирования импульсов, длительность которых зависит от параметров запускающего сигнала (1) и f2 ).

Эти устройства не позволяют формировать импульсную последовательность произвольной длины при подаче на их вход одиночного запускающего импульса, так как необходимым условием появления выходного сигнала в таких устройствах является подача на их вход очередного запускающего сигнала.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство, которое при поступлении на его вход запускающего импульса начинает форми- 39 ровать вьходную последовательность импульсов с частотой, равной частоте синхроимпульсов, причем длительность каждого импульса в последовательности равна длительности синхроимпульса. 25

Формирование последовательности импульсов продолжается до момента поступления на управляющий вход устройства сигнала прекращения формирования выходной последовательности (3), Недостаток известного устройства заключается в невозможности формирования последовательности импульсов, имеющих длительность, задаваемую входным сигналом.

Целью изобретения является обеспечение формирования последовательности импульсов, длительность каждого из которых пропорциональна длительности одиночного запускающего импульса.

Для этого в устройстве, содержащем блок для динамического запоминания запускающего импульса, вход и выход которого являются, соответственно, входом и выходом устройства, блок для формирования тактовых импульсов и управлякхций блок, вход сигнала запуска которого соединен со входом блока для динамического запоминания запускающего импульса, управляющий вход устройства, служащий для подачи сигнала прекращения формирования выходной последовательности импульсов, свяэан с соответствующим входом управляющего блока и со входом установки в начальное состояние блока для формирования тактовых импульсов, синхрониэирующий вход которого является синхронизирующим входом устройства, причем блок

769709 для динамического запоминания запус кающего импульса содержит два узла для управляемой задержки одиночного импульса, каждый из которых состоит из трех ключевых элементов, источника сигнала для заряда конденсатора, накопительного конденсатора и формирователя, выход которого является выходом узла, сигнальным входом узла для управляемой задержки является управляющий вход первого ключевого элемента, сигнальный вход которого подключен к выходу источника сигнала для заряда конденсатора, а выход— к одному из выводов накопительного конденсатора, к которому подключены также сигнальные входи второго и 15 третьего ключевых элементов, другой вывод накопительного конденсатора соединен с выходом второго ключевого элемента, выход третьего ключевого элемента подключен ко входу формиро- 20 вателя, а управляющие входы второго и третьего ключевых элементов являются, соответственно, первым и вторым управляющими входами узла для управляемой задержки, выход первого узла для управляемой задержки связан со входом второго узла и с первым вхо. дом первого элемента ИЛИ, выход которого является выходом блока для ди намического запоминания запускающего импульса, выход второго узла для уп- ЗО равляемой задержки подсоединен ко вторым входам первого и второго элементов ИЛИ, второй вход второго элемента ИЛИ соединен со входом блока для динамического запоминания занус-. 35 кающего импульса, а выход этого элемента ИЛИ вЂ” со входом первого узла для управляемой задержки, выход управляющего блока подключен к управляющему входу блока для формирования тактовых импульсов, первый и второй выходы которого, являющиеся выходами первого и второго тактовых импульсов, связаны со вторыми управляющими входами соответственно первого и второго узлов для управляемой задержки, первые управляющие входы которых подсоединены к управляющему входу устройства.

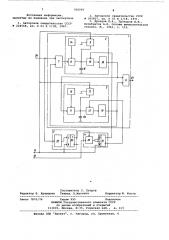

На чертеже дана. функциональная ур схема предложенного устройства.

Устройство для формирования последовательности импульсов заданной длительности содержит блок 1 для динамического запоминания запускающего им-э пульса, в состав которого входят первый и второй узлы 2 и 3 для управляемой задержки одиночного импульса, блок 4 для формирования тактовых импульсов и управляющий блок 5. Блок 1 для динамического запоминания запус- б© кающего импульса содержит также первый и второй элементы ИЛИ б и 7..уз« лы 2 и 3 для управляемой задержки одиночного импульса включают в себя ,.первый, второй и третий ключевые элементы 8, 9, 10 и 11, 12, 13, источники 14 и 15 сигнала для заряда конденсатора, накопительные конденсаторы 16 и 17, а также формирователи 18 и 19 соответственно. Блок 4 для формирования тактовых импульсов содержит ключевой элемент 20 и триггер 21 со счетным входом, а управляющий блок 5 состоит из формирователя 22 и триггера

23. Вход 24 является входом запускающего импульса, вход 25 — входом сигнала прекращения формирования выходной последовательности импульсов, а вход

26 — синхронизирующим входом устройства.

Устройство работает следующим образом.

Запускающий импульс, поступающий на вход 24, открывает через элемент

ИЛИ 7 ключевой элемент 8 на время, равное длительности импульса. Благодаря этому начинается заряд накопительного конденсатора 16 от источника 14 до величины, пропорциональной длительности запускающего импульса, что достигается соответствующим подбором постоянной времени цепи заряда. Одновременно формирователь 22 формирует по заднему фронту запускающего импульса .сигнал окончания заряда, который поступает на установочный вход триггера 23 и переключает его. Потенциал с триггера 23 открывает ключевой элемент 20 и разрешает прохождение синхроимпульса с синхройизирующего входа 26 на счетный вход триггера 21, который своими выходными потенциалами открывает ключевой элемент 10 и закрывает ключевой элемент

13. При этом происходит разряд накопительного конденсатора 16 на входное сопротивление формирователя 18.

Этот формирователь фиксирует моменты начала и конца разряда конденсатора

16 и формирует выходной импульс соответствугющей длительности. Длительность выходного импульса формирователя 18 пропорциональна длительности запускающего импульса, а в случае равенства постоянных времени цепей заряда и разряда конденсатора равна длительности запускающего импульса.

Одновременно с началом разряда конденсатора 16 начинается заряд конденсатора 17, так как выходной сигнал формирователя 18 открывает ключевой элемент 11, а ключевой элемент

13 при этом закрыт. кроме того, импульс с выхода формирователя 18 через элемент ИЛИ 6 поступает на выход 27 устройства.

После исчезновения выходного сигнала на выходе формирователя 18 закрывается ключевой элемент 11, и на конденсаторе 17 сохраняется заряд, величина которого пропорциональна длительности импульса на выходе формирователя 18, и следовательно, длительности запускакицего импульса.

769709

Следующий синхроимпульс, поступающий на счетный вход триггера 21, пе-. реключает его, и выходные потенциалы этого триггера открывают .ключевой элемент 13 и закрывают ключевой элемент 10. При этом происходит разряд конденсатора 17 и формирование, аналогично процессу в предыдущем такте, импульса заданной длительности формирователем 19. Импульс с выхода формирователя 19 поступает через элемент.

ИЛИ 6 на выход 27 устройства и одновременно подается через элемент

ИЛИ 7 на ключевой элемент 8 для управления зарядом конденсатора 16.

По мере поступления синхроимпульсов вышеописанный процесс повторяется, и на выходе устройства образуется последовательность. импульсов с частотой, равной частоте синхроимпульсов, а длительность каждого выходного импульса пропорциональна длительности. запускающего импульса.

При поступлении на вход 25 сигнала прекращения формирования выходной последовательности импульсов кондейсаторы 16 и 17 через открываемые .этим сигналом ключевые элменты 9 и 12 разряжаются, одновременно закрывается ключевой элемент 20, управляемый триггером 23, и устанавливается в начальное состояние триггер 21. В результате этого на выходе 27 устройства сигналы отсутствуют, а само уст.ройство находится в режиме ожидания прихода следующего запускающего импульса.

Таким образом, данное устройство позволяет формировать импульсную последовательность произвольной длины при подаче на его вход одиночного запускающего импульса, причем длительность каждого импульса формируемой последовательности пропорциональна. или равна длительности запускающего импульса.

Формула изобретения

При использовании изобретения, например, во время-импульсных вычислительных устройствах упрощается проведение промежуточных прямых и обратных аналого-цифровых преобразований, а при использовании в устройствах отображения информации упрощается отображение одиночных сигналов.

Устройство для формирования последовательности импульсов заданной длительности, содержащее блок для динамического запоминания запускакщего импульса, вход и выход которого являются, соответственно, входом и выходом устройства, блок для формирования тактовых импульсов и управляющий блок, вход сигнала запуска которого соединен со входом блока для динамического запоминания запускающего импульса, управляющий вход устройст- . ва, служащий для подачи сигнала прекращения формирования выходной последовательности импульсов, связан с соответствующим входом управляющего блока и со входом установки в началь-. ное состояние блока для формирования тактовых импульсов, синхрониэирующий вход которого является синхронизирующим входом .устройства, причем блок для динамического запоминания запускающего импульса содержит два узла для управляемой задержки одиночного импульса, каждый иэ которых состоит из трех ключевых элементов, источника сигнала для заряда конденсатора, накопительного конденсатора и формирователя, выход которого является выходом узла, сигнальным входом узла @ для упраляемой задержки является управляющий вход первого ключевого элемента, сигнальный вход которого подключен к выходу источника сигнала для заряда конденсатора, а выход—

25 к одному из выводов накопительного конденсатора, к которому подключены также сигнальные входы второго и третьего ключевых элементов, другой вывод накопительного конденсатора соединен с выходом второго ключевого элемента, выход третьего ключевого элемента подключен ко входу формирователя, а управляющие входы второго и третьего ключевых элементов являются, соответственно, первым и вторым управляющими входамн узла для управля.емой задержки, о т л и ч а ю щ в ес я тем, что, с целью обеспечения формирования последовательности импульсов, длительность каждого из ко4© торых пропорциональна длительности одиночного запускающего импульса, выход nepaoro узла для управляемой задержки связан со входом второго узла и с первым входом первого элемента

$$ ИЛИ, выход которого является выходом блока для динамического запоминания запускающего импульса, выход второго узла для управляемой задержки подсоединен ко вторым входам первого и второго элементов ИЛИ, второй вход второго элемента ИЛИ соединен со входом блока .для динамического запоминания запускающего импульса, а выход этого элемейта HJIH — со входом -первого уз55 ла as yapasaaeMoA задержки управляющего блока подключен к управляющему входу блока для формирования тактовых импульсов, первый и.второй выходы которогб, являющиеся выходами первого и второго тактовых. импульсов, 40 связаны со вторыми управляющими вхо.дами соответственно первого и второго узлов для управляемой задержки, первые управляющие..входы которых подсоединены к управляющему входу устройства.

769709

Составитель С. Егоров

Редактор Е. Кравцова Техред T.Ìàòî÷êà Корректор М. Коста

Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 7870/76

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Йсточники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР.

М 224568, кл. Н 03 К 1/18, 1967.

2. Авторское свидетельство СССР

В 365807, кл. Н 03 К 1/18, 1971.

3. Дроздов E.А., Прохоров В.И., Пятибратов A. П. Основы вычислительной техники. М., 1961, с. 115.