Устройство преобразования информации

Иллюстрации

Показать всеРеферат

17б 9730

ОЛИС

ИЗОБР

К АВТОРСКОМУ

С."1оз Советских

Соиалнстнческнх

Реслублнк (61) Дополнительное к (22) Заявлено 29.11.78 с присоединением

)M KaÇ

Н ОЗК 13,/02 (43) Опубликовано 07.1 (45) Дата опубликован

) УДК 681.325 (088.8) по делам изобретений н открытий (72) Авторы изобретения

В. И. Уваров и В. А. Окружиов (71) Заявитель (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ИНФОРМАЦИИ

Государственный комитет (23) Приоритет

Изобретение относится к цифровым преобразователям и может быть использовано в системах автоматического управления с цифровыми вычислительными комплексами.

Известно устройство аналого-цифрового и цифроаналогового преобразования информации, с временным разделением работающие по принципу последовательного приближения, содержащие регистр последовательного приближения, связанный с 10 блоком управления, с выходом компаратора и со входом преобразователя код-аналог, выход которого соединен с одним из входов компаратора, другой вход которого связан с источниками аналоговой информа- 15 ции .(11.

Однако такие преобразователи имеют ограниченные функциональные возможности и используются для выполнения операций аналого-цифрового и цифроаналогового 20 преобразования только в одном канале.

Целью изобретения является расширение функциональных возможностей устройства преобразования информации.

Это достигается тем, что в устройство 25 преобразования информации, содержащее преобразователь код-аналог, компаратор, выход которого соединен с первым входом регистра последовательных приближений, второй вход которого соединен с выходом 30 блока управления, введены регистры хранения, аналоговые запоминающие блоки для каждого канала цифроаналогового преобразования, ключ, мультиплексор входных сигналов, регистр адреса, дешифратор адреса, мультиплексор логических сигналов, мультиплексор выходных сигналов и программный блок, причем его вход соединен с первым входом мультиплексора логических сигналов с выходом блока управления, а выход соединен с мультиплексорами входных и выходных сигналов и вторым входом мультиплексора логических сигналов, третьи, четвертые, пятые и шестые входы которого соединены соответственно с выходами первого, второго и третьего регистров хранения и регистра последовательного приближения, а выходы соединены с первыми входами преобразователя код-аналог, выход которого соединен со входом ключа, первый выход которого через второй вход мультиплексора выходных сигналов соединен со входами аналоговых запоминающих блоков, а второй выход соединен с первым входом компаратора, второй вход которого соединен с первым выходом мультиплексора входных сигналов, второй выход которого соединен со вторым входом преобразователя коданалог, а входы соединены соответственно

769730 с шинами аналоговой информации, опорного напряжения и с первым выходом дешифратора адреса, второй выход которого соединен с первыми входами первого, второго и третьего регистров хранения, а входы соединены с первыми выходами регистра адреса, второй выход которого соединен с его первым входом и входом блока управления, а второй вход лодключен ко входной шине управления и ко вторым входам регистров хранения.

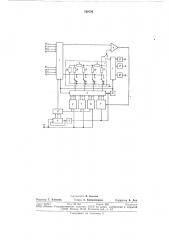

На чертеже представлена структурная схема устройства преобразования информации.

Он содержит мультиплексор 1 входных сигналов, мультиплексор 2 выходных сигналов, мультиплексор 3 логических сигналов, компаратор 4, преобразователь коданалог 5, ключ 6, регистр последовательного приближения 7, первый, второй и третий регистры хранения 8, 9 и 10 соответственно, регистр адреса 11, дешифратор адреса 12, блок управления 13, программный блок 14, аналоговые запоминающие блоки 15, шину опорного напряжения 16, входную шину управления 17 и шины аналоговой информации 18.

Устройство работает следующим образом.

Сигналом управления преобразователя является последовательный двоичный код.

Кодовая посылка содер>кит стартовую

«единицу» в первом разряде, признак управления режимом преобразования во втором разряде (режим) аналого-цифрового преобразования (АЦП) либо режим цифроаналогового преобразования (ЦАП), код адреса и информационный код, Перед началом работы преобразователя сигналом «Обнуление» устанавливается в исходное состояние регистр адреса 11.

Входной код записывается в регистр адреса 11. С появлением стартовой «единицы» в первом разряде регистра 11 входы последнего блокируются. Стартовая «единица» воздействует на блок управления 13, который в зависимости от признака управления режимом во втором разряде регистра 11 вырабатывает команду «Запуск АЦП» либо

«Запуск LIAII». По команде «Запуск АЦП» адресная комбинация, содержащаяся в регистре адреса 11, дешифруется, и сигнал управления с выхода дешифратора 12 воздействует на мультиплексор 1, который подключает выбранный источник входной информации к одному из входов компаратора

4. Одновременно по команде «Запуск АЦП» ключ 6 подключит выход преобразователя код-аналог 5 к другому входу компаратора

4. Команда «Запуск АЦП», воздействуя на мультиплексор 3 логических сигналов, блокирует выходы регистров хранения 8 — 10, воздействуя на мультиплексор 1, подключает шину опорного напряжения 16 к преобразователю код-аналог и включает ре5

2.1

9>5

Я

65 гистр последовательного приближения 7.

Аналоговый сигнал с выхода мультиплексора

1 на входах компаратора 4 сравнивается с напряжением обратной связи, выработанным преобразователем код-аналог 5, который через мультиплексор 3 управляется регистром последовательного приблп>кения 7.

Последний управляется сигналами компаратора 4.

Таким образом, в устройстве преобразования информации в режиме АЦП реализуется аналого-цифровое преобразование по методу последовательного приближения.

Результат преобразования с выходов компаратора 4 выводится в последовательном коде. С выходов регистра последовательного приближения 7 результат преобразования может быть выведен параллельным кодом. По окончании процесса преобразования регистр последовательного приближения 7 вырабатывает команду «Конец преобразования», по которой схема устанавливается в исходное состояние.

Цифроаналоговое преобразование в многоканальном преобразователе информации может происходить в двух режимах: преобразование кода в напряжение; цифроаналоговое перемножение входных сигналов.

Преобразователь код-аналог в схеме реализован по методу суммирования напря>кений из декодирующей матрицы R — 2R. Б режиме преобразования кода в напря>кение к разрядным ключам преобразователя коданалог через мультиплексор 1 подключается источник опорного напря>кения 16. Разрядные ключи управляются параллельным двоичным кодом с соответствующих регистров хранения через мультиплексор 3 и коммутируют напря>кение в разрядах матриц

R — 2R. Напряжение на выходе преобразователя код-аналог пропорционально величине кода.

В режиме цифроаналогового преобразования к разрядным ключам через мультиплексор 1 подключаются знакопеременные напряжения источников постоянного тока, изменяющиеся по произвольному закону.

Разоядные ключи управляются кодом с определенных регистров хранения. Сигнал на выходе преобразователя код-аналог пропорционален произведению входных управляющих сигналов.

Многоканальный преобразователь информации работает следующим образом.

После записи кода в регистр адреса 11 входы последнего блокируются, и блок управления по признаку «Режим ЦАП» в коде управления вырабатывает команду

«Запуск ЦАП». По этой команде адресная комбинация, содержащаяся в регистре 11, дешифрируется, и по сигналу управления с выхода дешпфратора адреса 12 информационный код переписывается в соответствующий регистр хранения. Одновременно

769730 по команде «Запуск ЦАП», воздействующей на мультиплексор 3, блокируются выходы регистра последовательного приближения 7 и снимается блокировка с регистров хранения, ключ б подключает выходы преобразователя код-аналог ко входу мультиплексора 2 и запускается программное устройство 14. Программное устройство 14 работает в циклическом режиме и вырабатывает последовательность команд управле- 10 ния мультиплексорами 1, 2 и 3. По командам программного устройства мультиплексор 1 подключает к разрядным ключам преобразователя код-аналог один из источников входных аналоговых сигналов, мультиплексор 3 подключает к управляющим входам преобразователя код-аналог сигналы соответствующего регистра хранения, а мультиплексор 2 подключает выходное напря кение преобразователя код-аналог ко 20 входам определенного аналогового запоминающего блока.

В следующем такте происходит цифроаналоговая обработка информации для другого абонента. 3а один цикл работы про- 25 граммного устройства 14 происходит последовательный опрос всех источников аналоговых сигналов и соответствующих регистров хранения, преобразование информации и запись результатов преобразования в 30 соответствующие запоминающие блоки.

Использование устройства преобразования информации в аппаратуре позволит качественно улучшить ее характеристики и с максимальной эффективностью использо- 35 вать оборудование, входящее в состав преобразователя. Дополнительное оборудование, позволяющее схему устройства преобразования информации, работающую по методу последовательного приближения, 40 преобразовать в многоканальное устройство преобразования, представляет собой преимущественно логические и аналоговые мультиплексоры и регистры, что при современном состоянии разработок интегральных 45 микросхем позволяет реализовать схему с минимальными затратами.

Формула изобрстсния

Устройство преобразования информации, содержащее преобразователь код-аналог, компаратор, выход которого соединен с первым входом регистра последовательных приближений, второй вход которого соединен с выходом блока управления, отл и ч аю шийся тем, что, с целью расширения функциональных возможностей, в него вве;IeIiII регистры храпения, аналоговые запоминающие блоки для каждого канала цифроаналогового преобразования, ключ, мультиплексор входных сигналов, регистр адреса, дешифратор адреса, мультиплексор логических сигналов, мультиплексор выходных сигналов и программный блок, причем его вход соединен с первым входом мультиплексора логических сигналов и с выходом блока управления, а выход соединен с мультиплексорами входHblx н выходных сигналов и вторы.» входом мультиплексора логических сигналов, третьи, четвертые, пятые и шестые входы которого соединены соответственно с выходами первого, второго и третьего регистров хранения и регистра последовательного приближения, а выходы соединены с первыми входами преобразователя код-аналог, выход которого соединен со входом ключа, первый выход которого через второй вход мультиплексора выходных сигналов соединен со входами аналогoBbix запоминающих блоков, а второй выход соединен с первым входом компаратора, второй вход которого соединен с первым выходом мультиплексора входных сигналов, второй выход которого соединен со вторым входом преобразователя коданалог, а входы соединены соответственно с шинами аналоговой информации, опорного напряжеш1я и с псрвым выходом дешифратора адреса, второй выход которого соединен с первыми входами первого. второго и третьего регистров хранения, а входы соединены с первыми выходаыи регистра адреса, второй выход которого соединен с его первым вхо.1ом и входом блока управления, а второй вход подключен ко входной шине управления и ко вторым входам регистров хранения.

Источники информации, пр1!нятыс Во Вни мание IIpli э! спертизе

1. Патент США ¹ 3504037, кл. 340 — 347, опубл. 1971.

769730

Составитель Л. Беляева

Редактор Т. Клюкина

Техред А. Камышникова

Корректор В. Дод

Типография, пр. Сапунова, 2

Заказ 2422,3 Изд. М 561 Тираж 995 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5