Параллельный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ i ц7б973!

Соизз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 11.10.78 (21) 2672785/18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 07.10.80. Бюллетень № 37 (45) Дата опубликования описания 07.10.80 (51) М. Кл."

Н 03К 13,/ 175

Государственный комитет (53) УДК 681.325(088Л ло делам изобретений и открытий (72) Автор изобретения

В. Я. Загурский

Институт электроники и вычислительной техники

АН Латвийской ССР (71) Заявитель (54) ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к импульсной технике, в частности к устройствам параллельного аналого-дискретного преобразования, в которых множество опорных значений, различных по величине, одновременно сравниваются с аналоговыми значениями преобразуемого сигнала. Устройство может быть использовано в скоростных системах обработки информации.

Известен параллельный аналого-цифро- 1п вой преобразователь, содержащий п групп компараторов н элементов памяти, где n =

= 1, 2, 3,..., п — число разрядов, причем общее число компараторов, подключенных к управляющим входам элементов памяти, 15 составляет 2" —, а элементов памяти — (2" — ), тактовые входы элементов памяти подключены к источнику стробирующего сигнала, а выходы — к разрядным шинам (1).

Недостатки этого АЦП вЂ” низкая точность, равная четырем разрядам, и значительная аппаратурная избыточность.

Наиболее близким по техничсской сущности и достигаемому рсзультату является па- 2,-, раллельный аналого-цифров >й прсобразователь, содержащий группу компараторов старших разрядов и группу компараторои младших разрядов, псрвые входы которых подключсны к выходам источников опор- 3Э ных напряжений, сш нальные входы группы компараторов старших разрядов подключены к источнику преобразуемого сигнала, выходы компараторов в каждой группе, кроме компараторов старших разрядов соответствующей группы, объединены попарно и подключены к управляющим входам соответствующих элементов памяти, выходы компараторов старших разрядов соответствующих групп соединены с управляющими входами соответствующих им элементов памяти, резистивный делитель, источник стробпрующего сигнала и источники тока смещения (2).

Известное устройство имеет недостаточно высокую точность.

Целью изобретения является повышение точности преобразователя.

Поставленная цель достигается тем, .что в параллельный аналого-цифровой преобразователь, содержащий группу компараторов старших разрядов и группу компараторов младших разрядов, первые входы которых подключены к выходам источников опорных напряжений, а сигнальные входы группы компараторов старших разрядов подключеIfbI к 11СТО IH11KI преOOp33)емого сигHQ.t13, выходы компараторов в каждой группе, кроме компараторов старших разрядов соответствующей группы, объединены попар769731 но д подключены к управляющим входам соответствующих элементов памяти, выходы компараторов старших разрядов соответствующих групп соединены с управляющими входами соответствующих им элементов памяти, резистивный делитель, источник стробирующего сигнала и источники тока смещения, введены инвертор, повторитель, элемент И вЂ” ИЛИ н дополнительный резистивный делитель, причем первые входы резистивных делителей подключены к выходам источников тока смещения, вторые входы соответственно через повторитель и инвертор подключены к выходу источника преобразуемого сигнала, а выходы попарно, со сдвиговых на один, через элемент И—

ИЛИ подключены к сигнальным входам группы компараторов младших разрядов, а входы стробирования элементов памяти подключены к выходу источника стробирующего сигнала.

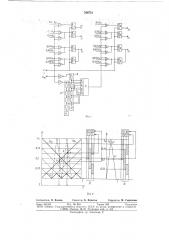

На фиг. 1 представлена блок-схема п-разрядного параллельного аналого-цифрового преобразователя; на фиг. 2 представлены временные диаграммы, поясняющие работу параллельного АЦП. Временные диаграммы построены для входного сигнала в виде линейно нарастающего напряжения.

Устройство содержит вход 1 преобразуемого сигнала (липейпо нарастающего напря>кения) U„,, вход 2 стробирующего сигнала, группу компараторов старших разрядов 3, группу компараторов младших разрядов 4, элементы памяти старших и младших разрядов 5, инвертор 6, повторитель 7, резисторы резистивного делителя 8, подключенного к выходу инвертора 6, резисторы резистивного делителя 9, подключенного к выходу повторителя 7, источники тока смещения 10, 11, подключенные к делителям 8 и 9 соответственно, элемент И вЂ” ИЛИ

12. 13, 14 — выходы элементов памяти старших и младших разрядов соответственно.

В качестве примера рассмотрен 6-разрядный параллельный АЦП, в качестве элементов памяти использованы D-триггеры с входами управления (D) и тактирования (С).

Элемент И вЂ” ИЛИ указывает на выполняемые логические операции, а не представляет собой конкретный тип элемента.

Источники опорного напряжения, подключенные ко вторым входам компараторов

3 и 4, соответствуют уровням квантования, выраженным в долях U, и Е, соответственно, где U, — максимально возможное значение U,, à Е, — максимально возмо>кное значение сигнала источников опорного напряжения группы компараторов младших разрядов.

Число рсзисторов в делителях 8 — 9 одно и то же, зависит от выбранного числа двоичных разрядов, кодируемых группой компараторов старших разрядов, и равно 2"-, где k == 1, 2, 3,..., k — число старших разрядов. В рассматриваемом примере k = 3, 5

05 следовательно, число резисторов равно

2Э- = 4. Резисторы выбирают таким образом, чтобы при равных токах смещения источников 10 и 11 весь диапазон преобразования С,, был разбит на равные части.

Полярность источников 10 и 11 выбирается противоположной, причем для делителя

8 положительная, а для делителя 9 — отрицательная. Таким образом на отводах делителя 8 напряжения сдвинуты друг относительно друга на 0,25 U, в сторону положительных значений, а на отводах делителя 9 — на 0,25 U, в сторону отрицательных значений.

На фиг. 2: квантующая характеристика

15 группы компараторов старших разрядов

3; квантующая характеристика 16 группы компараторов младших разрядов 4; U, преобразуемый сигнал; Е, — сигнал с вы . хода элемента И вЂ И 12; А, Б — значе. ния сигнала U,,- в моменты стробирования;

А, Б — значения сигнала Е„ соответствующие значениям А и Б.

Аналого-цифровой преобразователь работает следующим образом.

Предположим, что на вход 1 подается сигнал U„,, а на вход 2 подаются стробирующие сигналы. Сигнал U,,- квантуется группой компараторов старших разрядов 3 в соответствии с квантующей характеристикой 15 (фиг. 2.) В результате сдвига сигнала U„,- на резисторах делителя 8 происходит изменение напряжений со сдвигом на

0,25 Ь, и параллельно U,,-, а на резисторах делителя 9 с таким же сдвигом, но параллельно инверсии (> вх (. нх).

При изменении напряжений на входах элемента И вЂ И 12 на его выходе формируется сигнал Е„ который квантуется группой компараторов младших разрядов 4 в соответствии с квантующей характеристикой 16 (фиг. 2) . Процесс формирования сигнала Е,. рассмотрим на примере работы схемы, подключенной к выходу повторителя

7 (сигнал U,,) и первому отводу делителя, подключенного к выходу инвертора 6 (сигнал Г,,-, где сигнал U,,- смещен на 0,25 U ) источником тока смещения 10 положительной полярности. Пока на одном из входов элемента И вЂ И U,, ) U„, сигнал на выходе определяется значениями U„„, а когда U„„U„„— значениями U„„-. Это приводит к тому, что на выходе элемента

И вЂ” ИЛИ формируется сигнал Е„равный по амплитуде 0,125 U, и имеющий форму равнобедренного треугольника. Аналогичный процесс происходит и для других входов элемента И вЂ” ИЛИ 12. Сигналы на выходах элементов И объединяются элементом ИЛИ в непрерывно изменяющийся сигнал Е,.

В момент стробирования (например, для точки А фиг. 2) по входам С элементов памяти 5 под действием сигнала 2 (фиг, 2) 769731 происходит параллельное и одновременное запоминание цифрового эквивалента квантованных значений А и А сигналов U,x и

Е„ в результате чего на выходах 13 и 14 элементов памяти 5 одновременно появляется цифровой эквивалент значения U» в точке А (фиг. 2), кодированный в коде

Грея.

Суммарный цифровой результат преобразования получается как суперпозиция циф- 1О ровых значений, получаемых при запоминании элементами памяти с выходами 13 и

14 результатов квантования обеих групп компараторов 3 и 4. Суммарный код следует рассматривать как сумму двоичных чи- 15 сел, которая образуется в момент запоминания кода и хранится в элементах памяти с выходами 13 и 14 до появления по входу

2 следующего стробирующего импульса.

Конкретное значение кода (от старших разрядов к младшим) для точки А (фиг.

2) — 010 + 110 = 010110, что соответствует

27 квантам, а для точки Б — 111 + 101 =

= 111101, что соответствует 41 кванту.

Формула изобретения

Параллельный аналого-цифровой преобразователь, содержащий группу компараторов старших разрядов и группу компараторов младших разрядов, первые входы которых подключены к выходам источников опорных напряжений, а сигнальные входы группы компарато ров старших разрядов подключены к источнику преобразуемого сигнала, выходы компараторов в каждой группе, кроме компараторов старших разрядов соответствующей группы, объединены попарно и подключены к управляющим входам соответствующих элементов памяти, выходы компараторов старших разрядов соответствующих групп соединены с управляющими входами соответствующих им элементов памяти, резистивный делитель, источник стробирующего сигнала и источники тока смещения, о тл и ч а ю шийся тем, что, с целью повышения точности, в него введены инвертор, повторитель, элемент

И вЂ” ИЛИ и дополнительный резистивный делитель, причем первые входы резистивных делителей подключены к выходам источников тока смещения, вторые входы соответственно через повторитель и пнвертор подключены к выходу источника преобразуемого сигнала, а выходы попарно, со сдвигом на один, через элемент И вЂ” ИЛИ подключены к сигнальным входам группы компараторов младших разрядов, а входы стробирования элементов памяти подключены к выходу источника стробирующего сигнала.

Источники информации, принятые во внимание при экспертизе

1. Патент США Ке 3829853, кл. 340-347, 1976.

2. Авторское свидетельство СССР по заявке N 2254459/18-21, 28.04.78 (прототип).

76973I

0,.7 Р!б

Рпг. 7

0,75 ,/,ь/Р г

Корректор М. Гаврилова

Составитель Н. Козлов

Редактор Б. Федотов

Заказ 2412/8 Изд. № 504 Тираж 995 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2