Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

О П И (.". А Н И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистическик

Республик (ii 771666 (Sl) Донолннтельное к авт. свил-яу (22) Заявлено 09.01.79 (21) 2719437/18-24 с присоединением заявки ¹â€” (23) Приоритет— э (51) M. Кл.

G 06 F 7/00

Гесударстеенный комитет

Опубликовано 15.10.80. Бюллетень № 38

Дата опубликования описания 15.10.80 а денны изобретений и открытий (53) УЛК 681.325 (088.8) (72) Авторы изобретения

В. Н. Бессмертный и Д. Я. Золотухина (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ

ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к области автоматики и вычислительной техники, в частности к устройствам сравнения двоичных чисел, и может быть использовано при реализации технических средств автоматики и вычислительных машин.

Известно устройство для сравнения чисел, содержащее элементы И-НЕ (1). Недостатком этого устройства является его относительная сложность.

Наиболее близким к предложенному тсхни10 ческим решением является устройство для сравнения двоичных чисел, состоящее из двух каналов сравнения, содержащих основные и всномогательные транзисторы и шины прямых и инверсных фаз сравниваемых чисел. При этом колt5 лектор каждого транзистора старшего разряда одного канала соединен с эмиттером транзистора младшего разряда того же канала и через резистор — с базой транзистора младшего разряда другого канала, а шины прямой и инверсной фазы соответствующих разрядов сравниваемых кодов связаны с двумя другими резисторами, соединенными с базами транзисторов этих разрядов (2) .

Недостатком этого устройства является постоянное потребление энергии даже при отсутствии сравниваемых чисел и. необходимость использования прямых и инверсных шин сравниваемых чисел.

Целью изобретештя является уменьшение потребляемой энергии и сокращение числа внешних связей.

Поставленная цель достигается тем, что в устройстве, состоящем из и поразрядных узлов сравнения, 2п элементов ИЛИ, причем первый и второй информационные входы каждого i ro поразрядного узла сравнения, где i = 1, 2, ..., n соединены с шинами i-ro разряда первого и второго сравниваемых чисел соответственно, первый выход каждого i-го поразрядного узла сравнения подключен к i-ому входу, i-го, (i+1)-ro, ..., n-ro элементов ИЛИ, второй выход каждого i-го поразрядного узла сравнения соединен с i-ым входом (n + i) -го, (и + i + 1)-го... 2n-го элементов ИЛИ, каждый поразрядный узел сравнения содержит транзисторы, диоды и резисторы, причем первый информационный вход каждого узла соединены через первьш диод с первым

77)666 управляющим входом узла, а через первый резистор — с первым выходом узла, который че. рез второй диод соединен с коллектором первого транзистора, эмиттер которого подключен к коллектору второго транзистора, база которого . соединена через резистор с первым управляющим входом, второй информационный вход каждого узла подключен через третий диод ко второму управляющему входу узла, а через третий резистор — ко второму выходу узла, который через Ip четвертый диод соединен с коллектором третьего транзистора, эмиттер которого соединен с коллектором четвертого транзистора, база которого через четвертый резистор подключена ко второму управляющему входу узла, база первого транзистора через пятый резистор соединена со вторым управляющим входом узла, а база третьего транзистора через шестой резистор подключена к первому управляющему входу узла, эмиттеры второго и четвертого транзисторов соединены с нулевой шиной устройства, первый управляющий вход каждого i-го поразрядного узла сравнения подключен к выходу (i — 1)-ro элемента ИЛИ, а второй управляющий вход каждого i-го поразрядного узла сравнения соединен с выходом (n + i — 1)-го элемента ИЛИ.

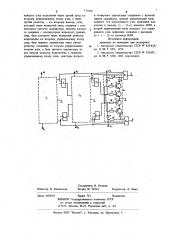

Схема устройства представлена на чертеже.

Устройство содержит и поразрядных узлов сравнения 1,,1, ..., 1и, 2и элементов ИЛИ

21 > 2г, ..., 2 п, 2 и+, ..., 2 и информационные входы 3,, 3,, ..., 3, 4,, 4,, ..., 4„, выходные шины 5, 6, каждый поразрядный узел сравнения состоит из транзисторов 7-10, диодов

11 — 14, резисторов 15 — 20.

Устройство работает следующим образом.

Когда на информационные входы 3,, 3, Зи, 4, 4, ..., 4и в прямом коде поступают сигналы нулевого уровня, на выходных шинах 4

5, 6 устройства отсутствуют сигналы, указывая тем самым, что сравниваемые числа равны. При. этом устройство практически не потребляет энергии. Потребление энергии начинается с появлением сигнала единичного уровня в одном из раз- 45 рядов сравниваемых чисел.

Если на информационные входы 4> 4, 4> поступает, например, число 100, а на информационные входы 3>, 3,, Зэ поступает число 000, то сигнал единичного уровня на входе 4 поступает через элемент ИЛИ 2 на вход 5 устройства, указывая тем самым, что число на входах 4 больше числа на входах 3. Одновременно сигнал со входа 4 через диод 11 и соответствующие ре55 зисторы 15, 17, 19 поступает на базы транзисторов 9 и 7, подготавливая их к открыванию, если на входе 3 появится сигнал, равный сигназу на входе 4.

Если на входы 3 и 4 поступают равные числа, например, !00 и 100, то сигналы единичного уровня на входе 3 и 4, открывают транзисторы 8, 9, 10, 7 и на выходах 5 и 6 устройства отсутствуют сигналы, указывая тем самым, что сравниваемые числа равны.

Если при сравнении чисел одна из них содержит единичный уровень в старшем разряде, например во втором разряде по входу 4, то сигнал единичного уровня через элемент ИЛИ 2 подготовит к открыванию транзистор 7 в младшем разряде второго числа. Таким образом, если в младшем разряде второго числа, например на входе 3> появится сигнал единичного уровня, то транзисторы 10 и 7 открываются и снимают сигнал единичного уровня со входа элемента ИЛИ 13. При этом только на выходе

5 устройства сохраняется сигнал единичного уровня.

Предлагаемое устройство выгодно отличается от прототипа простотой схемного решения и экономичностью потребления энергии в связи с тем, что устройство потребляет энергию только в момент сравнения двоичных чисел, а также тем, что для сравнения чисел нет необходимости представлять их в прямой и инверсной фазе, используя для этого шины прямой и инверсной фазы соответствующих разрядов сравниваемых чисел.

Формула изобретения

Устройство для сравнения двоичных чисел, содержащее и поразрядных узлов сравнения, 2и элементов ИЛИ, причем первый и второй информационные входы каждого i-го поразрядного узла сравнения, где i = 1; 2, ..., п соединены с шинами i-го разряда первого и второго сравниваемых чисел соответственно, первый выход каждого i-го поразрядного узла сравнения подключен к i-ому входу i-го, (i + 1)-го, ..., n-ro элементов ИЛИ, второй выход каждого i-ro поразрядного чзла спавнения соединен с i-ым входом (n + 1)-го, (и + i +1)-ro, ro элементов ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью уменьшения потребления энергии и сокращения числа внешних связей, в нем каждый поразрядный узел сравнения содержит транзисторы, диоды и резисторы, причем первый информационныф вход каждого узла соединен через первый диод с первым управляющим входом узла, а через первый резистор — с первым выходом узла, который через второй диод соединен с коллектором первого транзистора, эмиттер которого подключен к коллектору второго транзистора, база которого соединена через резистор с первым управляющим входом, второй информационный вход

7716Г) 6

Составитель В. Белкин Техред М. Петко Корректор Л Иван

Редактор Н. Каменская

Заказ 6699/61 Тираж 751 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 каждого узла подключен через третий диод ко второму управляющему входу узла, а через третий резистор — ко второму выходу узла, который через четвертый диод соединен с коллектором третьего транзистора, эмиттер которого соединен с коллектором четвертого транзистора, база которого через четвертый резистор подключена ко второму управляющему входу узла, база первого транзистора через пятый резистор соединена со вторым управляющим входом узла, а база третьего транзистора через шестой резистор подключена к первому управляющему входу узла, эмиттеры второго

6 и четвертого транзистора соединены с нулевой шиной устройства, первый управляющий вход каждого i-го поразрядного узла сравнения подключен к выходу (i — 1)-го элемента ИЛИ, а второй управляющий вход каждого i-го поразрядного узла сравнения соединен с выходом (и + i — 1)-ro элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 631914, кл. G 06 F 7/02, 1974.

2. Авторское свидетельство СССР М 332457, кл. G 06 F 7/00, 1965 (прототип).