Устройство для преобразования полярных координат вектора в прямоугольные

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВЧДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<„) 771682 (61) Дополнительное к авт. свид-ву (22) Заявлено 23.06.78 (21) 2633750/18-24 с присоединением эаявнм Йо (23) Приоритет

Опубликовано 15,1080, Бюллетень ¹ 38

Дата опубликования описания 171080 (5!)М. Кл.

G 06 G 7/22

Госуларственный комитет

СССР по ледам н юГ>ретеннй н открыгнй (53) УДК 681 ° 33 (088.8) (72) Авторы изобретения

А. 3. Венедиктов, А. К. Костенич, В. И. Медведев, Г. О. Паламарюк, А. И. Сдвижков, В. И. Соломаха

A. Г. Шевяков и В. И. Кривенков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПОЛЯРНЫХ

КООРДИНАТ ВЕКТОРА В ПРЯМОУГОЛЬНЫЕ

Изобретение относится к области вычислительной техники и может быть использовано в составе вычислителей при решении задач, связанных с преобразованием координат.

Известно устройство для преобразования полярных координат в прямоугольные, содержащсе блок формирования стробов, элементы И, блок умножения, блок памяти, потенциальными входами соединенный с шинами старших разрядов входного кода, ком» мутатор и переключатель квадрантов

f1).

К недостатком такого устройства следует отнести его сложность и недостаточно широкий диапазон изменения входной частоты.

Наиболее близким по технической сущности является устройство для преобразования полярных координат в прямоугольные, которое содержит коммутатор, первый и второй выходы которого соединены со входами делителей частоты, потенциальные входы которых подключены к знаковым выходам переключателя квадрантов, выход переключателя квадрантов соединен со входом коммутатора, потенциальным входом подключенного к управляющему выходу схемы фо!)ггирования стробов, а импульсным — к выходу схемы ИЛИ )2)

Недостатками этого устройства являются сложность обслуживания заданием ординат функции ь1п ос в частотно-импульсной форме, что требует определенных аппаратурных затрат, а также узкий диапазон изменения входной частоты, что вызвано формированием значений sin и cosa за два последовательных такта.

Целью изобретения является расширение диапазона входных сигналов.

15 Цель достигается тем, что устройство для преобразования полярных координат вектора в прямоугольные, содержащее блок памяти и коммутатор, первые входы которых подключены к

20 выходу триггера интервалов, первый вход которого соединен с импульсным входом устройства, первый и второй делители частоты, импульсные входы которых соединены с соответствующими выходами коммутатора, а управляющие входы — соответственно с первым и вторИм выходами квадрантного переключателя, подключенного входом к шине кода квадранта, третий выход

30 квадрантного переключателя соединен

771682

Таким образом эа один период развертывания аргумента, равный Т2 вЂ, с происходит формирование й@„ и й>я., За счет меньшей разрядности ячеек, требуемых для хранения приращений, и эа счет отсутствия в составе блока памяти 5 преобразователя кода в частоту достигается существенная эконо.мия оборудования (около 15%). и R1 %in п . с>Л

N C

Й л Ъ СО$ ) н,, ) с вторыч входом коммутатора, содержит блок число-импульсного умножения, блок сравнения, счетчик> элемент И, триггер запуска, выход которого подключен к первому входу элемента И, второй вход которого подключен к шине опорной частоты, а выход— к импульсному входу блока число-импульсного умножения, потенциальный вход которого соединен с выходом блока памяти, потенциальный выход - c младшими разрядами первой группы входов блока сравнения, первый и второй импульсные выходы — соответственно с импульсным входом коммутатора и с входом счетчика, потенциальный выход которого связан с вторым входом бло- 15 ка памяти и со старшими разрядами первой группы входов блока сравнения, а импульсный выход — с первым входом триггера запуска, второй вход которого соединен с импульсным входом уст-;щ ройства, вторая группа входов блока сравнения подключена к шине задания аргумента вектора, выход блока сравнения соединен с вторым входом триггера интервалов °

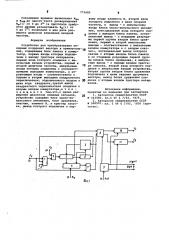

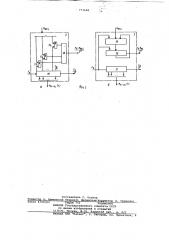

На фиг. 1 Показана блок-схеМа устройства, на фиг. 2 - варианты выполнения блока число-импульсиого умножения.

Устройство содержит триггер 1 запуска, элемент И 2, блок 3 число-им- 30 пульсйого умножения, блок 4 сравнения, блок 5 памяти, счетчик 6, триггер интервалов 7, коммутатор 8, квадрантный переключатель 9, делители частоты 10, 11. Позицией 12 обозначен импульсный 35 вход устройства, 13 — шина задания аргумента, 14 — шина кода квадранта, 15 — шина опорной частоты.

Блок 3 число-импульсного умножения содержит (в первом варианте, фиг.2а) элемент ИЛИ 16, элементы И 17, счетчик 18 ° Во втором варианте (фиг.2б) он состоит из сумматора 19, регистра

20, счетчика 21.

Устройство работает следующим образом.

Полярные координаты вектора, заданные частотой импульсов F> и кодом аргумента N, преобразуются в прямоугольные координаты в соответствии с выражениями йы+г Кать)ж

F F si»

2.е (й б Q Я . )>б

5S где 2 +, 2 =„2% ° ККЬ код номера ч; е квадранта.

В преобразователе с приходом каждого импульса входной частоты Р осу« ществляется формирование число-импульных кодов которые в зависимости от номера квадранта < улмнруются на соответствующих делителях частоты 10 и 11, образуя нэ их выходах импульсы переполнения

Г 14 и %

F»= Р Ь®

"О>, "

< - =z сот,— ч

1 здесь m - -разрядность делителей 10 и

11.

Особенность устройства состоит в том, что фориирование число-импульсных кодов КВ,„ и Ntt>c обеспечивается путем развертывания синусной и косинусной зависимостей во времени. При этом используется кусочно-линейная аппроксимация функций по выражениям

О - Ы„

Sist>tZ б(2. 7 )

I б1 4 С>>,. «gC.

),б>

zoster=z +(z .-z . ) ь(иw) h-i i 1) ос, бб», где 2; — ординаты функции синуса в

i-ом узле аппроксимации.

Формирование число-импульсных кодов КВ;и и й„, осУществлЯетсЯ следУющим образом.

На установочные входы триггера интервалов 7 к триггера запуска 1 поступают импульсы частоты F> и переводят их в единичные состояния.

Триггер 1 разрешает прохождение опорной частоты Ft> на вход блока 3 (а именно на вход счетчика 18 или 21) определяя начало линейного развертывания в нем кода аргумента Nz>>(t) ° При этом счетчик 6 фиксирует текущий код номера интервала разбиения по оси аргумента й>,>, который управляет выборкой из блока памяти 5 кодов приращений ординат N 2. =Ь2 ° 2 в течеC ние интервала Ц=2 1Ро > где 2 - шаг аппроксимации.

В результате развертывания йс) (t) к моменту сравнения на выходе блока

3 формируется число-импульсный код и п Р 2 sinC .

Затем начинается развертывание К рй > при котором триггер 7 изменяет свое состояние на противоположное и подключает к адресным входам блока памяти 5 обратные коды (N „)g» . 3a время дальнейшего развертывания аргумента (от и 1до 2 ) на выходе блока

3 формируется число-импульсный код й

771682

Сокращение времени вычисления Иш. и Марэ до одного "такта развертывания

N®(t) от 0 до 2 (в прототипе требуется дважды развертывать N (t) от

0 до 2 ) позволило в два раза расШирить диапазон изменения входной частоты.

Формула изобретения

Устройство для преобразования полярных координат вектора в прямоуголь- о ные, содержащее блок памяти и комму- . татор, первые входы которых подключены к выходу триггера интервалов, первый вход которого соединен с импульсные входом устройства, первый и второй делители частоты, импульсные входы которых соединены с соответствующими выходами коммутатора, а управляющие входы - соответственно с первым и вторьм выходами квадрантного переключателя, подключенного входом к 26 шине кода . квадранта, третий выход . квадрантного переключателя соединен с вторым. входом коммутатора,о т л и — . ч а ю щ е е с я тем,что,с целью рас- . ширения диапазона входных сигналов, р устройство содержит блок число-импульсного умножения, блок сравнения, счетчик, элемент И, и триггер запуска, выход которого подключен к перВсму входу элемента И, второй вход которого подключен к шине опорной частоты, а выход — к импульснсиу входу блока число-импульсного умножения, потенциальный вход которого соецинен с выходом блока памяти, потенциальный выход - с младаими разрядами первой группы входов блока сравнения, первый и второй импульсные выходы - соответственно с импульсным входом коммутатора и с входом счетчика, потенциальный выход которого связан с вторым входом блока памяти и со старшими разрядами первой группы входов блока сравнения, а импульсный выход — с первым входом триггера запуска, второй вход которого соединен с импульсным входси устройства, вторая группа входов блока сравнения подключена к шине задания аргумента вектора, выход блока Сравнения соединен с вторым входом триггера интервалов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 463986, кл.6 06 G 7/22, l974.

2. Авторское свидетельство СССР

В 596955, кл. G 06 G 7/02, 1976 (про-. тотип).

771682 а „.

Составитель Г. Осипов

Ре анто Н. Каменская Тех е А. Щепанская Ко екто А. Г

Закаэ 6700 62 иценко

Тираж 75 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Ра шская наб. д. 4 5

Филиал ППП "Патент, r. Ужгород, ул. Проектная 4