Устройство для воспроизведения цифровой информации

Иллюстрации

Показать всеРеферат

ОПИ- ИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<11>771712

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 01. 09. 78(21) 2660482/18-10 с присоединением заявки М (23} приоритет

Опубликовано 151080, Бюллетень Й9 38

Дата опубликования описания 18.1080 (51)М. Кл.3

G 11 8 5/09

Государственный комитет

СССР во делам изобретений и открытий (53) УДКЬЗ4. 8Ы2. (088;8) Л.A.Áåëîâà, В.И.Галкин, Д.С.Дубинин, Г.А.Комоцкий, И.A.Ëåñèêîâ, Ю.С.Романов, В.Н.Царьков и Г.Ф.Шамин (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ

ЦИФРОВОЙ ИНФОРМАЦИИ

Устройство относится к области приборостроения, а именно к устройствам записи-воспроизведения цифровой информации с движущегося магнитного носителя. 5

Известно многоканальное устройство записи-воспроизведения цифровой информации, записанной методом узкополосной фаэовой манипуляции j1).

Воспроизводящее устройство вклю- 10 чает в себя головку и усилитель воспроизведения, формирователь, на выходе которого получается сигнал, аналогичный сигналу на входе записывающего устройства. Далее сигнал после 15 пикового детектирования и двухполупериодного выпрямпения одновременно запускает четыре ждущих мультивибратора, имеющих времена задержки

4 4 4 4 — Т Т $ Т 1 Т соответст-.. венно. Пиковые детекторы, фиксирующие задние фронты входных импульсов, вырабатывают короткие импульсы, посие суммирования которых на выходе 25 схемы ИЛИ, получается последовательность синхроимпульсов с периодом .фТ, Импульсы синхронизации поступают на вход 5 триггера. Другой его вход соединен с выходом схемы И, на входы 30

2 которой поступают маркерный импульс с пикового детектора, работающего от мультивибратора с временем задержки 1< Т . На выходе триггера

А получается последовательность импульсов в правильной фазе, обеспечивающей прохождение импульсов, соответствующих "единицам" через вторую схему И. Кипп-реле вырабатывает в момент поступления на его вход коротких импульсов импульсы с длительностью Т, в результате чего на выходе получается исходная кодовая последовательность.

К недостатку этого устройства относится сравнительно невысокая достоверность воспроизводимой информации.

Наиболее близким по технической сущности является устройство для воспроизведения цифровой информации, содержащее информационные каналы и опорный канал, при этом в каждом, информационном канале формирователь импульсов соединен с декодером, а в опорном канале формирователь импульсов соединен с блоком умножения частоты, причем выход блока умножения частоты подключен ко вторым входам декодеров ичформационных каналов g2) .

771712

Недостатком устройства янляется малая устойчивость к временным смещениям между каналами.

Целью изобретения является повышение достоверности носстанонления информации и увеличение устойчивости к временным смещениям между каналами.

Цель достигается тем, что в устройство введены дополнительный информационный канал, аналогичный информационным, и блок проверки на четкость и исправления ошибок, при этом в каждый информационный канал введены корректор переходных характеристик, схема выделения ныпаданий, блок фазирования сигнала выпаданий, блок выделения маркерного слова, три логических элемента И, счетчик адресон занесения, счетчик адресов считывания и два блока памяти, а в опорный канал введены корректор переходных.. характеристик, схема выделения выпаданий, блок восстановления синхроимпульсов и блок выделения маркера, выход которого подключен к обнуляющим входам счетчиков адресов считывания каждого информационного канала, при этом выход формирователя импульсов опорного канала соединен с первыми входами блока выделения пларкера и блока восстановления синхроимпульсов, а выход схемы выделения выпаданий опорного канала подключен ко вторым входам блока восстановле-. ния синхроимпульсов и блока выделения маркера, причем выход блока умно жения частоты подсоединен к третьему входу блока восстановления синхроимпульсов и к одному из входов декодера информационного канала,.при этом выходы корректоров переходных характеристик каждого канала подключены к формирователям импульсов и схемам выделения ныпаданий каждого канала, а. выходы схем выделения ныпаданий информационных каналов через блоки фазирования сигналов вы паданий соединены с третьими входами декодеров, со вторыми входами блоков выделения маркерного слова и первыми входами первых логических элементов И, причем к первым входам блоков выделения маркерного слова . подключены выходы формирователей импульсов, а выходы декодеров подключены к пернйм нходам вторых и третьих логических элементов И, при этом первые выходы блоков выделения маркерных слов соединены со вторыми входами трех логических элементов И, вторые выходы соединены с обнуляющими входами счетчиков адресов занесения, а выходы вторых и первых элементов

И подключены к первым входаи блоков памяти, причем выходы третьих логических элементов И через счетчики адресов занесения своих каналов

lO

35 соединены со ьторыми входами блоков памяти тех же каналов, а.третьи входы блоков памяти связаны с выходами счетчиков адресов считывания, при этом их входы соединены с выходом блока восстановления синхроимпульсов, а выходы блоков памяти каждого информационного канала подключены к соответствующим входам блока проверки на чет ость и исправления ошибок.

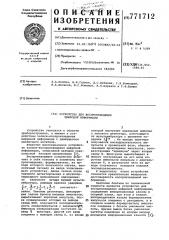

На фиг. 1 изображена функциональная схема устройства, на фиг. 2 временные диаграммы устройства. устройство содержит информационные каналы 1, дополнительный информационный канал 2, аналогичный информационному 1, опорный канал 3 и блок проверки на четкость и исправления ошибок 4.

Каждый информационный канал 1,2 состоит иэ корректора переходных характеристик 5, ныход которого подключен ко входу формирователя импульсов б и через схему выделения выпаданий 7 и блок Фазирования сиг25 нала выпаданий 8 к .третьему входу декодера 9, второму входу блока выделения иаркерного слова 10 и первому входу логического элемента И

11. Выход формирователя импульсов 6

ЗО соединен с первыми входами декодера

9 и блока выделения маркерного слона 10, первый выход декодера 9 †-с первым входом логического элемента

И 12, второй выход декодера 9 — с

35 пеРвым входом логического элемента

И 13,первый выход блока выделения маркерного слова 10 — со вторыми входами логических элементов И 11, 12,13, а второй выход — с обнуляю4О щим входом счетчика адресов занесения 14. Выход логического элемента

И 12 подключен к первому входу блока памяти 15, выход логического элемента И 11 - к первому входу блока памяти 16, а выход логического эле45 мента И 13 через счетчик адресов занесения 14 — ко вторым входам @локон памяти 15,16. Третьи входы блоков памяти 15,16 подключены к выходу счетчика адресов считывания 17.

Опорный канал 3 содержит корректор переходных характеристик 5, выход которого подключен к входу формирователя импульсов б и через схему выделения выпаданий 7 — ко вторым входам блока восстановления синхроимпульсов 18 и блока выделения марке ра 19. Выход формирователя импульсов б соединен с первыми входами блока восстаковления синхроимпульсон 18, 1Я) блока выделения маркера 19 и со вхоропе блока умножения частоты 20, ныход которого подключен к третьим входам блока восстановления синхроимпульсов 18 и декодерам 9 инфор 5 мационных каналов 1,2.

771712

Входы счетчиков адресов считывания

17 информационных каналов 1 соединены с выходом блока восстановления синхроимпульсов 18, а обнуляющие входы счетчиков адресов считывания 17 — с выходом выделения маркера 19. Выходы блоков памяти 15,16 подключены к соответствунщим входам блока проверки на четкость и исправление ошибок 4.

Считанный с магнитной ленты сигнал информационных каналов через корректор переходных характеристик поступает на формирователь импульсов и схему выделения выпаданий.

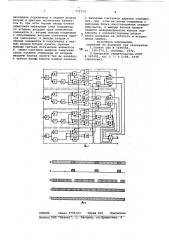

Сформированные формирователем импульсы и импульсы, сфазированные блоком Фазирования сигналов выпа- I5 дания, поступают на декодер и блок выделения маркерного слова. Декодер с помощью импульсов высокой частоты, которые поступают с блока умножения частоты, производят выделение кодо- щ вого сигнала (фиг. 2 а) и Формирует импульсы синхронизации для .занесения этого кодового сигнала в память.

Блок выделения маркерного слова формирует импульс запрета (Фиг.2 б) в момент прохождения в кодовом сигнале маркерного слова, который на логических элементах И производит "вырезки" маркерного слова из информации, определенного числа синхроимпульсов (фиг. 2 в) для занесения в память, а также сигнала выпаданий, соответствующего маркерному слову.

Поступающий со второго логического элемента И сигнал информации заносится в блок памяти в соответствии, З5 с адресами, сформированными в счетчике адресов занесения из синхроимпульсов занесения (фиг.2 в), поступающих с третьего логического элемента И. По такому же принципу эано- 4р сится в другой блок памяти и сигнал выпаданий. о

Сигнал опорного канала через корректор переходных характеристик постуйает на Формирователь импуль- 45 сов и схему выделения выпаданий.

Сформированные формирователем импуль- сы и импульсы со схемы выделения выпаданий поступают на блок восстановления синхроимпульсов, где восстанавливается непрерывная последовательность синхроимпульсов фиг.2 г поступающая на входы счетчиков адресов считывания информационных каналов для формирования адресов считывания, а также на блок выделения маркера для выделения импульса, обнуляющего счетчики адресов считывания.

С формирователя опорного канала., импульсы поступают также на блок умножения частоты, высокочастотные Я) импульсы которого используются для декодирования сигналов и восстановления синхроимпульсов.

Счита™ные с блоков памяти информация и сигнал выпаданий поступают g5 на блок проверки на четность и исправления ошибок, где происходит исправление ошибок, вызванных пропаданиями сигнала на магнитной ленте.

Формула изобретения

Устройство для воспроизведения цифровой информации, содержащее информационные каналы и опорный канал, при этом в каждом информационном канале формирователь импульсов соединен с декодером, а в опорном канале формирователь импульсов соединен с блоком умножения частоты, причем, выход блока умножения частоты, подключен ко вторым входам декодеров информационных каналов, о т— л и ч а ю щ е е с я тем, что, с целью повышения достоверности восстановления информации и увеличения устойчивости к временным смещениям между каналами, в устройство введены дополнительный информационный канал, аналогичный информационным,и блок проверки на четкость и исправление ошибок, при этом в каждый информационный канал введены корректор пе" реходных характеристик, схема выделения выпаданий, блок Фазирования сигнала выпаданий, блок выделения маркерного слова, три логических элемента И, счетчик адресов занесения, счетчик адресов считывания и два бло- ка памяти, а в опорный канал введены корректор переходных характеристик, схема выделения выпаданий, блок восстановления синхроимпульсов и блок выделения маркера, выход которого подключен к обнуляющим входам счетчиков адресов считывания каждого информационного канала, при этом выход формирователя импульсов опорного канала соединен с первыми входами блока выделения маркера и блока восстановления синхроимпульсов, а выход схемы выделения выпаданий опорного канала подключен ко вторым входам блока восстановления синхроимпульсов и блока выделения маркера, причем .выход блока умножения частоты подсоединен к третьему входу блока восстановления синхроимпульсов и к одному из входов декодера дополнительного информационного канала, при этом выходы корректоров переходных характеристик каждого канала подключены к. формирователям импульсов и схемам выделения выпаданий каждого канала, а выходы схем выделения выпаданий информационных каналов через блоки фазирования сигналов выпаданий соединены с третьими входами декодеров со вторыми входами блоков выделения маркерного слова и первыми входами первых логических элементов И, причем к первым входам блоков выделения маркерного слова подключены выходы формирователей импульсов, а выходы

771717

ВНИИПИ Заказ 6705/63 Тираж 662 Подписное

Филиал ППП ".Патент", r. Ужгород, ул.Проектная, декодеров подключены к первым входам вторых и третьих логических элементов И, при этом первые входы блоков выделения маркерных слов соединены со вторыми входами трех логических элементов И, вторые выходы соединены с обнулянхцими входами счетчиков адресов занесения, а выходы вторых и первых элементов И подключены к первым входам блоков памяти, причем выходы третьих логических элементов

И через счетчики адресов занесения своих каналов соединены со вторыми входами блоков памяти тех же каналов, а третьи входы блоков памяти связаны с выходами счетчиков адресов считывания, при этом их входы соединены с выходами блока восстановления синхроимпульсов, а выходы блоков памяти каждого информационного канала подключены к соответствующим входам блока проверки на четкость и исправления ошибок.

Источники информации", принятые во внимание при экспертизе

1.Патент СИА Р 3699556, кл. 340-174,1, опублик, 1972.

2.Авторское свидетельство СССР

9 587491, кл. G 11 В 5/09, 1976 (прототип).