Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

a1..- ÑФЮЯ ФЯ

ЙАТЙ! ..9- i. H ÑÊ

Союз Советских

Социалистических

Республик

О П ЙВ- А-Я И E

ИЗОБРЕТЕНИЯ

77 1 869

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 14.12.78 (21) 2695933/18-21 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано15.10$0. Бюллетень № 38

Дата опубликования описания 1Ы 080 (51) М. Кл. з

Н 03 К 13/02

Государственный комитет

СССР по делам изобретений и открытий (53) АК 881.325 (088.8) (72) Авторы изобретения

Д.М. Верник, Г.A. Столярова и Б.С. Седых (71) Заявитель (54 ) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области автоматики и импульсной техники. Устройство может быть использовано в радионавигационных системах для преобразования напряжений в цифровой 5 код.

Известны устройства, содержащие ключи, корректор и сумматор, выход которого через последовательно соединенные избирательный фильтр, ком- 10 паратор и формирователь временного интервала подключен к э".ементу И (1) .

Эти устройства имеют большую погрешность преобразования и сложны в реализации. !5

Наиболее близким по технической сущности к изобретению является преобразователь, содержащий последовательно соединенные сумматор и ком- 20 паратор, формирователь временного интервала и элемент И, на один вход которого поданы счетные импульсы (2) .

Недостатками такого преобразовате ля являются недостаточно высокое быс- 25 тродействие и значительная методическая погрешность °

Целью изобретения является повышение точности быстродействия преобразователя. 30

Цель достигается тем, тем, что в преобразователь, содержащий последовательно соединенные сумматор и компаратор, формирователь временного интервала и элемент И, введены два распределителя,.шина тактовых импульсов, две весовых матрицы, два коммугатора, два инвертора и интегратор, вход которого соединен с выходом компаратора, а выход подключен к входу формирователя временного интервала.

Причем входы распределителей соединены с шиной -тактовых импульсов,2 N выходов первого и 2 И выходов второго распределителей (N = 2,3,4,...) соединены соответственно с управляющими входами первого и второго коммутаторов, первые выходы которых соединены с входами сумматора непосредственно, а вторые выходы подключены к входам сумматора через инверторы, при этом N выходов первой и и выходов второй весовых матриц соединены с соответствующими входами первого и второго коммутаторов, а входы весовых матриц подключены к входу преобразователя.

Каждый коммутатор состоит иэ 2 N ключей, входы которых, соединенные попарно, подключены к входам комму771869 ) о Д, где Q — преобразуемая аналоговая величина.

С помощью весовых матриц 8 и 9 осуществляется квантование входных напряжений.на М уровней по закону

Й1п -g . Тактовые импульсы, постуЕ пающие на вход распределителей б и 7, преобразуются на их выходах в импульсные последовательности, которые управляют коммутаторами 10 и 11. В ком о мутаторах происходит дискретизация входных аналоговых напряжений по времени с интервалом Т, равным длительности тактовых импульсов. На каждом выходе коммутаторов формируются ступенчатые напряжения, которые складываются в сумматоре 1. Выходное напряжение сумматора поступает на интегратор 14, на выходе которого обра.-уется синусоидальное напряжение

20 Ц и "1 .г- -, где U — амплитуда

/ первой гармоники выходного напряжения сумматора Т = 4 N C — период первой гармоники. Компаратор 2 формирует короткие импульсы с периодом Т, соот2 ветствующие нулевым точкам перехода синусоиды. Полученные импульсы подаются на формирователь време 1ного интервала 3, на второй вход которого поступают тактовые импульсы с нулевым

Зо фазовым сдвигом. длительность сформированного временного интервала пропорциональна величине 9 . Сигнал с выхода формирователя временного интервала поступает на элемент И 4, З5 на другой вход которого подаются счетние импульсы с малым периодом следования. Элемент И пропускает счетные импульсы, чйсло которых соответствует величине 8 . С выхода счетчика снимается цифровой отсчет 8 ..

40 татора, выходы с нечетными порядковыми номерами соединены с первым выходом коммутатора, выходы с четными порядковыми номерами - с вторым выходом коммутатора, причем управляющие входы всех ключей подключены к управляющим входам коммутатора. Каждая весовая матрица содержит М последовательно соединенных элементов с весовыми коэффициентами Р.=51и †1, t где i = 1,2,3,...N

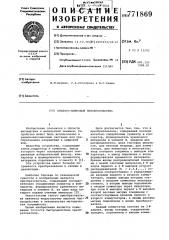

На фиг.1 изображена функциональная электрическая схема устройства; на фиг.2 — электрическая схема коммутатора.

Аналого-цифровой преобразователь . содержит сумматор 1, последовательно соединенные компаратор 2, формирователь временного интервала 3, элемент

И 4, шину 5 тактовых импульсов,два распределителя 6 и 7 тактовых импуль- сов, весовые матрицы 8 и 9, два коммутатора 10 и 11, два инвертора 12 и 13, интегратор 14, вход которого соединен с выходом компаратора 2, а выход подключен к входу формирователя временного интервала 3. Причем входы распределителей б и 7 соедине-. ны с шиной тактовых импульсов, 2 М (М = 2,3,4,. ) выходов распределителя 6 и 2 N выходов распределителя

7 соединены соответственно с управляющими входами коммутаторов 10 и 11, первые выходы которых соединены с входами сумматора 1, а вторые выходы подключены к входам сумматора через инверторы 12 и 13. N выходов матрицы;

8 и М выходов матрицы 9 соединены с соответствующими информационными входами коммутаторов 10 и 11, а входы матриц являются входами преобразователя.

Каждая матрица содержит М последовательно соединенных элементов с ве7Г . совыми коэффициентами Р = 8(2 ( (i = 1&,3,... М), причем вход элемента с номером М является входом и одновременно первым выходом матрицы, а остальные N — 1 ее выходов образованы соединенными между собой элементами.

Оба коммутатора. 10 и 11 идентичны и состоят из 2 N электронных ключей 15-20, входы которых, соединенные попарно, являются входами 2123 коммутатора. Выхбды ключей с нечетными порядковыми номерами соеди Heны между собой и являются выходом

24 коммутатора. Выходы ключей с четными порядковыми номерами соединены между собой и являются выходом 25 коммутатора. Управляющие входы 26-31 всех ключей являются управляющими входами коммутатора.

Устройство работает следующим образом.

На входы преобразователя поступают два аналоговых напряжения ОМЫЛО и

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий последовательно соединенные сумматор и компаратор, формирователь временного интервала и элемент И, отличающийся тем, что, с целью повышения быстродействия и точности преобразования, 50 в него введены два распределителя, шина тактовых импульсов, две весовых матрицы, два коммутатора, два инвертора и интегратор, вход которого соединен с выходом компаратора, а выход подключен к входу формирователя временного интервала, причем входы распределителей соединены с шиной тактовых импульсов, 2 М (N = 2,3,4,. ) выходов первого и 2 N выходов второго распределителей соединены соответст60 венно с управляющими входами первого и второго коммутаторов, первые выходы которых соединены с входами сумматора, а вторые подключены к входам сумматора через инверторы, при этом

6$ N выходов первой и М выходов второй

771869

Составитель l0.Áoãäàíoâ

Редактор Т.Юрчикова Техред Н. Барадулина Корректор В.Бутяга

Заказ 6718/71 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная,4 весовых матриц соединены с соответствующими входами первого и второго коммутаторов, а входы весовых матриц являются входами преобразователя.

2. Аналого-цифровой преобразователь по п.1, отличающийся тем, что каждый коммутатор состоит из 2 и ключей, входы которых, соединенные попарно, подключены к входам коммутатора, выходы с нечетными порядковыми номерами соединены с первым выходом коммутатора, выходы с четными порядковыми номерами подключены к второму выходу коммутатора, причем управляющие входы всех ключей подключены к управляющим входам коммутатора.

3. Аналого-цифровой преобразователь по п.1, о т л и ч а ю щ и.й с я тем, что каждая весовая матрица содержит N последовательно соединенных элементов с -весовыми коэффициентами P =з у 1, где = 1,2,3, й.

7 1

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 417823, кл. G 08 С 9/00, 06.07.72.

2. Авторское свидетельство СССР

Ч 447826, кл. Н 03 К 13/02, 30.01.73.