Мажоритарный логический элемент

Иллюстрации

Показать всеРеферат

О П И С А Н И Е < > 77I876

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Саюз Советских

Сацналнстическнх

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 30.10,78 (21) 2678413!18-21 (51) М.Кл.з Н 03 К 19/42 с присоединением заявки— (23) Приор,итет—

Государственный комитет пп делам изобретений и аткрытнй (43) Опубликовано 15.10.80. Бюллетень № 38 (53) УДК 621.374 (088.8) (45) Дата опубликования описания Оо.05.81 (72) Авторы изобретения

О. Н. Музыченко и В. П. Лукоянов (71) Заявитель

Ленинградский ордена Красного Знамени механический институт (54) МАЖОРИТАРНЫЙ ЛОГИЧЕСКИA ЭЛЕМЕНТ

Изобретение относится к автоматике и вычислительной технике и может использоваться при построении различных устройств переработки дискретной информации.

Известен пороговый логический элемент с порогом, равным трем, на восемь входов, выполненный на элементах И и ИЛИ, в котором каждая из четырех пар входов подключена к входам соответствующих первых элементов И и ИЛИ, выходы каждых трех из четырех первых элементов

ИЛИ подключены к входам соответствующих трехвходовых вторых элементов ИЛИ, выходы последних подключены к первым входам вторых элементов И, вторые входы которых соединены с выходами соответствующих первых элементов И, выходы вторых элементов И подключены к входам ьыходного элемента ИЛИ, выход которого является выходом порогового элемента, вы оды первых элементов ИЛИ подключены также к входам элемента с порогом, равным трем, на четыре входа, выход которого подключен к входу выходного элемента ИЛИ (1).

Такой элемент реализует лишь функцию с порогом, равным трем.

Известен мажоритарный логический элемент, содержащий четыре преобразователя весов двух входов, в каждом из которых первьш вход подключен к одному входу элемента И и к одному входу элемента

ИЛИ, а второй вход — к другому входу элемента И и к другому входу элемента

ИЛИ, при этом выходы элементов ИЛИ и

И являются одновременно выходами преобразователя соответственно с весами 1 и

2, два формирователя наборов весов первой ступени, каждый из которых содержит первый элемент ИЛИ, выход которого является выходом формирователя с весом 1, а к его входам подключены выходы двух преобразователей с весом 1, второй элемент ИЛИ, выход которого является выходом формирователя с весом 2, а к его Входам подключены выходы тех же двух преобразователей с весом 2 и через элемент И выходы с весом 1, третий элемент ИЛИ, выход которого является выходом формп20;,;ователя с весом 3, а к входам подключены выходы двух элементов И, к входам которых подключены соответственно выход с весом 2 одного пз двух преобразователей и выход с весом 1 другого пз этих преобра25 зователей, и элемент И, выход которого является выходом формирователя с весом

4, а входы подключены к выходам двух преобразователей с весом 2, причем взаимно дополняющие весовые выходы обоих формирователей наборов весов первой сту771876 пени попарно подключены к входам формирователя заданного порога второй ступени, выходы которого подключены попарно к входам элементов И с выходами,,подключенными к входам выходного элемента ИЛИ (2).

Недостаток данного мажоритарного логического элемента заключается в ограниченном числе его входов, что сужает функциональные возможности элемента.

Целью изобретения является расширение функциональных возможностей логического элемента.

Для достижения цели в мажоритарный логический элемент, содержащий преобразователи .весов двух входов, формирователи наборов весов первой ступени и выходной элвмент ИЛИ, выход которого является выходом элемента, введены два лреи1 образователя весов "/, входов илн-2 входов при нечетном n (n — число входов мажоритарного элемента), имеющих выходы с весами от 1 до величины, равной числу входов преобразователя, .подключенные попарно к входам элементов И, число которых на единицу меньше величины порога элемента, образуя все неповторяющиеся комбинации весов выходов этих преобразователей, сумма которых равна величине порога элемента, причем выходы элементов и —,

И и выход преобразователя весов и+1 входов с весом, -годключены к входам выходного элемента ИЛИ, а также преобразователи весов т; и р; входов, имеющие выходы с весами от 1 до величины, равной числу входов преобразователя.

При этом каждый из введенных преобразователей содержит два преобразователя весов т; и р; входов с равным и отличающимся на единицу числом входов, сумма которых равна числу входов данного преобразователя, выходы преобразователей весов т, и р; входов подключены попарно к входам групп элементов И, образуя в каждой группе все неповторяющиеся комбинации весов выходов преобразователей весов т, и р; входов, сумма которых одинакова и равна весу одного из выходов данного преобразователя в пределах от 2 до величины, на единицу меньшей числа его входов, выходы элементов И каждой группы и выходы преобразователей весов

m; и р; входов, вес которых равен сумме весов выходов, подключенных к входам каждого элемента И данной группы, подключены к входам элемента ИЛИ, выход которого является одним из выходов данного преобразователя с соответствующим весом, выходы преобразователей весов т; и р, входов с единичными весами подключены к входам элемента ИЛИ, выход

Зо

65 которого является выходом данного преобразователя с единичным весом, а Bblxoды с весами, равными числу входов,— к входам элемента И, выход которого является выходом данного преобразователя с весом, равным числу входов данного преобразователя.

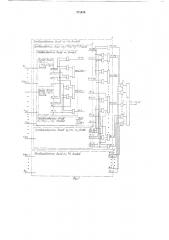

На фиг. 1 представлена структурная схема мажоритарного логического элемента для случая четного числа входов; на фиг. 2 — для случая нечетного числа входов; на фиг. 3 — схема его реализации для десяти входов.

Мажоритарный логический элемент состоит из двух преобразователей 1 и 2 и+1 весов m, = "/, (или при нечетном ив

2 число входов элемента) входов и р; = "/g и — 1 при нечетном п входов, имеющих выходы с весами от QJ 1 до ы „„, = mi y преобразователя 1 и от w „„„,=- 1 до m,, = р у преобразователя 2. Выходы преобразователей 1 и 2 подключены попарно к входам элементов И 3, число которых q — 1, где 1 — величина порога мажоритарного логического элемента, образуя все неповторяющиеся комбинации весов их выходов, сумма которых одинакова и равна 1 — величине порога. Выходы элементов 8, а также выход преобразователя 1 при нечетn+1 ном п с весом z, = mt — — т1 = —, подклю2 чены,к входам выходного элемента ИЛИ 4, выход которого является выходом мажоритарного логического элемента.

Каждый из преобразователей весов

m IH р, входов и все последующие состоят из двух преобразователей 5 и б весов т; и р; входов с равным или отличающимся на единицу числом входов, сумма которых равна числу входов данного преобразователя, и с выходами с весами от 1 до величины, равной числу входов. Выходы преобразователей весов m, и р; входов попарно подключены к входам групп элементов И 7, число групп определяется числом выходов данного преобразователя (1) с весами от 2 до (m,+ð„— 1), образуя в каждой группе все неповторяющиеся комбинации весов выходов преобразователей весов т; и р; входов (5 и б), сумма которых одинакова и равна весу одного из выходов данного преобразователя (1) в пределах от 2 до (т;+р; — 1). Выходы элементов И 7 каждой группы и выходы преобразователей весов m, и р; входов (5 и б) с весом, равным сумме весов выходов преобразователей, подключенных к входам каждого элемента И данной группы, подключены к входам элемента ИЛИ 8, выход которого является одним из выходов данного преобразователя (1) с соответствующим весом. Для образования выхода дан771876 ступени н выходной элемент ИЛИ, выход которого является выходом элемента, о тличающийся тем, что, с целью расширения его функциональных возможностей, в него введены два преобразователя весов — 1

"/ входов плн входов при нечетном

2 2 и (n — число входов мажоритарного элемента), имеющих выходы с весами от 1 до величины, равной числу входов преобразователя, подключенные попарно к входам элементов И, число которых на единицу меньше величины порога элемента, образуя все неповторяющиеся комбинации весов выходов этих преобразователей, сумма которых равна величине порога элемента, причем выходы элементов И и выход преобраи+1 и+1 зователя весов,, входов с весом

2а подключены к входам выходного элемента

ИЛИ, а также преобразователи весов m„. и р; входов, имеющие выходы с весами от 1 до величины, равной числу входов преобра25 зователя, при этом каждый из введенных преобразователей содержит два преобразователя весов m; и р; входов с равным или отличающимся на единицу числом входов, сумма которых равна числу входов данного преобразователя, выходы преобразователей весов m; и р; входов подключены попарно к входам групп элементов И, образуя в каждой группе все неповторяющиеся комбинации весов выходов преобразователей

ВесОВ mI и р,. ВходОВ, c) мма KQTopbIx Одинакова и равна весу одного из выходов данного преобразователя в пределах от 2 до величины, на единицу меньшей числа его входов, выходы элементов И каждой группы и

40 выходы преобразователей весов m; p; входов, вес которых равен сумме весов выходов, подключенных к входам каждого элемента И данной группы, подключены к входам элемента ИЛИ, выход которого является одним из выходов данного преобразователя с соответствующим весом, выходы преобразователей весов m; и р; входов с единичными весами подключены к входам элемента ИЛИ, выход которого является выходом данного преобразователя с единичным весом, а выходы с весами, равными числу входов, — к входам элемента И, выход которого является выходом данного преобразователя с весом, равным числу вхо55 дов данного преобразователя. еа ного преобразователя 1 с весом m;+p; выходы преобразователей вссов m, и р; входов с весами т; и р; соответственно подключены к входам элемента И 9, выход которого и является выходом данного преобразователя (1) с весом т,+р;, а выходы преобразователей весов m; и р; входов (5п б) с весами, равными 1, подключены к входам элемента ИЛИ 10, выход которого является выходом данного преобразователя (1) с единичным весом.

Устройство работает следующим образом.

При поступлении на его входы d единичных сигналов, из которых d, поступает на входы преобразователя 1 весов m, входов 1 и d2 — на входы преобразователя 2 весов р, входов, на всех выходах преобразователя 1 с весами, меньшими или равными

4, и на всех выходах преобразователя 2 с весами, меньшими или равными d2, появляются единичные сигналы. Если величина порога мажоритарного элемента d, то единичные сигналы появляются на обоих входах только одного элемента 8, подключенного к выходу преобразователя 1 с весом d, и к выходу преобразователя 2 с весом d2, что вызывает на его выходе и на выходе элемента ИЛИ 4 появление единичного сигнала. Если d больше величины порога мажоритарного элемента, то единичные сигналы появляются на обоих входах нескольких элементов И 8, что вызывает на их выходах и на выходе элемента .ИЛИ 4 появление единичного сигнала. Если все единичные сигналы поступают на входы преобразоваи --1 теля 1 с числом входов 2 (при нечетном и), то единичный сигнал появляется на выходе мажоритарного элемента только прп появлении единичного сигнала на его выходе с весом, pBBHbIM числу входов. При этом число единичных сигналов равно порогу мажоритарного элемента. Таким образом, каждый раз, когда число единичных сигналов на входах мажоритарного логического элемента больше или равно величии — 1 не его порога (q = при нечетном и

2 и q = "/2-, 1 при четном и) на выходе элемента ИЛИ 4 появляется единичный сигнал.

Таким образом, данный мажоритарный логический элемент имеет большие функциональные возможности по сравнению с прототипом за счет увеличения числа его входов.

Формула изобретения

Мажоритарный логический элемент, содержащий преобразователи весов двух входов, формирователи наборов весов первой

Источники информации, принятые во внимание при экспертизе:

1. Ф. Селлерс, Методы обнаружения ошибок в работе ЭЦВМ, пер. с англ., М., «М ир», 1972, с. 85, фиг. 4.20.

2. Заявка Мэ 1945420/18-21, кл, Н 03 К

19/42, 1973, по которой принято решение о выдаче авторского свидетельства.

771876

И= Nz!, =77 7-!! х, !

) ) (ЛЩ

° °

°, 7z =7 7777 (Ф /",РОЙ,X7Ogmrnp C:E 00 77, = 77/7 0ЛО ФА7.,i@000(),75000т "I o „ г 007 Р77 = / (Р?, 0000

I 7PePdPyg0/70m „7Ь 40077 m, 3ХО00Ь

I,7p

Ф, ф-0002.30,9йа РЛ6 с00 Pf= /7 Р 000Р / !

1 (!

il =i 07

Т=, 771876! х

Редактор T. Юрчикова

Корректор С. Файн

Заказ 420/358 Изд. ¹ 290 Тираж 988 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент» Ъеафа3а5птепь аеас Х окааМ

Х п реобрвзойте,ь уесо3

- а

Составитель Л. Петрова

Техред А. Камышннкова

>/