Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

Союз Советских

Соцнелнстнческнк

Ресяублнк (щ773616 (61) Дополнительное н авт. саид-ву(22) Заявлено 27.04.?9(21) 2759525/18-24 (51) М..Кл.

G 06 F 5/02 с присоединением заявки Йо—

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет—

Опубликовано 23.1030. Бюллетень ¹39

Дата опубликоваии я описания 2 5.1 080 (53) УДК 881. .325(088.8) (72) Авторы изобретения

Ю.С. Тархов и Ю.И. Иихеев

Научно-производственное объединение "Геофизика" (71.} Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В ДВОИЧНО-ДЕСЯТИЧНЫЙ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий переключатель эквивалентов, первый и второй формирователи эквивалентов, блок схем сравнения, блок выделения старшей единицы, шифратор двоично-десятичных чисел, вычислитель, элементы И и элемент задержки (1).

Недостаток известного преобразователя заключается в низком бйстроцействии, обусловленном последова- тельным принципом обработки двоичных и десятичных разрядов и невозможностью обратного преобразования. о

Наиболее близким по технической сущности к предлагаемому является преобразователь двоичного кода в двоично-десятичный, содержащий регистр двоичного числа и последова-, тельно соединенные каскады преобразования, каждый йэ. которых содержит блок выделения старшей единицы, сумматор, шифратор двоично-десятичных чисел, входы которого соединены с соответствующими выходами блока выделения старшей единицы, а выход шифратора двоично-десятичных чисел является десятичным выходом каскада преобразования, информационный вход блока старшего каскада преобразова-! ния соединен с выходом .регистра двоичного числа (2 .

Недостаток этого преобразователя состоит в относительно большом сбъеме аппаратуры и невозможности обратного преобразования. с

Целью изобретения является расширение функциональных воэможностей, f5 заключающихся в обеспечении обратного преобразования и упрощение преобразователя.

Поставленная цель достигается за счет того, что в преобразователе

20 двоичного кода в двоично-десятичный, содержащем регистр двоичного числа и последовательно соединенные каскады преобразования каждый из которых содержит блок выделения

25 старшей единицы, сумматор, шифратор двоично-десятичных чисел, входы которого соединены с соответствующими выходами блока выделения старшей единицы, а выход шифратора дво30 ично-десятичных чисел является де773616 сятичным выходом каскада преобразования, информационный вход блока старшего каскада преобразования соединен с выходом регистра двоичного числа, каждый каскад преобразования дополнительно содержит формирователь двоичного эквивалента,. девять элементов ИЛИ, девять схем сравнения и дешифратор двоично-десятичного кода, выходы которого соединены с первыми входами соответствующих элементов ИЛИ, вторые входы которых соединены с выходами блока . . выделения старшей единицы, а выходы соединены со входами формирователя двоичного эквивалента, выход которого соединен с первым входом суммато- 15 ра, второй вход которого соединен с первыми входами всех схем сравнения и с информационным входом каскада преобразования, выход сумматора является двоичным выходом кас- 2О када преобразования, управляющий вход которого соединен с управляющими входами формирователя двоичного эквивалента и блока выделения старшей единицы, информационные входы которого соединены с выходами схем сравнения, вторые входы которых соединены с входом двоичных эквивалентов, вход дешифратора двоично-десятичного кода является десятичным входом каскада. преобразования. 30

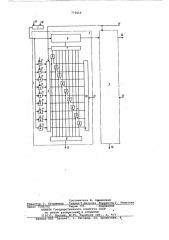

На чертеже представлена структурная схема реверсивного преобразователя двоичного кода в двоично-десятичный.

Устройство содержит регистр 1 дво-.35 ичного числа, старший каскад 2 преобразования, предпоследний каскад 3 преобразования, схемы 4 сравнения, блок 5 выделения старшей единицы, сумматор б, формирователь 7 двоичного эквивалента, шифратор 8 двоично-десятичных чис л, девять элементов

ИЛИ 9, дешифратор 10 двоично-десятичного кода, вход 11 двоичных эквивалентов, десятичный выход 12 стар,шего каскада преобразования, вход .13 старшего каскада преобразования, десятичный выход 14 предпоследнего каскада преобразования, вход 15 предпоследнего каскада пре50 образования, двоичный выход 16 каскада преобразования, управляющий вход

17, вход 18-двоичного числа, вход

19 младшего каскада преобразования.

Предлагаемый преобразователь работает следующим образом.

В режиме прямого преобразования двоичный код преобразуемого числа через вход 18 заносится в регистр 1.

На управляющий вход 17 подается "1", что соответствует прямому преобразо- ® ванию. С выхода регистра 1 параллельным кодом число A подается на вход сумматора б и на все первые входы девяти схем 4 сравнения, относящихся к старшему каскаду 2 преобразования. 65

На вторые входы 11 схем 4 сравнение подается девять двоичных эквивалентов десятичных чисел вида: В = b-.tO" где Ь„ "=1,2,,9; К вЂ” 0,1,2...-номер разряда десятичного числа.

С помощью схем 4 сравнения определяются те двоичные эквиваленты, для которых справедливо неравенство

АЪВ. Схемы сравнения, для которых удовлетворяется это условие, вырабатывают на выходе сигналы> поступающие на блок 5 выделения старшей единицы. Сигнал с выхода блока 5 поступает через первый вход соответствующего элемента ИЛИ 9 (на другие входы элементов ИЛИ подан

"0" в режиме прямого преобразования) на формирователь 7 двоичного эквивалента. Восстановленный соответствующий двоичный эквивалент десятичного числа в дополнительном коде подается на вход сумматора б и вычитается из преобразуемого двоичного числа. Кроме того, сигнал с выхода блока 5 поступает на двоично-десятичный код шифратора 8, на выходе

12 которого форглируется двоично-десятичный код старшей десятичной цифры.

Полученный остаток разности с выхода сумматора б поступает на первый вход сумматора и девять схем сравнения следующего десятичного разряда. Процесс формирова ыя остатков и двоично-десятичных кодов в следующих десятичных разрядах происходит аналогично. Младшая двоичнодесятичная цифра получается непосредственно на выходах 16 четырех младших разрядов сумматора б предпоследнего каскада3 преобразования.

B режиме обратного преобразования двоично-десятичный код подается на дешифратор 10 двоично-десятичного кода. Старший разряд подается через вход 13, а младший — через вход

19 на четыре младших разряда регистра 1. На управляющий вход 17 подается "0", который запрещает работу блока 5, в результате чего его выходы принимают нулевое значение и приводит шифратор 7 двоичных эквивалентов в режим формирования двоичных,эквивалентов в прямом коде.

Младший разряд преобразуемого десятичного числа подается на первый вход сумматора 6 и складывается с двоичным эквивалентом старшего десятичного разряда, который соответствует поданному двоично-десятичному коду. Полученная схема с выхода сумматора б подается на первый вход суьЖатора следующего каскада преобразования. Далее процесс формирования двоичного числа происходит аналогично. Результат преобразования снимается с выхода 16 сумматора

6 предпоследнего каскада преобразования.

773616

Подача двоичных экниналентов на схемы 4 сравнения выполняется практически заземлением входов схем сравнения, соотнетстнующих "0", в пода- . ваемом коде двоичного эквивалента и подаче потенциала на входы, соответствующие "1". Разрядность схем сравнения и шифраторов двоичных экви- . валентов зависит от номера десятичного разряда. Разрядность схем сравнения, кроме того, может быть уменьшена за счет отбрасывания младших iO разрядов постоянно равных нулю во всех девяти двоичных эквивалентах, относящихся к одному десятичному разряду. При выбранной разрядности десятичного числа, К преобразуемое, двоичное число не должно превышать

10 к-1.

Технико-экономическая эффективность предлагаемого устройства определяется тем, что оно может быть использовано для преобразования целых или дробных чисел, при соответствующем включении дноичных эквивалентов.

Время перенода чисел не зависит от разрядности и определяется задерж— ками на переключение логических схем, Применение предлагаемого преобразователя позволяет производить преобразование в реальном масштабе времени. Устройство является универсаль- 30 ным и может быть использовано в специализированных быстродействующих устройствах.

Формула изобретения

Преобразователь двоичного кода н двоично-десятичный, содержащий регистр двоичного числа и последовательно соединенные каскады преобразования, каждый из которых содержит блок выделения старшей единицы, сумматор, шифратор дноично-десятичных чисел, входы которого соединены с соответствующими выходами блока выделения старшей единицы, информационный вход старшего каскада преобразонания соединен с выходом регистра двоичного числа, о т л и ч а ю шийся тем, что, с целью расширения функциональных возможностей, заключающихся в возможности обратного преобразонания и упрощения преобразования, в нем каждый каскад преобразования содержит формирователь двоичного эквивалента, девять элементов ИЛИ, девять схем сравнения и дешифратор дноижо-десятичного кода, выходы которого соединены с первыми входами соответствующих элементов

ИЛИ, вторые входы которых соединены с выходами блока выделения старшей единицы, а выходы соединены со входами формирователя двоичного экви-валента„. выход которого соединен с первым входом сумматора, второй нход которого соединен с первыми выходами всех схем сравнения и информационным входом каскада преобразования, выход сумматора является двоичным выходом каскада преобразования, управляющий вход которого соединен с управляющими входами формирователя двоичного эквивалента и блока выделения старшей единицы, информационные входы которого соединены с выходами схем сравнения, вторые входы которых соединены с входом двоичных эквивалентов, вход дешифратора двоично-десятичного кода янляется десятичным нходом каскада преобразования.

Источники информации„ принятые во внимание при экспертизе

1. Анторское свидетельство СССР

9 523406, кл. G 06 F 5/02, 1973.

2, Авторское свидетельство СССР по заявке Р 2766118, кл.С 06 F 5/02, 19.04.79.

773616

Составитель М. Аршавский

Редактор Т. Куг ыаева Техред Т.Иаточка Ко екто Г. Решетник

Заказ 7506/62 Тираж 75 — Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

Ъ.

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4