Устройство для дистанционного программного управления механизмами

Иллюстрации

Показать всеРеферат

уз

As,Toe%»всi тcl. àe» »å Ô

5ж1л ьК 1 ефФфз Ф ф 4

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Соцналнстнческкк

Реслублнк оо773672 (6l ) Дополнительное к ввт. с вид-ву (22) Заявлено 24,04.79 (2 l ) 2 756543/18-24 (51) M. -Кд.

08 С 19/16

05 В 19/08 (5 06 Р 9/02 с присоединением заявки,%

3Ъвударетеенный коннтет (23) Приоритет ссср ео AellaM нэобретенкй

H открытий

Опубликовано 23.10.80. Бюллетень № 39 (53) УДК 621. . 398 (088.8) Дата опубликования описания 26.10,80 (72) Авторы изобретения

Б. Г. Терехин, Ю. В. Панасейкин, B. В. т1арьков и Ю. Б. Зуев

Государственный всесоюзный научно-исследоватепьский институт строительных материалов и конструкций им. П. П. Будникова (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ ДИСТАНЦИОННОГО ПРОГРАММНОГО

УПРАВЛЕНИЯ МЕХАНИЗМАМИ

Изобретение относится к автоматике и может быть использовано при автоматизации работы механизмов.

Известно устройство для автоматизаmm работы механизмов, в котором используют диодную матрицу, входные узлы, 5 шины, логические элементы, блоки памяти Я.

Недостатком укаэанного устройства является низкая надежность работы и

10 ограниченная функциональная возможность.

При увеличении входов и блоков оперативной памяти в тт раз количество шин и диодов логической части возрастает в

) тФ раз, что делает его громоздким, а значит мапонадежным. При реализации различных функций в зависимости от изменения технологического режима, оно требует перенастройки многих элементов в принципиальной схеме, что ограничивает функциональные возможности устройства.

Наибопее близким по технической сущности к предлагаемому является устройство дня дистанционного программного управления механизмами, содержащее первые и вторые элементы И, первые входы которых соединены с соответствующими информационными входами устройства, выходы первых элементов И подключены к первой шине управления, а выходы вторых элементов И - ко второй шине управпения, усилитель и исполнительный блок 2).

Недостатком известного устройства явт яются ограниченные функцттонапьные возможности устройств а.

Бель изобретения — расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство введены блок управления, элементы И, ИЛИ, НЕ, считывающие элементы и блоки оперативной памяти и запоминающий блок, первая и вторая шины управления подключены соответственно к первым выходам первого и второго элементов НЕ, выходы которых соединены с соответствующими входами третьего элемента И и элемента ИЛИ, выход третье3 7736 го элемента И подключен к первому входу первого считывающего элемента, выход которого соединен с первым входом запоминающего блока, выход первого запоминающего блока через последовательно соединенные усилитель и исполнительный блок подключен к выходу устройства, выход элемента ИЛИ соединен с первым входом второго считывающего элемента, выход которого соединен с первыми входами первого и второго блоков оперативной памяти, выходы второго и третьего блоков оперативной памяти подключены соответственно к первым входам второго. и третьего считывающих элементов, выходы которых соединены соответственно с первой и второй шинами управления, первые выходы блока управления соединены со вторыми входами первых и вторых элементов И, вторые выходы блока управления подключены соответственно ко втоpbnvr входам элементов НЕ, считывающих элементов, запоминающего блока и блоков оперативной памяти, блок управления содержит элемент коммутации, распределитель импульсов, разъемы, генератор импульсов, выход которого подключен к распределителю импульсов, выходы распределителя импульсов через первый штепсельный разъем соединены со входами элемента коммутации, выходы которого подключены через второй штепселЬный разъем с соответствующими первыми и вторыми выходами блока управления.

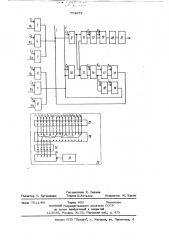

На чертеже представлена схема устройств а.

Устройство содержит шины управления

1 и 2, первые элементы И 3, 4 и 5, вторые элементы И 6„7 и 8, элементы

НЕ 9 и 10, третий элемент И ll элемент ИЛИ 12, первый, второй, третий и четвертый считывающие элементы 13, 14, 15 и 16, блоки 17 и 18 оперативной памяти, запоминающий блок 19, усилитель 20, исполнительный блок 21, блок

22 управления, генератор 23 импульсов, распределитель 24 импульсов, разъем

25 и элемент 26 коммутации.

На чертеже Q Og и Q обозначают входные сигналы от дискретных датчиков (на чертеже не показаны), С 6 KoHTGKчм с которых поступают управляющие импульсы на соответствук щие элементы и звенья от программного блока.

Устройство работает следующим образом е

Реализация алгоритма управления происходит поочередно во времени по управ

72 ф ляющим импульсам, поступающим с программного блока 22. В течение одного такта одновременно происходит подача на шины 1, 2 либо двух входных сигналов, либо одного входного сигнала и одного сигнала с выхода блока оперативной памяти. При этом управляющие импульсы с блока 22 управления поступают на счи» тывающне элементы 13, 14, 15 и 16, а также на элементы HE 9, 10. Запись результатов вычислений осуществляется на блоки оперативной памяти 17, 18 или на запоминающий блок 19 в зависимости от программы. Например, при реализации релейной функции управления (О„+ O )

"Q, где О, Og и g> — входные сигналы, на первом такте импульсы (С

С, C oи С12) с блока 22 управления одновременно попадают соответственно на входные элементы 3, 7, считывающий элемент 14 и в блок 18 оперативной памяти, при этом к шинам 1, 2 подключаются сигналы >q и Ор с дискретных датчиков. Результат вычислений функции д (0 4 < г. ) записывается в блок 18.

На втором такте импульсы (С,, С-т, Со, Qg и С1б ) от распределителя 24 поступают соответственно на входной узел

5, элемент НЕ 9, считывающие элементы

13, 16 и блок 19. При этом входной сигнал Q от дискретного датчика поступает на шину 1, а с считывающего элемента 16 результат вычислений функции (0 +Ф ) попадает на шину 2 через обратную связь. Electee сигнал Q с шины

1 через элемент HE 9 и сигнал, от вычисления функции (4 + >g ) соответственно попадают на элементы И 11 и ИЛИ 12.

Результирующая функция (Q +Op) Qy co

40 считывающего >< M©H 1 - записывается в блок 19 и далее через усилитель

20 поступает на вход исполнительного блока 21, Блоки 9, 10 инвертируют си налы с 8!НН 1„2 ToTIbKo HpH подаче управляющих импульсов < и С .

Таким же образом можно реализовать последовательно во времени любую дискретную последовательно параллельную функцию управления. При возрастании количества входов с дискретных датчиков к шинам 1, 2 подключаются соответственно входные узлы и блоки оперативной памяти.

Изобретение позволяет сократить время простоя оборудования. При изменении технологического режима работы оборудования можно произвести быстро перенастройку его согласно новой прогпамме путем замены, например штепсельного разъема.

Формул а изобретения

1. Устройство для дистанпионного программного управления механизмами, содержащее первые и вторые элементы

И, первые входы которых соединены с соответствующими информаш онными входами устройства, выходы первых элементов И подключены к первой шине управления, а выходы вторых элементов Ико второй шине управления, усилитель и исполнительный блок, о т л и ч а ющ е е с я тем, что, с пелью расширения функпиональных возможностей устройства, в него введены блок управления, элементы И, ИЛИ, НЕ, считывающие элементы, блоки оперативной памяти и запоминающий блок, первая и вторая шины управления подключены соответственно к первым выходам первого и второю элементов НЕ, выходы которых соединены с соответствующими входами третьего элемента И и элемента ИЛИ, выход третьего элемента И подключен к первому входу первого считывающего элемента, выход которого соединен с первым входом запоминающего блока через последовательно соединенные усилитель и исполнительный блок подключен к выходу устройства, выход элемента ИЛИ соединен с первым входом второго считывающего элемента, выход которого соединен с пер73672 выми входами первого и второго блоков оперативной памяти, выходы второго и третьего блоков оперативной памяти подключены соответственно к первым входам второго и третьего считывающих элементов, выходы которых соединены соответственно с первой и второй шинами управления, первые выходы блока управления соединены со вторыми входащ ми первых и вторых элементов И, вторые выходы блока управления подключены соответственно ко вторым входам элементов HE считывакнпих элементов, запоминающего блока и блоков оперативной памяти.

2. Устройство по п. 1, о т л и ч а юm е е с я тем, что блок управления содержит элемент коммутации, распределитель импульсов, разъемы и генератор импульсов, выход которого подключен к распределителю импульсов, выходы распределителя импульсов через первый штепсельный разъем соединены со входами элемента коммутации, выходы которого подключены через второй разъем с соответствующими первыми и вторыми выходами блока управления.

Источники информации, принятые во внимание при экспертизе

1. Шария Ю. С. и др. Комбинаторные шкалы в системах автоматики. М., «Энергия 1973 с 105

2. Авторское свидетельство СССР . ¹ 395886, кл. Q 08 С 19/16, 1970 з (прототип ) .

773672

Тираж 682 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Заказ 7511/65

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель Е. Бакеев

Редактор Т. Кугрыщева Техред И.Асталош Корректор М. Коста