Блок управления запоминающим устройством

Иллюстрации

Показать всеРеферат

— — т». оки

1 ™, ! " бв;1, ь; »

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистичаских

Республик

< 773722 (61) Дополнительное к авт. саид-ву (22) Заявлено 06.04. 79 (21) 2749378/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 231080, Бюллетень ¹ 39

Дата опубликования описания 25. 10. 80 (51)М. Кл.з

G 11 С 7/00

Государственный комитет

СССР но делам изобретений и открытий

G 06 F 9/00 (53) УДК 681 327 (088.8) (72) Автор изобретения

Д. Е. Перельмутер (71) Заявитель (54 ) БЛОК ДЛЯ УПРАВЛЕНИЯ ЗАПОМИНАЮЩИМ

УСТРОЙСТВОМ

Изобретение относится к запоминающим устройствам и может быть испсльзовано в любых устройствах вычислительной техники, где требуется автоматическая установка триггеров в исходное состояние в момент включения.

Известен блок для управления запоминающим устройством, который состоит из элемента задержки и триггера обращения, установочный вход которого соединен с шиной обращения, а сбросовый вход соединен с отводом элемента задержки 11) .

Недостатком этого блока является необходимость автоматической установки триггера обращенйя в исходное состояние после включения питания, что требует дополнительного оборудования.

Наиболее близким по технической сущности к предлагаемому изобретению является блок, состоящий из элемента задержки, и триггера полуцикла, установочный вход которого соединен через элемент И с выходом элемента задержки и шиной строба записи, а сбросовый вход соединен с нулевым выходом триггера запроса (2) .

Недостатком этого блока также является необходимость автоматической установки триггеров запроса и полуцикла в исходное состояние

5 после включения питания, что требует затрат оборудования и, следовательно, усложняет блок.

Цель изобретения — упрощение блока.

1Р Поставленная цель достигается тем, что в блок для управления запоминающим устройством, содер;;ащий элемент задержки, триггеры, блок питания, шину нулевого потенциала, причем входы установки и сброса триггеров подключены к выходам элемента задержки, введен разделительный элемент, причем информационные входы триггеров подключены к шине

2р нулевого потенциала, а входы синхронизации триггеров соединены через разделительный элемент с выходом источника питания. При этом разделительный.элемент целесообразно

25 выполнить в виде резистора.

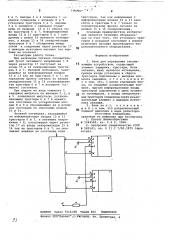

На чертеже представлена структурная схема блока для управления запоминающим устройством.

Блок содержит элемент 1 задержки

Зр с выходами 2, 3, 4 и 6, триггеры а ° . е %

7 7«b g

Формула изобретения

ВНИИПИ Заказ 7516/68 Тираж 662 Подписное

Филиал ППП"Патент",г.ужгород, ул. Проектная 4

Э

6 и 7. Выходы 2 и 4 элемента 1 . адержки соединены с входами 8 и 9 установки триггеров 6 и 7, выходы

3 и 5 элемента 1 задер:хки соединены со входами 10 и 11 сброса те;;. же триггеров 6 и 7. Информационные входы 12 и 13 триггеров 6 и 7 соединены с шиной 14 нулевого потенциала, а входы 15 и 16 синхронизации триггеров 6 и 7 объединены между собой и соединены через резистор 17 с выходом источника питания (на чертеже не показан).

Рассмотрим работу блока.

При включении питания положительный фронт питающего напряжения + Е через резистор 17 поступает на входы 15 и 16 синхронизации триггеров 6 и 7. Нулевой потенциал, находящийся на информационных входах

12 и 13 тех же триггеров 6 и 7, по переднему фронту сигнала на входах синхронизации 15 и 16 устанавливает эти триггеры 6 и 7 в исходное (нулевое) состояние.

При подаче на вход элемента 1 задержки импульса на выходах 2, 3, 4 и 5 появляются импульсы, устанавливающие триггеры 6 и 7 в единичное состояние по установочным входам 8 и 9 и сбрасывающие их в исходное состояние по сбросовым входам . 10 и 11.

Нулевой потенциал, находящийся на информационных входах 12 и 13 триггеров 6 и 7, и питающее напряжение + Е, поступившее через резистор 17 на входы синхронизации 15 и

16 тех же триггеров 6 и 7, не оказывают влияния на состояние этих триггеров, так как информация с информационных входов 12 и 13 зано сится в триггеры 6 и 7 только по положительному фронту сигнала на входах 15 и 16 синхронизации.

Основным преимуществом изобретения является экономия оборудования за .счет того, что установка триггеров в исходное состояние в момент включения питания производится без дополнительного оборудования.

1. Блок для управления запоминающим устройством, содержащий элемент задержки, триггеры, блок питания, шину нулевого потенциала, причем входы установки и сброса триггеров подключены к выходам эле3О мента задержки, о т л и ч а ю щ и йс я тем, что, с целью упрощения блока, он содержит разделительный элемент, причем информационные входы триггеров подключены к шине нулевого потенциала, а входы синхрониэа/ ции триггеров соединены через разделительный элемент .с выходом источника питания.

2. Блок по п.1, о т л и ч а юшийся тем, что разделительный элемент выполнен в виде резистора.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании

Р 1044580, кл. G 4 С, 1966.

2. Авторское свидетельство СССР

Р 585543, кл. G 11 С 7/00,1975 (прототип).