Матричный накопитель

Иллюстрации

Показать всеРеферат

0 и ь. и!А :и"и е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<>773728

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 27. 04. 79 (21) 2758997/18-24 с присоединением заявки М (23) Приоритет—

Опубликовано 23.1080. Бюллетень М39

Дата опубликования описания 25. 10. 80 (51)М. Кл.з

G 11 С 11/34

Государственный комитет

СССР ио дедам изобретений и открытий (53) УДК б81. . 327 . б б (088. 8) (У2) Авторы изобретения

A.Ì. Заброда, М.Д. Кардащук, С.К. Лесничий, А.Г. Максимчук, A.A. Мержвинский и О.Г. Мороз-Подворчан

Ордена Ленина институт кибернетики AH Украинской CCP (7! ) Заявитель (54) МАТРИЧНЫЙ НАКОПИТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на биполярных транзисторных структурах. 5

Известен накопитель постоянных запоминающих устройств, собранный на биполярных транзисторах, в которых запись информации производится путем и дачи электрических сигналов на 10 соответствующие внешние выводы f1/.

Недостатком накопителя, где запоминающие элементы включены в цепь коллектора транзистора, является недостаточно высокая плотность ин- 15 формации.

Наиболее близким по технической сущности к предлагаемому является накопитель, содержащий числовые шины, разрядные шины, соединенные с числовыми шинами посредством диодов и запоминающих элементов, транзисторы, эмиттеры которых соединены с раэрядныйи .шинами, коллекторы — с выходными шинами, а базы посредством 25 резисторов соединены с входными шинами накопителя (2).

Недостатком такого накопителя является большое число внешних выводов, что требует большого коли- 3р чества оборудования, а это, в свою очередь, приводит к увеличению стоимости всего ПЗУ, увеличению. потребляемой мощности и снижению быстро действия.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем)

° что в матричный накопитель, содержащий последовательно соединенные запоминающие элементы и диоды, которые подключены между числовыми и разряд; ными шинами, транзисторы, коллекторы которых подключены к выходным шинам, эмиттеры — к разрядным шинам, а базы — через резисторы к входным шинам: введены группы транзисторов и первые и вторые адресные шины, причем коллекторы транзисторов первой группы подключены к числовым шинам, базы к первым адресным шинам, а эмиттеры подключены к коллекторам транзисторов второй группы, которые через резисторы подключены к шине питания, базы транзисторов второй группы подключены ко вторым адресным шинам, а эмиттеры — к общей шине накопителя.

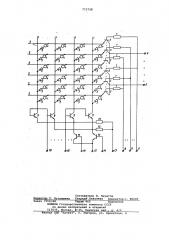

На чертеже показана электрическая схема матричного накопителя.

773728

Устройство содержит числовые шины

1 и разрядные шины 2, соединенные между собой диодами: 3, и запоминающие элементы 4, к разрядным шинам подключены эмиттеры транзисторов 5, коллекторы которых соединены с выходными шинами 6, а базы — с резисторами 7. Другие выводы резисторов

7 подключены ко входным шинам 8, коллекторы транзисторов 9 первой группы соединены с числовыми шинами 1, с первыми адресными шинами

10, а эмиттеры подключены к коллекторам транзисторов 11 второй группы и через резисторы 12 к шине 13, базы транзисторов соединены со вторыми адресными шинами 14., а эмиттеры — с общей шиной 15.

Матричный накопитель работает следующим образом.

В режиме записи на шину 15 подают нулевой потенциал, а на шину 13 положительный потенциал, например

2-5 В, на одну иэ шин 10 и 14 подают токи выборки. В результате открываются транзисторы 9 и 11, соединенные с выбранными шинами, и подключают одну из числовых шин 1 к общей шине 15.

Остальные шины 1 остаются отключенными от общей шины 15, так как в цепочке транзисторов 9, 11 этих шин хотя бы один оказывается закрытым.

На одну иэ шин 8 подают потенциал записи, а на остальные — нулевой потенциал. При этом транзисторы 5, подключенные к выбранной числовой шине 1 переходят в режим насыщения, а остальные находятся в режиме отсечки. В соответствии с записываемой информацией на выходные шины 6 пода-. ется ток записи или нулевой потенциал. В первом случае ток записи через выбранный транзистор, находящийся в режиме насыщения, попадает на соответствующую разрядную шину, а оттуда через диод и запоминающий элемент — на выбранную числовую шину, производя запись. Во втором случае ток, протекающий через выбранный резистор 7 стекает через коллекторный переход транзистора на выходную шину и запись не происходит

В режиме считывания, так же как и при записи выбранная числовая шина

1 подключается, а остальные отключаютоя от общей шины 15. На выбранную входную шину 8 подается потенциал высокого уровня, а на остальные нулевой потенциал. При этом, в зависимости ст состояния проводимости за поминающих элементов, находящихся на пересечении выбранных, числовой и разрядных шин, ток выбранных резис торов 7 через эмиттерные переходы транзисторов 5, разрядные шины и проводящие запоминающие элементы, не проводят, через коллекторные переходы поступает на выходные шины накопителя. В первом случае на выходных. шинах устанавливается потенциал низкого уровня, а во втором высокого.

По сравнению с известным предлагаемый накопитель дает значительный . выигрыш в количестве внешних выводов. Минимально возможное число внешних выводов известно- го накопителя равно m = ЗЧЙ

1 где Н - объем информации. В предлагаемом накопителе минимально возмСо15 ное число внешних выводов m< = 478+2, Например для объема 4096 бит в = 48/ а m = 26, причем в первом случае диодная матрица оказывается слишком несимметричной (16 числовых и 256 разщ рядных шин), что приводит к потерям в плотности информации и быстродействии, в то время как в предлагаемом накопителе количество числовых и разрядных шин равно 64. Если же в .извесь ном накопителе число разрядных и; числовых шин уравнять, .то накопйтель будет иметь уже 8С внешних выводов, что приводит к необходимости подключения дополнительного оборудования и усложнению накопителя.

65

55 стекает на выбранную числовую шину, либо, если запоминающие элементы

Формула изобретения

Матричный накопитель, содержащий последовательно соединенные запоми-нающие элементы и диоды, которые подключены между числовыми и разрядными шинами, транзисторы, коллекторы которых подключены к выходным шинам, эмиттеры — к разрядным шинам, а базы — через резисторы к входными шинам, отличающийся тем, что, с целью упрощения устройства, в него введены группы транзисторов и первые и вторые адресные шины, причем коллекторы транзисторов первой группы нодключены к число- вым шинам,базы — к первым адреснымшинам, а эмит те ры подключ е ны к коллен торам транзисторов второй группы, которые через резисторы подключены к шине питания, базы транзисторов второй группы подключены ко вторым адресным шинам, а эмиттеры - к общей шине накопителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 506060, кл. G 11 С 11/34, 1973.

2. Авторское свидетельство СССР по заявке 9 2697090, кл. G 11 С 11/34

18.12.78 (прототип).

773728

5 68 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Раушская наб. д. 4 5

Закаэ

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель В. Муратов

Редактс т. кугрышева тех е Н.ковалева корректор О. Билак