Запоминающий элемент

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И„ЗОБ РЕТЕ Ы ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалиетическик

Республик

< >773738 (6I ) Дополнительное к авт. свид-ву (22) За" влено 17.04.79 (21) 2753296/18 2 с присоединением заявки РЙ .(23) Приоритет

Опубликовано 23.10.80 Бюллетень Ж 39

Дата опубликования описания 02,. 11.8Q (5! )М. Кл.

Гасударственный комитет

G 11 С 11/34 ео делан иаабретеккй к открытнй (53) УЛ 681.327. 66(088.8) (72) Авторы изобретения

Б. В. Кузнецов, E. И. Потемкин и Ю. А. Уральский

Г

1 !

1 с

j (7I) Заявитель

ЗАПОМИНАЮШИЙ ЭЛЕМЕНТ (54) 1

Изобретение относится к вычислительной технике, в часности к запоминающим устройствам цифровых вычислительных машин.

Известен запоминающий элемент на

МДП-транзисторах, содержащий триггер, управляющие МДП-транзисторы, разрядные и адресные шины (1).

Известен также запоминающий элемент, содержащий триггер на МДП-транзисторах с нагрузочными МДП-транзистором и диодом, включенными в разные плечи триггера (21.

Наиболее близким по технической сущности к предлагаемому является запоминающий элемент, содержащий триггер на МДП-транзисторах и управляющий

МДП-транзистор, сток (исток) которого соединен с одним из плеч триггера, исток (сток) соединен с разрядной шиной, а затвор — с адресной шиной 3 .

Недостатком известных запоминающих элементов является значительное потребление мощности.

Кроме того, статические запоминающие элементы на МДП-транзисторах требуют увеличенных геометрических размеров транзисторов, что в случае интегрального исполнения увеличивает

5 площадь, занимаемую таким запоминающим элементом на кристалле. Как правило, такие схемы потребляют в момент переключения сравнительно большую мощность и обладают малой надежто ностью из-за частого пробоя подзатворного диэлектрика в мощных управляющих транзисторах.

Целью изобретения является уменьшение потребляемой мощности.

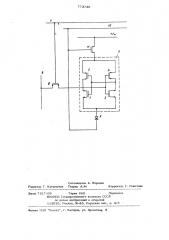

Поставленная цель достигается тем, что в запоминающий элемент, содержащий триггер, выполненный на первом, втором, третьем и четвертом МДП-транзисторах, причем затворы третьего и четвертого МДПгранзисторов, сток первого и сток второго МДП-транзисторов соединены со стоком (истоком) пятого

МДП-транзистора, исток (сток) которого.

77 37

3 подключен к разрядной шине, а затвор— к адресной шине, тактовую шину и шину питания, введены шестой МДП-транзисто и диод, катод которого соединен с тактовой шиной и затвором шестого МДП-тран$ зистора, исток шестого МДП-транзистора подключен к шине питания, а сток — к истокам второго и четвертого МДП-транзистров, анод диода соединен с истоками первого и третьего МДП-транзисторов.

На чертеже представлена электрическая схема изобретения.

Запоминающий элемент содержит первый, второй, третий и четвертый МДП-транзисторы 1-4, образующие триггер 5, разрядну ю шину 6, адресную шину 7, пятый МД П-транзистор 8, диод 9, тактовую шину 10 и шестой МДП-транзистор 11.

Устройство работает следующим образом.

При записи логической "1" в исходном состоянии на шины 6 и 7 подается логическая "1", а на шину 10-"0". За логический "0" принимается нижний уровень напряжения (В), а за логическую

1" — верхний уровень (+E1 ). В этом случае транзистор 8 закрыт, а транзистор 11 открыт и в триггере 5, состоящем из транзисторов 1-4, хранится информация, полученная от предыдущей записи. В следующий момент времени снимается питание триггера 5, т.е. на шину

10 подается "1" и транзистор 11 закрывается. Далее идет перепись "1" с шины

6 в триггер 5, для чего на адресную

3S шину 7 подается лигический "0", а через некоторый промежуток времени включается питание триггера 5 путем подачи на шину 10 логического "0", после чего

40 триггер 5 (без динамического потребления) готов к хранению записанной в него информации. При подаче на адресную шину 7 1" транзистор 8 закрывается и происходит хранение логической "1

Для считывания логической "1" на

43 адресную шину 7 подается "0", транзистор

8 открывается и логическая "1" через шину 6 поступает на транзисторы 3 и 4.

При записи и считывании логического 0"

38 4 очевидно, что все действия идентичны, за исключением того, что предварительно на шине 6 присутствует логический

"0" и в процессе запуска триггер 5 устанавливается в противоположное положение.

Таким образом, предлагаемый запоминающий элемент обладает меньшей потребляемой мощностью за счет того, что триггер 5 предварительно подготавливается к работе до момента подачи сигналов на шину 10 тактовых импульсов.. формула изобретения

Запоминающий элемент, содержащий триггер, выполненный на первом, втором, третьем и четвертом МДП-транзисторах, причем затворы третьего и четвертого МДП-транзисторов, сток первого и сток второго МДПгранзисторов соединены со стоком (истоком) пятого

МДП-транзистора, исток (сток) которого подключен к разрядной шине, а затвор — к адресной шине, тактовую шину и шину питания, отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введены шестой

МДП вЂ” транзистор и диод, катод которого соединен с тактовой шиной и затвором шестого МДП-транзистора, исток шестого МДП-транзистора подключен к шине питания, а сток — к истокам второго и четвертого МДП-транзисторов, анод диода соединен с истоками первого и третьего МДП-транзисторов.

Источники информации, принятые во внимание при экспертизе

1.Старос ф. Г. и др. Полупроводниковые запоминающие устройства, "Энергия", Л., 1973, с. 48-53.

2. Авторское свидетельство СССР

Мю 431554, кл. С 11 С 11/40, опублик. 1 97 4.

3. Сборник Микроэлектроника". Под

Ред. Лукина ф. В., Советское Радио", M., вып. 5, 1975, с. 135, рис. 5а (прототип) .

7737 38

Составитель А. Воронин

Редактор Т. Кугрышева Техред А.Ач Корректор Г. Решетник

Заказ 7517/69 . Тирвж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектнаи, 4