Способ преобразования частотноимпульсного сигнала в код и устройство для его осуществления

Иллюстрации

Показать всеРеферат

< >773927

О П

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (51) Ила (22) Заявлено060379 {21) 2735813/18-21 с присоединением заявки Мо (23) Приоритет

Опубликовано 2 310.80. Бюллетень Но 39

Дата опубликования описания 231080

Н 03 К 13/20

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 325 (088.8) (72) Автор .. изобретения

Г. О. Паламарюк

Рязанский радиотехнический институт (71) Заявитель (54) СПОСОБ ПРЕОБРАЗОВАНИЯ ЧАСТОТНО-ИМПУЛЬСНОГО

СИГНАЛА В КОД И УСТРОИСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных частотно-импульсных вычислительных устройств и . реобразователей типа частота-код. . Известен способ преобразования частотно-импульсного сигнала в код, основанный на формировании длительности импульсов, кратных или равных периоду Тх измеряемой частоты

Рк,и квантовании этой длительностьк образцового интервала времени То с одновременным кодированием результата (1).

Недостатком способа является низкое быстродействие.

Известен способ преобразования частотно-импульсного сигнала в код, основанный на принципе последовательного сравнения входной частоты и ее остатков с соответствующими значениями опорных частот (2).

- Недостатком способа является низкое быстродействие преобразования.

Цель изобретения — повышение быстродействия.

Указанная цель достигается тем, что в способе преобразования частотно-импульсного сигнала в код, основанном на принци .е последовательного сравнения входной частоты и ее остатков с соответствующими значениями опорных частот, входной сигнал разбивают на Р частей, каждую из частей,за исключением первой, умножают, часть входного сигнала,содержащего высокочастотные составляющие, преобразуют в код по методу поразрядного взвешивания, выделяют остаток, который подвергают умножению, высокочастотную часть умноженного остатка входного сигнала преобразуют по методу поразрядного взвешивания

15 в код, формируют второй остаток, который подвергают умножению, высокочастотную часть второго умноженного остатка преобразуют в код по методу пора=-:рядного взвешивания с последую20 щим выделением третьего остатка, который также подвергают умножению и т.д., умноженный Р 1-й остаток преобразуют по методу поразрядного взвешивания в код.

Устройство для осуществления спо соба содержит Р преобразователей частота-код, соединенный последовательно, каждый из которых, кроме последнего, содержит преобразователь поразрядного взвешивания, первый

773927 вход которого соединен с первым входом блока выделения остатка, и входной клеммой преобразователя частота-код, второй вход соединен с выходом преобразователя поразрядного взвешивания, третий вход соединен

r. клеммой источника опорной частоты, выход через умножитель частоты соединен с выходной клеммой преобразователя частота-код, второй и третий выходы умножителя частоты соединены с клеммами источников опорных частот, а последиий преобразователь частота-код выполнен на преобразователе поразрядного взвешивания.

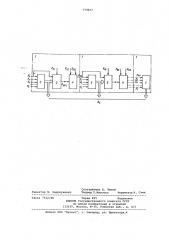

На чертеже приведена структурная электрическая схема устройства.

Устройство содержит Р преобразователей 1 частота-код, которые состоят из преобразователей 2 поразрядного взвешивания, блоков 3 выделения остатков, умножителей 4 частоты. 20

Преобразователи 2 имеют вхоцные и одну выходную шину.

На первую входную шину поступают импульсы измеряемой частоты Г, на другие шины поступают импульсы опорных частот F, Г, Г,...,F„ . Предположим, что устройство разбито на четыре преобразователя 1, коэффициенты умножения умножителей 4 соответственно равны: и = 4, m = 16, m = 32.

Так как с помощью умножителей 4 частот частота на их выходе увеличивается в 16 раэ, делители частот во всех блоках 3 имеют три разряда.

Число разрядов преобразователей 2 равно соответственно 9, 2, 4 и 5.

Допустим, что входная частота изменилась в виде скачка от нуля до

1023476 Гц, в кодовой шине первого преобразователя сформируется код 40

N = 110011111 .

По истечении времени С = 0,65 мс блок 3 сформирует импульсную последовательность Fact„ 1524 Гц. На выходе первого умножителя 3 45 1(2 ост m = 6096 Гц.

В кодовой шине второго преобразователя 2 сформируется код N g = 01.

По истечении C — — 0,5 мс второй блок 3 выдаст импульсную последовательность Fa > = 2000 Гц. На выходе второго умножителя 4

Гост m „ = 32000 Гц. В кодовой шине третьего преобразователя 2 сформируется код N> = 1111 .

По истечении а = 0,77 мс третий блок 2 сформирует имп.льсную последовательность F тз = 1284 Гц. На выходе третьего умножителя 4 получают

F „4 = Fact m > = 41088 Гц. В кодовой шине четвертого преобразователя 2 сформируется код N4 = 00101д . Время четвертого преобразователя .4=0,024 мс. Таким образом,результирующий код равен N = 00101111101110011111 .

Время измерения N составляет

T> = 1,94 мс.

Увеличение числа умножителей частоты приводит к дальнейшему повышению быстродействия преобразования.

Формула изобретения

1. Способ преобразования частотно-импульсного сигнала в код, основанный на принципе последовательного сравнения входной частоты и ее остатков с соответствующими значениями опорных частот, о т л и ч а юшийся тем„ что, с целью повышения быстродействия преобразования, входной сигнал разбивают на Р частей, каждую из частей, за исключением первой множают часть вхо р у

I д ного сигнала, содержащего высокочастотные составляющие, преобразуют в код по методу поразрядного взвешивания, выделяют остаток, который подвергают умножению, высокочастотную часть умноженного остатка входного сигнала преобразуют по методу поразрядного взвешивания в код, формируют второй остаток, который подвергают умножению, высокочастотную часть второго умноженного остатка преобразуют в код по методу поразрядного взвешивания с последующим выделением третьего остатка, который подвергают умножению, умноженный P 1-й остаток преобразуют по методу поразрядного взвешивания в

gPB °

2. Устройство для осуществления способа по п.1, содержащее Р преобразователей частота-код,соединенных последовательно, каждый из которых, кроме последнего, содержит преобразователь поразрядного взвешивания, первый вход которого соединен с первым входом блока выделения остатка, и входной клеммой преобразователя частота-код,второй вход соединен с выходом преобразователя поразрядного взвешивания,третий вход соединен с клеммой источника опорной частоты, а выход через умножнтель частоты соединен с выходной клеммой преобразователя частота-код, второй и третий входы умножителя частоты соединены с клеммами источников опорных частот, а последний преобразователь частота-код выполнен на преобразователе поразрядного взвешивания.

Источники информации, принятые во внимание при экспертизе

1. Орнатский П.П. Автоматические измерения и приборы. Киев, "Вища школа", Головное изд-во, 1973, с. 522.

2. Авторское свидетельство СССР

Р 341160, кл. Н 03 К 13/20, 1971 (прототип).

773927

Редактор М. Недолуженко

Заказ 7532/80

Fg

Fg

Fg

6 составитель A. Титов

Техред Т.Маточка Корректор Н. Стец

Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4