Устройство декодирования м-последовательности

Иллюстрации

Показать всеРеферат

Союз Советскик

Соцнвлтеск.

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ!

>773948 (61) Дополнительное к авт. свид-ву (5ЦМ. Кл.з (22) Заявлено 21,0,77 (21) 2478955/18-09 с присоединением заявки Мо (23) Приоритет

Опубликовано 231080.Бюллетень ¹ 39

Дата опубликования описания 231080

Н 04 L 17/30

Н 04 L 1/16

Государственный комитет

СССР оо делам изобретений и открытий (53) УДК 621. 394. . 6 (088. 8) (72) Авторы изобретения

В.В. Лосев и B.Ä. Дворников

1 „ 1

1,4 й;: .;; .

Минский радиотехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЕКОДИРОВАНИЯ Й-ПОСЛЕДОВАТЕЛЬНОСТИ

Изобретение относится к радиотехнике и может использоваться в системах связи с блочным кодированием информации М-последовательностью.

Известно устройство декодирования 5

М-последовательности, содержащее генератор поля Галуа, выход которого через первый коммутатор; подключен к входам первого и второго запоминающих блоков, первый регистр и 10 блок выбора максимального сигнала (1).

Однако такое устройство имеет невысокую помехоустойчивость.

Цель изобретения — повышение помехоустойчивости. 15

Для этого в устройство декодирования М-последовательности, содержащее генератор поля Галуа, выход которого через первый коммутатор подключен к входам первого и второго запо- 2Q минающпх блоков, первый регистр и блок выбора максимального сигнала, введены элемент ИЛИ, второй регистр и последовательно соединенные арифме тический блок, третий регистр и вто- 25 рой коммутатор, выходы которого подключены соответственно к входу блока выбора максимального сигнала, соединенного с входом второго регистра и вторым входом первого и второго запо- З() 2 минающих блоков, выходы которых через последовательно соединенные элемент ИЛИ и первый регистр подключены к входам арифметического блока, другой выход которого подключен к второму входу второго коммутатора, третий вход которого соединен с вторым входом первого коммутатора и выходом блока управления, второй выход которого подключен к третьим входам первого и второго запоминающих блоков, третий выход подключен к другим входам первого, второго и третьего регистров, а четвертый выход подключен к третьему входу первого коммутатора.

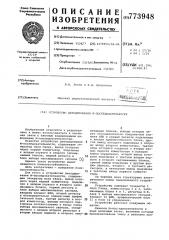

На чертеже дана структурная электрическая схема предложенного устройства.

Устройство содержит генератор 1 поля Галуа, коммутаторы 2 и 3, запоминающие блоки 4 и 5, регистры 6-8, блок 9 выбора максимального сигнала, элемент 10 ИЛИ, арифметический блок

11 и блок 12 управления.

Устройство работает следующим образом.

Символы М-пос."едовательности в виде двоичных чисел, величина которых пропорциональна знаку и величине при773948 нимаемого сигнала, поступают через коммутатор 2 на информационные Входы первого запоминающего блока 4. B это

Время к адресньж входам этого блока с помощью коммутатора 3 годключаются выходы генератора 1. В результате этоГО Зиа Е111тн ВХОДНОГО СИГНала ЗНПИСЫваются в ячейки памяти запоминающегo бЛОКа 4 ПО аДт7ЕСам, ОПРЕДЕЛЯЕМЫМ В каждый момент времени номером символа

N-последовательности и состоянием Вы- ходов генератора 1. Поле генерируется

В соотьетствии со степенью элемента поля.

Для Др;- кОДНРОвания необхОДимо ум ножить записанную В запомина1ощий бл(к (1 Р етлт13 BIIHB lа MBTР1тт1у ApBMB— ра„ т,е. Вычислить коэффициенты корреляции с функциями уота. Это может быть сделанст с помОтщью алгОритма быстрых преобразований„

Дрт1р1 зтОго УстРОйстВО пеРРеключает — Щ сН В Режи(т(Вычисления когДа к аД""

Рес11ь1м Входам запоминающегo б IQI(B 4 чеp("3 коммутeттор 3 подключаются выхО

Ды б71окe 1 2 . "Ва17омийающий блОк 5 пеРЕ 5," т71(тн -т Р т(Я На айит Ь Р- IIú!BOßO В (ЛЕ», рт т"

ДУ1СЩЕт". ПОС ЧРЭДОБаТЕЛЬНОСТИ И К Е O

Х атт„7 (7нцм Вх()ЛBltl через кощ1уj, атор

Пот" КЛЮЧВЮТ(!7 ВЫХОтты т Е НЕРВ рРтОтрт;. 1

ПроисхОдит су1ря (ированирт" ч Выт(НTани

Пар С111,.1ВОЛQZ» CТОЯ1(1ИХ РЯДОМ (0 И 1, 2 и 3, 4 и 5 и т.д.). Полученные

cyMm=l и Разности записываются B ячейт(И Па; Hти ЗBIIOIIHHBI(IIIIeI O блока

ИРиче м р сУмма 3 аписыэ аетсЯ э Яч ейкУ р которой было емое, B peзность за1тись1вается э ячейкjj р З5 и которой было считано второе сла ГаемОе . При этОм „пОскольку нулеэойт симьол равен 0 (QTcyTcTByeT) э ячейКv ДЛЯ СУММЫ ЗаПИШЕТСЯ СатМО ЧИСЛОр B

В т(т(Е- йКУ ДЛЯ РаЭНОСТИ -- ЧИСЛОр УМНО-,Щ

zeHHoe HB -1. Сч11таннь1е числа через

1 0 ИЛИ I7OIIBJ BIOT HB регистра 6 и запоминаются э нем на эрем1т» вы 1ислеиия, 8 ао11фметическом блОке- 11 происходит Вычисление суммы и разности чисел, поступающих с

Выходов Регистра 6. Сумма, через коммутатор 2, непосредственно попадает

На ИНФОРМВЦИОННЫЕ ВХОДтэ- ЗНПОМИНавщего блока 4„ B разность записывается и регистр 8.

После произведен11ых вычислений полученные коэффициенты начинают анализироваться блоком 9. В этом блоке 9 определяется максимальный коэффициент корреляции и номер, под 55 которым он находится в последовательности всех коэффициентов. Этот номер

ДЭОИЧНОй форме ПРЕДСТаэлЯЕт СОбсй .Декодированные символы, при этом первому коэффициенту присваивается номер 0.

Декодированные символы, поступающие с выхода блока 9, записываю;ся в регистр 7, с которого выводятся на выход устройства.

На этом заканчивается декодирование одной И-последовательности, к этому времени оказывается заполненным запоминающий блок 5 и, после соответствующей коммутации, начинаО ется декодирование вновь записанной

М-последовательности.

Назначение блока 12 — формировать соответствующие сигналы для управления режимами записи — чтения запоминающих блоков 4 и 5, управления работой коммутаторов 2 и 3 и синхронизации работы регистров 6-8.

Предложенное устройство работает не с бинарноквантованными символами, а с числами, осуществляя прием в целом,помехоустойчивость которого выще позлементного, реализуемого в известном устройс "ae.

Формула изобретения устройс»О декодирования М-последовательности, содержащее генератор поля Галуа, выход которого через пергый коммутатор подключен к входам

IIepsoro и второго запоминающих блоков, первый регистр и блок выбора максимального сигнала, о т л и ч а ющ е е с я тем, что, с целью повы1аения помехоустойчивости, введены элемент ИЛИ, второй регистр и последовательно соециненные арифметический блОК, Третнй рЕГИСтр и ВторОй КОмМутатор, Вю(оды которого подключены соответственно к входу блока выбора максимального сигнала, соединенного с входом второго регистра и вторым

Входом первого и второго запоминающих блоков, выходы которых через последовательно соединенные элемент ИЛИ и первый регистр подключены к входам арифметического блока, другой выход которого подключен к

Второму входу второго коммутатора, третий вход которого соединен с

Вторым входом первого коммутатора и выходом блока управления, второй

Выход которого подключен к третьим входам первого и второго запоминающих блоков, третий выход подключен к другим входам первого, второго и третьего регистров, а четвертый выход подключен к третьему входу первого коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке Р 2416008,кл.Н 04 L 7/02р

1976.

Составитель P.Ìàðêèíà

Редактор T.Kèñåëåâà Техред Е.Гаврилешко Корректор .С.шекмар

Заказ 7534/81 Тираж 729 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4