Усилитель с защитой от перегрузки

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских (и) 77780

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 11.07.78 (21) 2642534/18-09 (51) M. Кл.з

Н 03F 3/20 с присоединением заявки №

Государственный комитет (23) Приоритет (53) УДК 621.375.026 (088.8) (43) Опубликовано 07.11.80. Бюллетень № 41 (45) Дата опубликования описания 07.11.80 по делам изобретеиий и открытий (72) Авторы изобретения

К. С, Глиненко, 3. Д. Грицкив, Г. А. Туркинов и В. И. Шклярский

Львовский ордена Ленина политехнический институт (71) Заявитель (54) УСИЛИТЕЛЬ С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ

Изобретение относится к радиотехнике и может использоваться в различных радиотехнических устройствах.

Известен усилитель с защитой от перегрузки, содержащий последовательно соединенные предварительный и двухтактный транзисторные каскады, подключенные к источнику питания со средней точкой, датчики перегрузки, включенные в токовые цепи каждого плеча двухтактного каскада и соединенные через цепь управления с транзисторами защиты, промежуток коллектор-эмиттер первого из которых включен параллельно входу предварительного транзисторного каскада, а коллектор второго через диод подключен к базе транзистора одного из плеч двухтактного транзисторного каскада (1).

Однако в усилителе при срабатывании схем защиты на выходных транзисторах выделяется значительная мощность.

Цель изобретения — уменьшение мощности рассеяния.

Для этого в усилителе с защитой от перегрузки, содержащем последовательно соединенные предварительный и двухтактный транзисторные каскады, подключенные к источнику питания со средней точкой, датчики перегрузки, включенные в токовые цепи каждого плеча двухтактного каскада и соединенные через цепь управления с транзисторами защиты, промежуток коллекторэмиттер первого из которых включен параллельно входу предварительного транзисторного каскада, а коллектор второго через диод подключен к базе транзистора одного из плеч двухтактного транзисторного каскада, эмиттер второго транзистора защиты соединен со средней точкой источ10 ника питания.

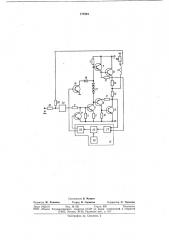

На чертеже приведена электрическая принципиальная схема предлагаемого усилителя.

Усилитель с защитой от перегрузки со15 держит предварительный транзисторный каскад, выполненный на транзисторе 1 и резисторах 2 — 5, двухтактный транзисторный каскад, выполненный на транзисторах

6 — 9 и резисторах 10 — 12, датчики пере20 грузки, выполненные на резисторах 13, 14, цепь управления 15, транзисторы 16 и 17 защиты, диод 18, а также входные резисторы 19 и 20, диоды 21 для выбора исходного режима транзисторов 8 и 9, согласующий

25 усилитель 22, резистор 23 обратной связи, катушку 24 индуктивности. Цепь управления 15 состоит из блока 25 управления, триггера 26, компаратора 27, кнопки 28 сброса.

З0 Усилитель работает следующим образом, 777801

Входной сигнал через согласующий усилитель 22 и резистор 2 поступает на базу транзистора 1. Усиленный сигнал с коллектора транзистора 1 поступает на базы транзисторов 6 и 7 и далее на базы транзисторов 8 и 9, которые через резисторы 13 и 14 нагружены катушкой 24 с последовательно соединенным резистором 23 обратной связи. В результате по катушке 24 протекает ток, вызывающий отклонение луча электронно-лучевой трубки в соответствии с подведенным к входу сигналом. Снимаемое с резистора 23 напряжение через резистор 20 подводится по входу согласующего усилителя 22, чем обеспечивается требуемая стабилизация тока катушки 24.

Если рабочие токи транзисторов 8 и 9 не превышают некоторого заданного значения, транзисторы 16 и 17 закрыты и не влияют на работу усилителя. Диод 18 защищает транзистор 16 от пробоя отрицательным напряжением, возникающим на базах транзисторов 6 и 7 при открытом транзисторе1.

Если токи транзисторов 8 и 9 превышают заданное значение (например, при подаче на вход усилителя сигнала, амплитуда которого превышает допустимое значение или при коротком замыкании нагрузки), то напряжение, снимаемое с резисторов 13 и 14 и подводимое к входу компаратора 27, приводит к срабатыванию компаратора 27, вследствие чего триггер 26 переводится в единичйое состояние. При этом блок 25 управление формирует управляющие сигналы, которые переводят транзисторы 16 и 17 в насыщенное состояние. В результате транзистор 1 запирается, а на.базах транзисторов 6 и 7, благодаря наличию открытого диода 18 и транзистора 16, устанавливается потенциал, близкий к нулевому. Транзисторы 6 и 7 и, следовательно, транзисторы 8, 9, а также нагрузка обесточиваются.

После устранения причин перегрузки схема переводится в рабочее состояние путем нажатия кнопки 28 сброса. При этом триггер 26 переводится в нулевое состояние, а блок 25 управления вызывает запирание транзисторов 16 и 17.

Использование предлагаемой схемы выгодно отличает предлагаемый усилитель от прототипа, так как в отличие от прототипа при срабатывании транзисторов 16 и 17 за5 щиты в транзисторах 6 — 9 двухтактного транзисторного каскада устанавливается нулевое значение тока, тогда как в прототипе устанавливается наперед заданный максимально допустимый ток. Этим исклю10 чается перегрев выходных каскадов усилителя и, следовательно, надежность усилителя возрастает. Повышение надежности позволяет снизить затраты на работы по ремонту устройства, а также затраты, возни15 кающие в связи с простоем ЭВМ, для вывода Информации от которой используется устройство с усилителем.

Применение предлагаемой схемы может быть полезно также в усилителях, иного

20 назначения, например в усилителях низкой частоты, усилителях мощности схем автоматики и т. п.

Формула изобретения

Усилитель с защитой от перегрузки, содержащий последовательно соединенные предварительный и двухтактный транзисторные каскады, подключенные к источнику питания со средней точкой, датчики перегрузки, включенные в токовые цепи каждого плеча двухтактного каскада и соединенные через цепь управления с транзисторами защиты, промежуток коллектор-эмитЗ5 тер первого из которых включен параллельно входу предварительного транзисторного каскада, а коллектор второго через диод подключен к базе транзистора одного из плеч двухтактного транзисторного каскада, 40 отличающийся тем, что, с целью уменьшения мощности рассеяния, эмиттер второго транзистора защиты соединен со средней точкой источника питания.

Источники информации, принятые во внимание при экспертизе

1. Рубрика «3а рубежом». «Радио», 1973, Ко 8, с. 60 (прототип).

777801

Составитель В, Маврин

Техред В. Серякова

Редактор Ж. Рожкова

Корректор Л. Тарасова

Типография,. пр. Сапунова, 2

Заказ 2422/10 Изд. № 561 Тираж 995 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5