Устройство контроля цифро-аналогового преобразователя

Иллюстрации

Показать всеРеферат

О П И С А Н И Е >777816

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 18.12.78 (21) 2697516/18-21 с присоединением заявки— (23) Приоритет—

151) 1.Кл.з Н 03 К! 3/34

Государственный комитет по делам изобретений и открытий (43) Опубл икова (088.8) (45) Дата опубликования описания 04.12.80 (72) Авторы изобретения

C. С. Коган, С. Е. Квн и В. Н. Соколов (71) Заявитель (54) УСТРОЙСТВО КОНТРОЛЯ

ЦИФРО-АНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ

Изобретение относится к цифровым системам связи, вычислительной технике и злектроизмерениям.

Известно устройство контроля цифроаналогового преобразователя (ЦАП), содержащее датчик цифрового сигнала, разрядный цпфро-аналоговый преобразователь, сумматор по модулю два, и первых элементов И, элемент ИЛИ, распределитель импульсов делитель частоты, формирующий блок, видео".онтрольное устройство (ВКУ), и блок объединения, первый вход которо"0 соединен со входом делителя частоты, входом датчика цифрового сигнала и с клеммой входа строчных импульсов, второй вход блока объединения подключен через формирующий блок к клемме входа кадровых импульсов и ко входу кадровой синхронизации ВКУ, а также .к управляющим входам распределителя импульсов и делителя частоты, выход котор|ого соединен с другим входом распределителя импульсов, третий вход блока объединения соединен с выходом сумматора по модулю два, выход датчика цифровых сигналов подключен ко входам и первых элементов И, другие входы которых соединены с соответствующими выходами распределителя импульсов, выходы и первых элементов И подключены ко входам элемента ИЛИ (1).

Контроль ЦАП в данном устройстве производится с использованием обратного аналого-цифрового преобразования, что огранпчивает точность:контроля из-за вносимых реальным аналого-цифровым преобразог ателем дополнительных искажений.

Кроме того, известное устройство не позволяет выявить влияние отдельных разрядов ЦАП на суммарную погрешность.

Целью изобретения является повышение точности и качества контроля цифро-анало".îâîãî преобразователя.

Поставленная цель достигается тем, что в устройство контроля ЦАП, содержащее

15 датчик цифрово;о сигнала, и-разрядный

ЦАП, сумматор по модулю два, и первых

:., сментов И, элемент ИЛИ, распределитель импульсов, делитель частоты, формирующий блок, видеоконтрольное устройство

;. б. ок объединения, первый вход которого соединен со входом делителя частоты, Входом датчика цифрового сигнала и с клеммой входа строчных импульсов, второй вход блока объединения подключен через

>З формирующий блок к клемме входа кадровых импульсов и;ко входу кадровой синхронизации ВКУ, а также к управляющим входам распределителя импульсов и делителя частоты, выход которого соединен с другим входом распределителя импульсов, 777816 третий вход блока объединения соединен с выходом сумматора по модулю два, выход датчика цифровых сигналов подключен ко входам и первых элементов И, другие входы которых соединены с соответствующими выходами распределителя импульсов, выходы и первых элементов И подключены ко входам элемента ИЛИ, дополнительно введены дешифратор, и вторых схем И, полосовой фильтр, два модулятора, инвертор, вход которого соединен с выходом элемента ИЛИ и управляющим входом первого модулятора, выход инвертора подключен:к управляющему входу второго модулятора, входы дешифратора соединены с выходами распределителя импульсов, выходы дешифратора подключены к первым входам и вторых элементов И, вторые входы которых соединены с выходами датчика цифрового сигнала, а выходы и вторых элементов И подключены через ЦАП к входам полосового фильтра, выход к оторого через первый модулятор соединен с первым, а через второй модулятор — co вторым входом сумматора по модулю два.

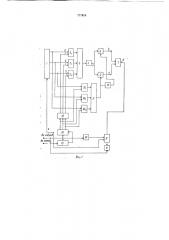

На фиг. 1 приведена функциональная схема устройства контроля ЦАП; на фиг.

2 — временные диаграммы, поясняющие его работу, Выходы разрядов датчика цифрового сигнала 1 через соответствующие вторые элементы И 21 — 2„, ЦАП 8, полосовой фильтр 4 соединены со входами первого 5 и второто б широтно-импульсных модуляторов (ШИМ), выходы которых через сумматор по модулю два 7 и блок объединения 8 подключены ко входу видеосигна"",à

ВКУ 9. Выход разрядов датчика цифрового сигнала 1 через соответствующие первые элементы И 101 — 10„, схему ИЛИ 11 соединены с управляющим входом первого

ШИМ 5 непосредственно и с управляющим входом второго ШИМ б через инвертор 12.

Вход строчных синхроимпульсов «Вх. строк» соединен со входом блока объединения 8, со входом датчика цифрового сигнала 1 и через делитель частоты 18, распределитель импульсов 14 — со входами соответствующих первых элементов И 10>—

10„, а также через дешифратор 15 — со входами соответствующих вторых элементов И 2i — 2„. Вход кадровых синхроимпульсов «Вх. кадров» соединен со входом кадровой синхронизации ВКУ 9 с управляющими входами делителя частоты 18 и распределителя импульсов 14 и, через формирующий блок lб — со входом блока ооъединения 8.

Устройство работает следу|ощим образом.

Импульсы с частотой строк телевизиочной развертки подаются на вход делителя частоты 18. Его коэффициент деления выбирается так, чтобы за цикл контроля можно было проконтролировать все разря5

65 ды ЦЛП 8 на экране ВКУ 9 . Например, при числе строк в полукадре телевизионной развертки N,, = 312,$ и числе разрядов кода n=8 контроль каждого разряда должен осуществляться в течение не более

N„, чем :=39 строк. Пусть контроль каждого разряда производится в течение 32 строк полукадра. Каждые 32 строки на выходе делителя частоты 18 появляется импульс, который поступает на распределитель импульсов 14. Распределитель 14 управляет первыми элементами И 10 — 10„ таким образом, чтобы на выход элемента

ИЛИ 11 поочередно (например, каждые 32 строки) проходили сигналы с выходов разрядов датчика цифрового сигнала 1.

Кроме того, распределитель 14 через дешифратор 15 управляет вторыми элементами И 21 — 2„таким образом, чтобы на входы разрядов ЦАП 8 подавалось монотонно увеличивающееся число разрядов с выхода датчика цифрового сигнала 1. Например, первые 32 строки подается 1-й разряд, вторые 32 строки — 1-й и 2-ой разряды и т. ь, последние 32 строки — все восемь разрядов Такой цифровой сигнал на входе ЦАП 8 соответствует последовательному (например, каждый 32 строки) удвоению числа ступенек пилообразного напряжения на выходе ЦАП 8. Сигнал с выхода

ЦАП 8 поступает на вход полосового фильтра (ПФ) 4. На выходе ПФ 4 в моменты перехода аналогового сигнала на выходе

ЦЛП 8 с одного уровня, квантования на другой появляется импульс, амплитуда которого пропорциональна величине интервала между соответствующими уровнями амплитудного квантования. Сигнал с выхода

ПФ 4 поступает на входы с|оответственно первого 5 и второго б ШИМ, где производится преобразование амплитудно-модулированного импульса в широтно-модулированный, причем ШИМ 5 обрабатывает четпыс импульсы с выхода ПФ 4, а ШИМ б— нечетные. Временное положение импульсов на входах ШИМ 5 и б определяется моментом смены кодовых комбинаций, подаваемых с выхода датчика цифрового сигнала 1 на входы ЦАП 8, а амплитуда определяется числом разрядов, подключаемых на входы ЦАП 8 кодовых комбинаций.

Число разцядов изменяется, например. каждые 32 строки. Таким образом, амплитуда импульсов на выходе ПФ 4 должна сохраняться постоянной в течение каждых

32 строк. Она соответствует величине кванта младшего коммутируемого разряда

ЦЛП 8. Изменение амплитуды импульсов на выходе ПФ 4 в течение данных, например 32, строк свидетельствует о погрешностях в работе ЦАП 8, связанных с отклонениями уровней амплитудного квантования ЦАП 8 от своих номинальных положений. Передний фронт широтно-модулиро777810

50 ванных импульсов на выходе преобразозателя 5(б) определяется моментами поступления четных (нечетных) амплитудномодулированных импульсов с выхода ПФ 4 на вход преобразователя 5(б) (фиг. 2}.

Задний фронт широтно-модулированных импульсов на выходе преобразователя 5(б) определяется амплитудой четных (нечетных) амплитудно-модулированных импульсов с выхода ПФ 4 на входе ШИМ 5(б) (фи г. 2). Если амплитуда импульсов на входе преобразователей 5 и б точно соответствует величине интервала между соответствующими уровнями амплитудного квантования, то длительность импульсов на выходах преобразователя 5 и 6 равна периоду поступления импульсов с выхода

ПФ 4 на входы ШИМ 5 и б. В этом случае на выходе сумматора по модулю два 7, ко входу, которого подключены выходы ШИМ 5 и 6, отсутствует сигнал ошибки. В противном случае возникает сигнал ошибки в виде широтно-модулированных импульсов, временное положение переднего фронта которых соответствует моменту появления импульсов на выходе ПФ 4, а заднего фронта — величине отклонения интервала между соответствующими уровнями амплитудного квантования ЦАП 8 от номинальной величины. Этот сигнал через блок объединения 8 подается на ВКУ 9. На блок объединения 8, кроме тото, подаются импульсы кадровой частоты от клеммы «вх. кадров» через формирующий блок 16 и импульсы строчной частоты от клеммы «вх. строк». Блок объединения 8 замешивает три сигнала: сигнал ошибки с выхода сумматора по модулю два 7, строчные синхроимпульсы и кадровые гасящие импульсы, поступающие от формирующего блока 16.

На выходе блока объединения 8 образуется телевизионный видеосигнал. Кроме того, импульсы кадровой частоты подаются непосредственно от клеммы «вх. кадров» на ВКУ 9 для обеспечения кадровой синхронизации.

Формула изобретения

Устройство контроля цифро-аналогового преобразователя, содержащее датчик цифрового сигнала, п-разрядный цифро-анало5

Зо

45 гс-ый п еобразователь, сумматор по модулю два, и первых элементов И, элемент

ИЛИ, распределитель импульсов, делитель частоты, формирующий блок, видеоконтрольное устройство и блок объединения, первый вход которого соединен с входом делителя частоты, входом датчика цифрового сигнала и с клеммой входа строчных имгульсов, второй вход блока объединения подключен через формирующий блок к клемме входа кадровых импульсов и ко входу кадровой синхронизации видеоконтрольного устройства, а также .к управляющим входам распределителя импульсов и делителя частоты, выход которого соединен с другим входом распределителя импульсов, третий вход блока объединения соединен с выходом сумматора по модулю два, выход датчика цифровых сигналов подключен к входам п первых элементов И, другие входы которых соединены с соответствующими выходами распределителя импульсов, выходы п первых элементов И подключены ко входам элемента ИЛИ, о тлии ч а ю щ ее ся тем, что, с целью повышения точности и качества контроля цифроаналогового преобразователя, в него дополнительно введены дешифратор, п вторых схем И, полосовой фильтр, два модулятора, инвертор, вход которого соединен с выходом элем нта ИЛИ и управляющим входом первого, модулятора, выход инвертора подключен к управляющему входу второго модулятора, входы дешифратора соединены с выходами распределителя импульсов, выходы дешифратора подключены к первым входам и вторых элементов И, вторые входы которых соединены с выходами датчика цифрово"îсигнала,,а г,ыходы и вторых элементов И подключены через цифро-аналоговый преобразователь к входам полосового фильтра, выход которого через первый,модулятор соединен с первым, а через второй модулятор — со вторым входом сумматора по модулю два.

Источник информации, принятый во внимание при экспертизе:

1. Кислицкий Н. Т., Коган С. С. Способы контроля аналого-цифровых и цифроаналоговых преобразователей сигналов изображения. Вопросы радиоэлектроники

Сер, ТПС, 1974, вып 6, с. о8, рис. 3 (прототип).

777816

Составитель А. Симагин

Техред И. Пенчко Корректор И. Осиповская

Редактор Б. Федотов

Заказ 14бб/147б Изд. ¹ 543 Тираж 995 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5

Тип. Харьк. фил, пред. «Патент»