Перестраиваемый делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

О П

Союз Советских

Социалистических

Республик (111777824

ИЗОБР ЕТЕ Н И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 26.12.78 (21) 2702759/18-21 (51) Ч.Кл.з Н 03 К 23/00 с присоединением заявкн— (23) Приоритет—

Государственный комитет по делам изобретений и открытий (53) УДК G21.377.44 (088.8) (43) Опубликовано 07.11.80. Бюллетень № 41 (45) Дата опубликования описания 04.12.80 (7, 2) Авторы язобр етен и я

A. В. Шанин и Е. С. Заводий (71) З,аяаитель (54) ПЕРЕСТРАИВАЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

СЛЕДОВАНИЯ ИМПУЛЬСОВ

Изобретение относится к цифровым делителям частоты следования импульсов и может быть использовано в цифровых синтезаторах частоты и устройствах синхронизации цифровых систем.

Известно устройство для деления частоты импульсов, содержащее счетчик, триггеры, вентили, инвертор и генератор эталонного сигнала (Ц.

Недостатком данного устройства является недостаточно высокая скорость измерения коэффициента .деления.

Известно также устройство, содержащее двоичный счетчик импульсов, включающий в себя буферный и информационный регистры и сумматор, формиро ватель синхроимпульсов, выходы которого соединены со входами синхронизации счетчика импульсов,,первый — непосредственно, а второй — через элемент И, инверторы, элементы И вЂ” ИЛ И, триггер, элемент ИЛИ и два элемента сравнения, первые входы первого из которых соединены с разрядными выходами счетчика импульсов, первые входы второго — с выходами элементов

И вЂ” ИЛИ, а,вторые входы обоих элементов сравнения — с шиной управления 12).

Недостатком данного устройства является сложность.

Целью изобретения является упрощение устройства. .Поставленная цель достигается тем, что

:в перестраиваемый делитель частоты следования импульсов, содержащий двоичный счетчик импульсов, формирователь синхроимпульсо в, первый:выход которого соединен с первым, входом синхронизации двоичного счетчика импульсов, а второй выход — непосредственно с первым .входом первого элемента И, второй вход которого подключен ко входу инвертора и выходу элемента сравнения, а через второй элемент И,,второй вход которого подключен к выходу инвертора, — со вторым входом синхронизации двоичного счетчика импульсов, разрядные выходы которого соединены с первыми входами элемента сравнения, .вторые входы которого подключены к кодовой ши20 не, элемент ИЛ И и триггер,,введены дополнительный элемент И и дополнительные триггеры, первый вход первого из которых соединен с шиной управления, второй вход — с выходом первого элемента И, пер25 вый выход — с первым установочным,входом двоичного счетчика импульсов и первым входом триггера и второй выход — со вторым установочным, входом счетчика импульсов и первым входом элемента ИЛИ, второй вход которого соединен с выходом

777824

j0

15 ю

3О

65 дополнительного элемента И, первый вход которого соединен с первым выходом формирователя синхроимпульсов, второй вход— с выходом триггера, второй вход которого соединен со вторым входом синхронизации д воичного счетчика импульсов, à выход элемента ИЛИ подключен ко входу второго дополнительного триггера.

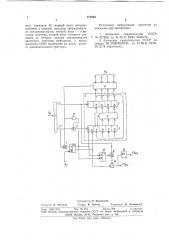

На чертеже представлена структур и", я электрическая схема устройства.

Оно содержит формирователь 1 синхроимпульсов, счетчик 2 двоичных импульсов, регистр 8 информационный двоичного счетчика имлульсов, регистр 4 буферный двоичного счетчика импульсов, сумматор б двоичного счетчика импульсов, элемент б сравнения, элементы И 7 — 9, инвертор 10, триггеры 11 —.И, элемент ИЛИ 14. Триггеры 11, 1З,выполнены со счетным входом.

Перестраиваемый делитель частоты следования импульсов работает следующим образом.

Частота 1.:, поступает на формирователь

1, на первом выходе которого формируется импульсная последовательность (Cl) с частотой и фазой, равными частоте и фазе ,входного сигнала f» а иа втором выходе— импульсная последовательность (С2) с частотой f „. отстающая по фазе на 180 (сдвинутая на величину Т,/3). В зависимости от формы входщого сигнала, конкретная реализация формирователя 1 может быть различной.

В исходном состоянии на выходе элемента б присутствует «нулевой» потенциал. запрещающиЙ прохождение синхроимпульсов С1 через элемент 7 и через инвертор 10 разрешающий прохождение Cl через элемент 8 на синхро вход (C) регистра 4.

С поступлением .каждого импульса Cl содержимое регистра (3 переписывастся 3 регистр 4, при этом,на выходе сумматора б формируется число,,равное сумме содержимого (n — 1) -го старших разрядов регистра

4 н значения первого разряда регистра 4 (все разряды — 2 =1).

Таким образом, с приходом каждого импульса серии С2 содержимое регистра 1 увеличивается на единицу по сравнениIO с предыдущим значением. При достижении содержимым регистра

3 величины Л „(целая часть .коэффициента деления относительно f",„., или старшие (и — 1) разряды коэффициента деления, относительно f д.ы„,,) срабатывает элемент б, и

«единичный» сигнал с его выхода запрещает прохождение Cl на С-.вход регистра 4 и разрешает прохождение С1 на счетный вход триггера 11. Реакция триггера 11 на воздействие сигнала С1 зависит от значения N, (дробная часть — 0,5 — коэффициента деления, относительно f"-,.,или первый разряд коэффициента деления относительно f D,) . EcJlh ; == О, 11 заблокирован по входу R, и на его первом выходе формируется импульс, поступающий Hà R- вход регистра 4 и обнуляющий его. Если N =,1, то триггер И .разблокирован, и при каждом срабатывании элемента б .импульс Cl, поступая на счетный вход триггера 11, переключает его в противоположное состояние и формируетна его выходах импульсы переноса. При этом ии7ульс переноса с первого выхода, поступая на вход R регистра 4, обнуляет его и ставит в «единичное» состояние триггер,12, разрешая при этом прохождение импульса

С2 через элемент 9, элемент,14 на выход (/"„,,) и выход триггера 13, формирующего выходной сигнал f „,, Импульс со второго выхода триггера 11 устанавливает «1» в первом разряде регистра 4 и через элемент

14 формирует сигнал f"„„,, а поступая на триггер 18, формирует на его выходе симметричный сигнал f . Таким образо.л, перестраи ваемыЙ делитель частоты формирует сигнал f = f„,. N,-... являющийся симметричным «меандром» при любом целом

N„„,è импульсный сигнал f" = f Уу:,г 2.

Таким образом, предлагаемая реализация перестраиваемого делителя частоты позволяет исключить элемент сравнения и элементы И вЂ” ИЛИ, объем которых прямо пропорционален числу разрядов счетчикаделителя импульсов, что, в свою очередь, сокращает объем оборудования устройства в целом и,ведет к упрощению устройства.

Формула изобретения

Перестраиваемый делитель частоты следования импульсов, содержащий двоичный счетчик импульсов, формирователь синхроимпульсов, первый выход которого соединен с первым входом синхронизации двоичного счетчика импульсов, а второй .вы од —,непосредственно с первым входом первого элемента И,,второй вход которого подключен ко входу инвертора и выходу элемента сравнения, а через второй элемент

И, второй вход которого подключен к выходу инвертора,— со вторым входом синхронизации двоичного счетчика импульсов, разрядные выходы которого соединены с первыми входами элемента сравнения, вторые входы, которого подключены к кодовой шине, элемент ИЛИ и триггер, о тл и ч а ю. щ и и ся тем, что, с целью упрощения уст,ройства, в него введены дополнительный элемент И и дополнительные триггеры, первый вход первого из которых соединен с шиной управления, второй вход — с выходом первого элемента И, .первый выход — с первым установочным входом двоичного счетчика .импульсов и первым, входом триггера и второй выход — со вторым установочным входом счетчика импульсов и первым входом элемента ИЛИ, второй вход которого соединен с выходом дополнитсль777824

Составитель О. Ь;ружилина

Техред И. Пеннко Корректор И. Осиповская

Редактор Б. Федотов

Заказ 1466/1476 Изд. № 543 Тираж 995 Подписное

HTIO «Поиск» Государственного комитета СССР по делам изобретений и открьггий

113035, Москва, Я-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент» ного элемента И, первый вход которого соединен с первым выходом формирователя синхроимпульсов, второй,вход — с вы. ходом триггера, второй вход которого соединен со вторым входом синхронизации двоичного счетчика импульсов, а выход элемента ИЛИ подключен ко входу второго дополнительного триггера.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 527826, кл. Н 03 К 23 34, 04.05.75.

2. Авторское свидетельство СССР по заявке № 2702759/18-21, кл. Н 03 К 23!00, 26.12.78 (прототип) .