Устройство проверки матриц коммутации

Иллюстрации

Показать всеРеферат

.1Я вЂ” 1т. в

З .

О П И С А Н -И -Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 08.01.79 (21) 2709566/18-09 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 07.11.80. Бюллетень № 41 (45) Дата опубликования описания 07.11.80 (51) M. Кл.

Н 04 М 3/22

Государственный комитет (53) УДК 621.395.66 (088.8) по делам изобретений и открытий (72) Авторы изобретения В. В. Бебрис, С. Н. Милейко, М. К, Сидяков и В. А. Цветков (71) Заявитель (54) УСТРОЙСТВО ПРОВЕРКИ МАТРИЦ КОММУТАЦИИ

Изобретение относится к телефонии и может быть использовано для проверки матриц коммутации при производстве и эксплуатации матричных соединителей (герконовых и др.) .

Известно устройство проверки матриц коммутации, содержащее генератор токовых импульсов, выход которого через коммутатор подключен к управлтпощим входам матрицы, генератор тактовых импульсов, выход которого через счетчик подключен к входу блока подключения испытательного сигнала, а вход соединен с первым выходом блока сравнения, первый вход которого подключен к второму входу счетчика, третий выход которого подключен к второму входу коммутатора и индикатор (1).

Однако в известном устройстве проверка матрицы занимает значительное время из-за того, что после включения (выключения) каждой точки проверяемой матрицы производится поочередная проверка состояний всех ее входов и выходов.

Цель изобретения — сокращение времени проверки.

Для этого в устройство проверки матриц коммутации, содержащее генератор токо, вых импульсов, выход которого через коммутатор подключен к управляющим входам матрицы, генератор тактовых импульсов, выход которого через счетчик подключен к входу блока подключения испытательного сигнала, а вход соединен с первым вы5 ходом блока сравнения, первый вход которого подсоединен к второму входу счетчика, третий выход которого подключен к второму входу коммутатора, индикатор, введены блок контроля состояния входов, блок контроля состояния выходов. При этом информационный выход матрицы через блок контроля состояния выходов подключен к второму входу блока сравнения, а выход блока подключения испытательных

15 сигналов подключен одновременно к информационному входу матрицы и через блок контроля состояния входов — к третьему входу блока сравнения, второй выход которого подключен к входу индикатора.

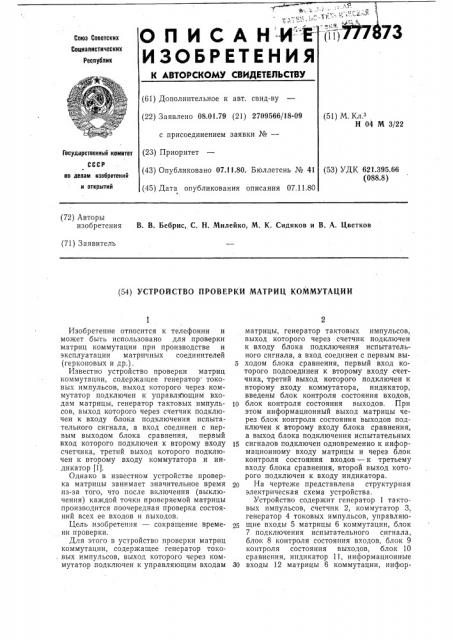

На чертеже представлена структурная электрическая схема устройства.

Устройство содержит генератор 1 тактовых импульсов, счетчик 2, коммутатор 3, генератор 4 токовых импульсов, управляющие входы 5 матрицы 6 коммутации, блок

7 подключения испытательного сигнала, блок 8 контроля состояния входов, блок 9 контроля состояния выходов, блок 10 сравнения, индикатор 11, информационные

30 входы 12 матрицы 6 коммутации, инфор777873

НПО «Поиск»

Тираж 729

Изд. № 579

Подписное

Заказ 2533/18

Типография, пр. Сапунова, 2 мационные выходы 13 MaTpH11bi 6 KOMM jта ции.

Устройство работает следующи м образом.

Сигнал с генератора 1 тактовых импуль- 5 сов подается на счетчик 2, который определяет координаты очередной включаемой точки кОммутации в матрице 6 коммутации. Эти координаты передаются на коммутатор 3, который подключает необходи- 10 мые входы 5 матрицы 6 коммутации к генератору 4. Одновременно блок 7 подключения испытательного сигнала подает сигнал на соответствующий вход 12 матрицы

6 коммутации. Блок 8 контроля состояния 15 входов и блок 9 контроля состояния выходов в каждый момент определяют номера информационных входов 12 и выходов 13 матрицы 6 коммутации, на которых присутствует испытательный сигнал, и выда- 20 ют информацию об этом на блок 10 сравнения. Если эта информация соответствует информации, поступающей на блок 10 сравнения со счетчика 2, блок 10 сравнения подает разрешающий сигнал на вход гене- 25 ратора 1 тактовых импульсов. По следующему тактовому импульсу проверяемая точка коммутации выключается.

Включается очередная точка коммутации и т. д. 30

Если сигналы на выходах блока 8 контроля состояния входов и блока 9 контроля состояния выходов не соответствуют сигналу на выходе счетчика 2, блок 10 сравнения останавливает генератор 1 тактовых импульсов, и проверка прекращается.

Состояние устройства и проверяемой матрицы 6 отображает индикатор 11.

Таким образом, предлагаемое устройство позволяет проверить состояние матрицы коммутации за один такт, т. е. после включения (или выключения) проверяемой точки коммутации не требуется дополнительных переключений, за счет чего сокращастся время проверки матрицы в целом, Формула изобретения

Устройство проверки матриц коммутации, содержащее генератор токовых импульсов, выход которого через коммутатор подключен к управляющим входам матрицы, генератор тактовых импульсов, выход которого через счетчик подключен к входу блока подключения испытательного сигнала, а вход соединен с первым выходом блока сравнения, первый вход которого подсоединен к второму входу счетчика, третий выход которого подключен к второму входу коммутатора, и индикатор, отличающееся тем, что, с целью сокращения времени проверки, введены блок контроля состояния входов и блок контроля состояния выходов, при этом информационный выход матрицы через блок контроля состояния выходов подключен к второму входу блока сравнения, а выход блока подключения испытательных сигналов подключен одновременно к информационному входу матрицы и через блок контроля состояния входов — к третьему входу блока сравнения, второй выход которого подключен к входу индикатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 439075, кл. H 04 М 3/22, 1972 (прототип).