Устройство коррекции фазы

Иллюстрации

Показать всеРеферат

Ъ

-е;lf) о.

ОП ИСЛ Й-"—

ИЗОБРЕТЕНИЯ

* jt

- 1) 777882, Союз Советски«

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 24.01.79 (21) 2731770/1 8-09 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано 07.11.80. Бюллетень ¹ 41 (45) Дата опубликования описания 07.10.80 (51) М. Кл.з

Н 04L 7/04

//H 04| 25/36

Государствеиимй комитет (53) УДК 621.394.662 (088.8) ло делам изобретений и от«ритий (72) Авторы изобретения

А. И. Ворожко, Л. А. Шарейко, Г. В. Тандилашвили и В. В. Бачериков (71) Заявитель (54) УСТРОЙСТВО КОРРЕКЦИИ ФАЗЪ|

Изобретение относится к связи и может использоваться в аппаратуре синхронизации приема цифровой информации.

Известно устройство коррекции фазы, содержащее последовательно соединенные задающий генератор, делитель частоты и блок выделения синхроимпульсов, причем к другому входу делителя частоты подключен выход блока установки делителя частоты в исходное состояние, а также входной триггер и элемент И (1) .

Однако известное устройство имеет недостаточную помехоустойчивость.

Цель изобретения — повышение устойчивости.

Для этого в устройство коррекции фазы, содержащее последовательно соединенные задающий генератор, делитель частоты и блок выделения синхроимпульсов, причем 20 к другому входу делителя частоты подключен выход блока установки делителя частоты в исходное состояние, а также входной триггер и элемент И, введены последовательно соединенные счетчик импульсов, до- 25 полнительный элемент И и элемент ИЛИ, а также блок разрешения синхронизации, при этом информационный вход входного триггера объединен с другим входом дополнительного элемента И и с первым входом 30 элемента И, выход которого подключен через элемент ИЛИ к входу блока установки делителя частоты в исходное состояние, выход которого подключен к одному из входов счетчика импульсов, к другому входу которого подключен выход входного триггера, а другой выход делителя частоты через блок разрешения синхронизации подключен к управляющему входу входного триггера и к второму входу элемента И.

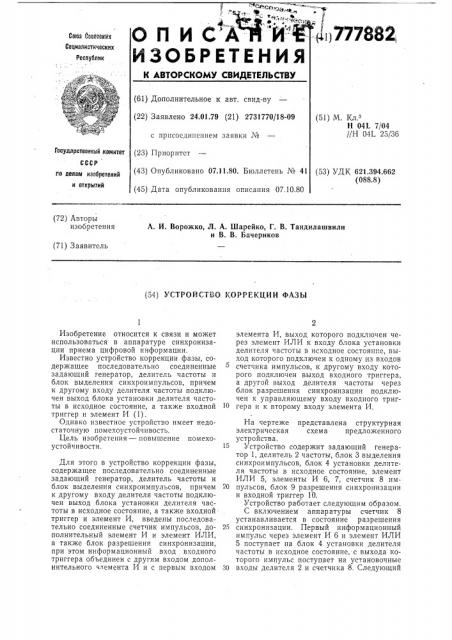

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство содержит задающий генератор 1, делитель 2 частоты, блок 3 выделения синхроимпульсов, блок 4 установки делителя частоты в исходное состояние, элемент

ИЛИ 5, элементы И 6, 7, счетчик 8 импульсов, блок 9 разрешения синхронизации и входной триггер 10.

Устройство работает следующим образом.

С включением аппаратуры счетчик 8 устанавливается в состояние разрешения синхронизации. Первый информационный импульс через элемент И 6 и элемент ИЛИ

5 поступает на блок 4 установки делителя частоты в исходное состояние, с выхода которого импульс поступает на установочные входы делителя 2 и счетчика 8. Следующий информационный импульс придет на элемент И 7 в момент времени, когда на второй вход элемента И 7 поступит с блока 9 разрешения синхронизации сигнал разрешения синхронизации в виде импульса постоянного тока, длительность которого выбирается больше, чем флуктуация фазы между двумя информационными посылками в процессе работы. С выхода элемента И 7 информационный сигнал через элемент

ИЛИ 5 поступает на вход блока 4 установки делителя в исходное состояние. B случае прихода помехи или серии помех по информационному входу они устанавливают в состояние «1» триггер 10, который формирует импульс постоянного тока, и в счетчик

8 записывается «1». С приходом информационного импульса счетчик 8 устанавливается в исходное состояние. В случае нарушения синхронизма счетчик 8 заполняется, 20 и следующий информационный импульс поступает на вход блока 4 установки делителя в исходное состояние, который вводит устройство в режим синхронизации и устанавливает счетчик 8 в исходное состояние.

Таким образом, воздействие по информационному входу помехи или серии помех в заявляемом устройстве не вызывает сбоя синхронизации по сравнению с прототипом, 0 что повышает помехоустойчивость устройства в целом.

Формула изобретения

Устройство коррекции фазы, содержащее посредовательно соединенные задающий генератор, делитель частоты и блок выделения синхроимпульсов, причем к другому входу делителя частоты подключен выход блока установки делителя частоты в исходное состояние, а также входной триггер и элемент И, отличающееся тем, что, с цель1о повышения помехоустойчивости, введены последовательно соединенные счетчик импульсов, дополнительный элемент И и элемент ИЛИ, а также блок разрешения синхронизации, при этом информационный вход входного триггера объединен с другим входом дополнительного элемента И и с первым входом элемента И, выход которого подключен через элемент ИЛИ к входу блока установки делителя частоты в исходное состояние, выход которого подключен к одному из входов счетчика импульсов, к другому входу которого подключен выход входного триггера, а другой выход делителя частоты через блок разрешения синхронизации пбдключен к управляющему входу входного триггера и к второму входу элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 294264, кл. Н 04L 25/36, 1971 (прототип), Подписное

Заказ 2530/15

Изд. № 577 Тираж 729

Типография, пр. Сапунова, 2