Усилитель считывания для программируемого постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских.

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТИЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 29. 11. 76 (21) 2425295/18-24 (51) М. Кл. с присоединением заявки Мо

G 11 С 7/00

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 151180. Бюллетень Мо 42

Дата опубликования описания 15. 11. 80 (53) УДК681 327 6 (088.8) (72) Авторы изобретения

Ю. И. Шетинин, В.A. Неклюдов, В. В. Воробьева, П.С. Приходько и В.A. Мнтйна (7 t ) Заявитель

1 (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ ДЛЯ ПРОГРАММИРУЕМОГО

ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

--...t

Изобретение относится к области вычислительной техники, и в частности, к интегральным полупроводниковым постоянным запоминающим устройствам.

Известны интегральные постоянные запоминающие устройства, имеющие усилители считывания с инверсией или без инверсии сигналов запоминающей матрицы j1J .

Такое построение выходных усилителей накладывает ограничение на надежность постоянных эапоминающихустройств (ПЗУ).

В ПЗУ запись информации заключается в создании избирательного ри- . сунка соединений элементов запоминающей матрицы с разрядными шинами. Наличие соединения соответствует логической единице (нулю) на выходе усилителя считывания. Количество нулей и единиц существенно отличается в каждом разряде. С точ- ки зрения надежности, целесообразно выбирать фазу выходного сигнала таким образом, чтобы обеспечить минимальное подключение элементов матрицы ПЗУ.

В электрически программируеьых постоянных ЗУ (ППЗУ) изменение фаI

2 зы выходного сигнала дает возмож- . ность изменить состояние минимального количества программируемых элементов матрицы, что приводит

5 не только к повышению надежности, но и к уменьшению времени записи информации и увеличению процента выхода годных запрограммированных

ППЗУ. Надежность в большой степени

10 зависит от количества запрограммированных элементов. Так как каждый запрограммированный элемент имеет определенную вероятность восстановления своего прежнего состояния, 15 то чем больше таких элементов в матрице, тем больше вероятность отказа схемы ППЗУ. Время записи информации находится s прямой зависимости отколичества программируемых элемен2О тов, меняющих свое состояние. В процессе записи практически все узлы схемы ППЗУ работают в предельных режимах.

Чем больше время записи, тем больше вероятность выхода из строя какого25 либо узла или элемента схемы, что определяет процент брака при программировании.

Наиболее близким техническим решением является усилитель считываЗр ния, .состоящий иэ двух последователь780033

25 но включенных инверторов, каждый из которых имеет свою выходную контактную площадку на кристалле pj . В процессе сборки к выходной клемме ,корпуса подключается один из выходов усилителя считывания в соответствии с записываемой информацией.

Если для масочных ПЗУ такое решение является приемлемым, то для электрически программируемых ПЗУ целесообразно иметь усилитель считывания также с электрическим изменением фазы © выходного сигнала, что приводит к повышению надежности, уменьшению времеЙи записи информации и увеличению выхода годных ППЗУ.

Целью изобретения является повыше- 13 ние надежности усилителя считывания за счет изменения фазы выходного сигнала электрическим способом после завершения цикла изготовления большой интегральной схемы (БИС). 20

Эта цель достигается тем, что усилитель считывания для интегрального программируемого постоянного за. поминающего устройства, содержащий управляющий, фазорасщепительный, выходной транзисторы, три резистора, входную и выходную шины, шину питания и шину нулевого потенциала, причем эмиттер управляющего транзистора соединен с входной шиной, база через первый резистор с шиной питания, а коллектор с базой фазорасщепительного транзистора, коллектор которого соединен через втоРой РезистоР с шиной питания, эмиттер с базой выходного транзистора и через третий резистор с шиной нулевого потенциала, эмиттер выходного транзистора соединен с шиной нулевого потенциала, а его коллектор с выходной шиной содержит инвертирую- 40 щий транзистор, пороговый элемент, программируемый элемент, два источника напряжения смещения, четвертый и пятый резисторы, причем коллектор инвертирующего транзистора соединен 45 с коллектором управляющего транзистора, с базой фазорасщепительного транзистора и через четвертый резистор с шиной питания, база инвертирующего транзистора соединена с эмитте- у» ром управляющего транзистора, с входной шиной и через пятый резистор с шиной питания, а эмиттер с базой уп " равляйи4его транэистора и с положительным полюсбм первого источника напряжения смещения, отрицательный полюс которого соединен через программируемый элемент с шиной нулевого потенциала и с выходом порогового элемента,- вход которого соединен с коллектором выходного транзистора и 60 выходной шиной, эмиттер фазорасщепи-тельного транзистора соединен с положительным полюсом второго источника напряжения смещения, положительный полюс которого соединен с базой вы- 5 ходного транзистора и через третий резистор с шиной нулевого потенциала.

Программируемый элемент выполнен в виде плавной перемычки. Программируемый элемент выполнен в виде обратносмещенного р-п перехода.

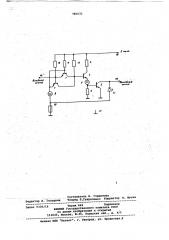

На чертеже дана электрическая схема усилителя считывания, содержащего управляющий транзистор 1, фазовращательный транзистор 2, выходной транзистор 3, первый Резистор 4, второй резистор 5, третий резистор б, инвертирующий транзистор 7, первый источник 8 напряжения смещения, второй источник 9 напряжения смещения, программируемый элемент 10, пороговый элемент 11, четвертый резистор

12, пятый резистор 13, входную шину

14, выходную шину 15, шину 1б питания, шину 17 нулевого потенциала.

Программируемый элемент 10 может быть выполнен любым известным способом: плавкая перемычка, обратно смещенный р-п переход и т.д. Программируежий элемент 10 может иметь два состояния: низкое и высокое сопротивление. Для плавкой нихромовой перемычки эти состояния определяются сопротивлением 100 Ом и более 1 Мом соответственно.

В начальном состоянии перемычка имеет низкое сопротивление.

В этом состоянии управляющий транзистор закрыт при любОм сигнале на входной шине, а инвертирующий транзистор инвертирует входной сигнал, который вторично инвертируется выходным транзистором 3.

При лог. "0" на входной шине 14 необходимо обеспечить закрытое состояние транзисторов 1 и 3.. В зависимости от уровня логического "0" входного сигнала смещающее напряжение (0См) выбирается из следующего

1 условия:

О Еп "см

0 -0- и ех оэср R + Р

Il .ЭЛ.+ СМ > пр. Эл где U о

sx напряжение логическо

Ъ го "0" на входной шине;

0 — падение напряжения на переходе база-эмиттер

Ьэъ открытого инвертирующего транзистора 7;

- напряжение на шине питания; В р ЭЛ - сопротивленне програмпр.э . мируемого элемента в пров одяи(ем : состоянии .

При таком соотношении напряжений при малом сопротивлении программируемого элемента сигнал разрядной шины будет появляться на выходе усилителя считывания без инверсии.

Напряжение второго источника смещения выбирается из условия согла780033 сования уровней входной и выходной цепи убилителя считывания. В частности, источники 8 и 9 могут быть равными.

Для того, чтобы изменить фазу сигнала входной шины, достаточно привести программируемый элемент в состояние высокого сопротивления. Инвертирующий транзистор 7 будет закрыт при любом сигнале на входной шине, а транзистор 1 будет выполнять функцию управляющего транзистора в инвертирующем каскаде на транзисторах 1-3.

Изменение состояния нрограммируемого элемента происходит при подаче импульса тока на выходную шину 15 усилителя считывания через пороговый элемент 11.

Таким образом, предлагаемая схема позволяет менять фазу выходного сигнала после сборки в корпус микросхемы непосредственно самими заказчиками, что приводит к повышению надежности, уменьшению времени записи информации и увеличению процента выхода годных ППЗУ в процессе программирования.

Усилитель считывания может быть выполнен по обычной планарной технологии, используемой при производстве полупроводниковых электрически программируемых постоянных запоминающих устройств.

Формула изобретения

1. Усилитель считывания для программируемого постоянного запоминающего устройства, содержащий управляющий, фазорасщепительный, выходной транзисторы, три резистора, входную и выходную шины, шину питания и шину нулевого потенциала, причем эмиттер управляющего транзистора соединен с входной шиной, база через первый резистор с шиной питания, а коллектор с базой фазорасщепительного транзистора, коллектор которого соединен через второй резистор — с шиной питания, эмйттер с базой выходного транзистора и через третий резистор с шиной нулевого потенциала, эмит - тер выходного транзистора соединен с шиной нулевого потенциала, а его кол . лектор с выходной шиной, о т л ич а ю шийся тем, что, с целью повышения надежности усилителя,он содержит инвертирующий транзистор, пороговый элемент, программируемый элемент,два источника напряжения смещения, четвертый и пятый резисторы, причем коллектор инвертирующего транзистора соединен с коллектором управлякиаего транзистора, с базой фазорасщепительного транзис15 тора и через четвертый резистор с шиной питания, база инвертирующего транзистора соединена с эмиттером управляющего транзистора, с входной шиной и через пятый резистор с шиной щ питания, а эмиттер с базой управляю- . щего транзистора и с положительным полюсом первого источника напряжения смещения, отрицательный полюс которого соединен через программируемый элемент с шиной нулевого потенциала и с выходом порогового элемента, вход которого соединен с коллектором выходного транзистора и выходной шиной, эмиттер фазорасщепительного транзистора соединен с положительным полюсом

M второго источника напряжения смещения, положительный полюс которого соединен с базой выходного транзистора и через третий резистор с шиной нулевого потенциала.

35 2. Усилитель по п.1, о т л ич а ю шийся тем,,что программируемый элемент выполнен в виде плавкой перемычки.

3. Усилитель по п.1, о т л и4О ч à ю щ и и ся тей, что программируемый элемент выполнен в виде обратногс смещенного р-п перехода.

Ис точ ники и нформаци и, принятые во внимание при экспертизе

1. Electronic Оеь!дп, 13, 1973.

2. Патент CQIA,êë. 340-173.5, В 3721964, 1974 (прототип).

780033

АааЖ е у

4 cIAf фУ

Составитель В. Гордонова

Техред Й,Гаврилещко Корректор И. Муска

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Редактор Л. Гольдина

Заказ 9330/16 Тираж 662 . - Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035у Москва, Ж-35, Раушская наб., д. 4/5