Устройство регенерации информации для динамического блока матричной памяти

Иллюстрации

Показать всеРеферат

(1)780035

Союз Советских

Социалистических республик

ОПИСАНИЕ

ИЗОБРЕТЕЦИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (61 ) Дополнительное к ввт. саид-ву (51)М. Кл З (22) Заявлено 27. 12. 78 (21) 2703321/18-24

G 11 С 7/00 с присоединением заявки №

Государственный комитет

СССР яо делам изобретений н открытий (23) Приоритет

Опубликовано 151180, Бюллетень ¹ 42

Дата опубликования описания 15. 11. 80 (53) УДК 681. 327 (088.8) (72) Авторы изобретения

Е.Я. Ваврук, A.Н. Елагин, В.С. Жижин, В.E. Тимофеенко и A.À. Филимонов (71) Заявитель (54) УСТРОЙСТВО РЕГЕНЕРАЦИИ ИНФОРМАЦИИ

ДЛЯ ДИНАМИЧЕСКОГО БЛОКА МАТРИЧНОЙ

ПАМЯТИ.

Изобретение относится к области запоминающих устройств и может быть использовано в динамических запоминающих устройствах.

Известно устройство регенерации информации для динамического блока матричной памяти, содержащее коммутатор адреса, одни входы которого подключены к входу устройства, а другие — к выходам счетчика адреса регенерации (11 .

Недостатком этого устройства явля.ется невысокое быстродействие.

Наиболее близким техническим решением к изобретению является устройство регенерации информации для динамического блока матричной памяти, содержащее адресный блок, дешифратор строк, элементы памяти, блок синхронизирующих импульсов, причем одни входы адресного блока подключены к входным адресным шинам, управляющий вход подключен к первому выходу блока синхронизирующих импульсов, а выходы соединены с выходными адресными шинами устройства и входами дешифратора строк, стробирующий вход которого подключен ко второму выходу блока синхрониэирующих импульсов, а выходы соединены со входами установки единицы элементов памяти (2 .

Йедостатками .этого устройства являются удвоенная частота следования запросов на регенерацию, большое время ожидания окончания регенерации, в худшем случае равное времени регенерации всего объема памяти запоминающего устройства, поскольку ре10 генерация информации выполняется путем последовательного перебора адресов строк. Эти недостатки устройства приводят к снижению его быстродействия. !

5 Целью изобретения является повы» шение быстродействия устройства.

Поставленная цель достигаеся тем, что устройство содержит счетчйк адреса регенерации, дваяфратор адре20 са регенерации и коммутатор, причем выходы счетчика адреса регенерации подключены к другим входам адресного блока, к адресным входам коммутатора и дешифратора адреса регенерации, стробирующий вход которого подключен к третьему выходу блока синхрониэирукхдих импульсов, а выходы подключены к входам установки нуля элементов памяти, выходы которых соеди30 нены с информационными входами комму780035 татора, выход которого подключен к входу блока синхронизируюцих импуль-, cos, четвертый выход которого соединен с входом счетчика адреса регене.рации.

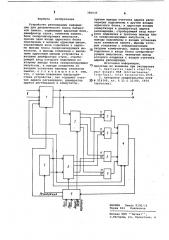

На чертеже изображена блок-схема предложенного устройстна.

Устройство содержит адресный блок 1, дешифратор 2 строк, элементы

3 памяти, коммутатор 4, счетчик 5 адреса регенерации, дешифратор 6 адреса регенерации, блок 7 синхрониэируюцих импульсов, имеюций входы

ВПУСК, СБРОС и ЗАПРОС РЕГЕНЕРАЦИИ, входные адресные шины 8, выходные адресные шины 9, входы 10 установки нуля и входы 11 установки единицы 15 элементов 3 памяти.

Одни входы адресного блока 1 подключены к входным адресным шинам 8, другие входы — к выходам счетчика 5 адреса регенерации, адресным входам 20 коммутатора 4 и дешифратора 6 адреса регенерации, управляющий вход подключен к первому выходу блока 7 синхронизируюцих импульсов, а выходы соединены с выходными адресными шинами 9 25 устройства и входами дешифратора 2 строк. Стробирующий вход дешифратора

2 строк подключен к второму выходу блока синхронизирующих импульсов 7, а выходы соединены с входами 11 уста- З нонки единицы элементов 3 памяти.

Стробирующий вход дешифратора 6 адреса регенерации подключен к третьему выходу блока 7 синхрониэируюцих импульсов, а выходы подключены к входам 10 установки нуля элементов 3 памяти, выходы которых соединены с информационными входами коммутатора 4.

Выход коммутатора 4 подключен к входу блока синхронизирующих импульсов 7, четвертый выход которого соединен с 4G входом счетчика 5 адреса регенерации.

Устройство работает следуюцим образом.

На вход блока 7 синхронизирующих импульсов постуйают сигналы СБРОС, 45

ПУСК и ЗАПРОС РЕГЕНЕРАЦИИ. По сигналу СБРОС блок 7 синхронизирующих импульсов устанавливается н исходное состояние, а элементы 3 памяти — в состояние "0 ". Если нет запросов на регенерацию, то производится работа на запись (считывание), и на управляющий вход адресного блока 1 с выхода блока 7 синхронизирующих

-импульсов не поступает сигнал РЕГЕНЕРАЦИЯ. При этом адресный блок 1 коммутирует содержимое входных адресных шин 8 на выходные адресйые шины

9. С приходом сигнала ПУСК блок 7 синхронизирующих импульсов формирует строб, по которому дешифратор 2 g) строк устанавливает один из элементов

3 памяти в состояние "1". Таким образом производится запоминание строки, к которой производилось обращение.

Коммутатор 4 коммутирует в соответствии с кодом адреса регенерации, поступающим с выходов счетчика адреса регенерации 5, выход одного иэ элементов 3 памяти на вход блока 7 синхронизирующих импульсов.

С приходом сигнала ЗАПРОС РЕГЕНЕРАЦИИ блок 7 анализирует выходной сигнал коммутатора 4. Если с выхода коммутатора 4 поступает сигнал "0", то блок 7 формирует сигнал РЕГЕНЕРАЦИЯ, по которому адресный блок 1 коммутирует содержимое счетчика 5 адреса регенерации на выходные адресные шины 9, и производится один цикл регенерации. Одновременно блок 7 синхронизируюцих импульсов формирует строб, по которому дешифратор 6 адреса регенерации обнуляет один из элементов 3 памяти. Причем, если производится регенерация 1-й строки, то обнуляется элемент 3 памяти, соотN нетствующий строке 1 + вЂ, где Й вЂ” количество строк блока памяти (после строки N идет строка 1, т.е. имеет место циклический перенос).

По окончании цикла регенерации сигнал РЕГЕНЕРАЦИЯ снимается, а к содержимому счетчика 5 адреса регенерации прибавляется единица.

Если с приходом сигнала ЗАПРОС

РЕГЕНЕРАЦИИ на ныходе коммутатора

4 стоит "1", то формирование сигнала РЕГЕНЕРАЦИЯ блокируется, цикл ре- генерации не производится, вырабатывается строб, по которому дешифратор

6 адреса регенерации обнуляет соответствующий элемент 3 памяти, а затем к содержимому счетчика 5 адреса регенерации прибавляется единица.

Таким образом, по одному Запросу на регенерацию производится один цикл регенерации, если за последний

2 период времени — Т p (Т р — допустимое время хранения информации в динамическом запоминающем устройстве) к данной строке не произ— водилось обращение. Это снижает максимальное время ожидания окончания регенерации по длительности одного цикла регенерации.

Сигналы ЗАПРОС РЕГЕНЕРАЦИИ посту2 пают с периодом 3НТ р т.е. каждая строка регенерируется с периодом

3 ехнико-экономическое преимущество описываемого устройства заключается в том, что в нем максимальное время ожидания окончания регенерации информации снижено до длительноСти одного цикла регенерации,что повышает быстродействие устройства и, при применении его в вычислительной системе, исключает конфликтные ситуации между процессором и динамическим блоком матричной памяти.

780035

Формула изобретения

Устройство регенерации информации для динамического блока матричной памяти, содержащее адресный блок, дешифратор строк, элементы памяти, блок синхронизирующих импульсов, причем одни входы адресного блока подключены к входным адресным шинам, управляющий вход подключен к первому выходу блока синхронизирующих импульсов, а выходы соединены с выходными адресными шинами устройства и входами дешнфратора строк, стробирующий вход которого подключен ко второму выходу блока синхронизирующих импульсов, а выходы соединены со входами установки единицы элементов памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит счетчик адреса регенерации, дешифратор адреса регенерации и коммутатор, причем выходы счетчика адреса регенерации подключены к другим входам адресного блока, к адресным входам коммутатора и дешифратора адреса регенерации, стробирующий вход кото5 рого подключен к третьему выходу бло ка синхронизирукиаих импульсов, а выходы подключены к входам установки нуля элементов памяти, выходы кото. рых соединены с информационными входами коммутатора, выход которогб подключен к входу блока синхронизи-. рующих импульсов, четвертый выход которого соединен с входом счетчика адреса регенерации.—

Источники информации, 15 принятые во внимание при экспертизе

1. Application report simplify

your dynamIc RA8 (microprocessor

interface), inteI Corporation, 1976.

2. Авторское свидетельство СССР

20 is 514346, кл. G 11 С 21/00, 1974 (прототип).

9330/16

Тирам 662 Подписное

Филиал ППП Патент, г,Умгород, ул, Проектная, 4