Регистр сдвига

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ о>780046

Ф

// (61) Дополнительное к авт. саид-ey— (22) Заявлено 25 ° 12. 78 (21) 2700914/18-24 (51)М. Кл. с присоединением заявки ¹â€”

G i1 С 19/00

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 151180.Бюллетень № 42 (53) УДК681. 327. 66 (088.8) Дата опубликования описания 181180 (72) Автор изобретения !

Д.В.Пуцыкович (71) Заявитель (54) РЕГИСТР СДВИГА так как вычислительные устройства, как правило, работают в условиях воздействия различных помех, а длительность периода между посылками двух последовательных слов обычно на порядки выше длительности самого слова. При этом следует иметь ввиду, что в целом ряде случаев появление на выходе регистра неправильной информации даже в одном такте является недопустимым, а пропуск одного такта не вносит существенной ошибки.

Таким образом, целью изобретения является повышение помехозащищенности.

Поставленная цель достигается тем, что в регистр сдвига, содержащий последовательно соединенные ячейки памяти, управляющие входы которых соединены с шиной управления сдвигом информации, выходы ячеек памяти подключены к одним из входов первых элементов И, выходы которых соединены с выходами регистра сдви25 га, информационные входы последней ячейки памяти соединены с входами регистра сдвига, введены счетчик импульсов, два генератора одиночных импульсов, второй и третий элементы

И и элемент НЕ, вход которого соеди-1

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных устройствах.

Известен регистр сдвига, содержащий h разрядов, цепь управления сдвигом информации, генератор импульсов, соединенный с выходными элементами И (1).

Наиболее близким из известных по технической сущности является регистр сдвига, содержащий в каждом разряде статический триггер с двумя элементами И, а также выходные элементы И по числу разрядов, цепь последовательной входной информации и цепь сдвига j2).

Однако недостатками известных регистров является низкая помехозащищенность, так если в цепи сдвига появляется импульс помехи, амплитуда.которого превышает порог срабатывания логических элементов, то на параллельных выходах регистров появляется неправильная информация, так как импульс помехи сдвигает на один разряд последовательную информацию, занесенную в регистр во время последнего такта записи,, Вероят1 ность такого события весьма велика, .

78004б нен с одним из входов второго элемента И и выходом первого генератора одиночных импульсов, выход элемента НЕ подключен к одному из входов третьего элемента И, выход которого соединен с входом первого генератора одиночных импульсов, другие входы второго и третьего элементов

И соединены с шиной управления сдвигом информации, выход второго элемента И подключен к первому входу счетчика импульсов, выход счетчика импульсов соединен с входом второго генератора одиночных импульсов, выход которого подсоединен к другим входам первых элементов И и вторым входам счетчика импульсов.

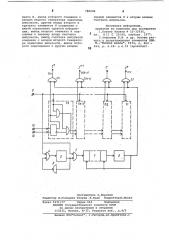

На чертеже представлена функциональная схема предложенного регистра сдвига.

Он содержит ячейки 1.1-1,п памяти, первые элементы И 2.1-2.п> второй и третий элементы И 3 и 4, первый и второй генераторы 5 и б одиночных импульсов, счетчик 7 импульсов, элемент HE 8, шину 9 управления сдвигом информации, входы 1 О, выходы 11.1-11п.

Устройство работает следующим образом.

На вход 10 поступает информация в виде последовательных и-разрядных слов. Для записи этой информации на шину 9 управления сдвигом информации подаются пачки из сдвиговых импульсов. Предполагается, что число разрядов (и сдвиговых импульсов) и — четное. Длительность периода между двумя словами — Т, длительность ймпульса сдвига — t> расстояние между импульсами сдвига — с .Как правило, t и, составляют доли или единицы микросекунды, и

T»P

1 сдвиговых импульсов.

Запись входной информации в разряды 1.1-1.п регистра происходит так же > как и в прототипе. Но передача информации на параллельные входы 10 регистра производится, . после анализа сдвиговых импульсов. Б исходном сбстоянии на входе генератора 5 присутствует "логический нуль", а на входе элемента И 4 - " логическая единица". Первый сдвиговой импульс поступает на вторые входы элементов

И 3 и 4 и .через элемент И 3 своим задним фронтом запускает генератор

5, который вырабатывает одиночный импульс такой длительности, чтобы его задний фронт окончился после окончания второго сдвигового импульса, но до прихода 3-ro сдвигового импульса. Импульс с выхода генератора 5 (его амплитуда равна "логической единице") поступает на первый вход элемента И 3, разрешая прохож дение на его выход (и на счетййй

Регистр сдвига, содержащий последовательно соединенные ячейки памяти, управляющие входы которых соединены с шиной управления сдвигом информации, выходы ячеек памяти подключены к одним из входов первых элементов

И, выходы которых соединены с выходами регистра сдвига, информационные входы последней ячейки памяти соединены с входами регистра сдвига, отличающийся тем, что, с целью повышения помехозащищенности, в него введены счетчик и>лпульсов, два генератора"одиночных импульсов, второй и третий элементы И и элемент

НЕ, вход которого соединен с одним из входов второго элемента И и выходом первого генератора одиночных

>1мпульсов, выход элемента HE подключен к одному из входов третьего эле50

55 бО

35 вход счетчика 7) второго сдвигового импульса. На это время элемент

И 4 закрыт по второму входу через элемент HE 8. Далее на вход элемента

И 4 поступает третий сдвиговой импульс, генератор 5 снова запускается и разрешает прохождение на вход счетчика 7 четвертого сдвигового импульса и т.д. Благодаря этому, на вход счетчика 7 поступает и/2 сдвиговых импульсов, после чего на выходе счетчика 7 появляется сигнал, запускающий генератор б, который вырабатывает импульс, разрешающий прохождение информации из разрядов

1.1-1.п регистра на входы регистра сдвига через элементы И 2.1-2,п.

Одновременно происходит обнуление счетчика 7.

Таким образом, передача информации на выход регистра сдвига происходит толькс в том случае, если на шину управления 9 поступает и импульсов, расстояние между которыми не превышает известное расстояние между импульсами сдвига в пачке.

Поскольку период повторения пачек много больше расстояния между импульсами в пачке, то появление импульса помехи, отделенного от пачки расстоянием, равным или меньшим расстояния между импульсами пачки, представляется маловероятным. Следовательно, при поступлении на шину 9 управления импульсов помехи межцу пачками сдвиговых импульсов на выход регистра не будет выдаваться неправильная информация, занесенная в предыдущем такте.

По предложенной схеме был изготовлен и испытан лабораторный макет регистра сдвига. Испытания подтвердили вь1сокую помехоустойчивость макета: при подаче на информационный и сдвиговой входы регистра специально организованных импульсов помех на его выходе не наблюдалось ложной информации.

Формула изобретения

780046

Составитель A.Âoðîíèí

Редактор Л.Гольдина Техред, Н.Граб Корректор И.Муска

Заказ 9331/17 Тираж 662 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, R-35, Раушская наб., д.4/5

Филиал ППП"Патент", r.Óæãoðîä,óë.Ïðîåêòíàÿ,4 мента И, выход которого соединен о входом первого генератора одиночных импульсов, другие входы второго и третьего элементов И соединены с шиной управления сдвигом информации, выход второго элемента И подключен к первому входу счетчика импульсов, выход счетчика импульсов соединен с входом второго генератора одиночных импульсов, выход которого подсоединен к другим входам первых элементов И и вторым входам счетчика импульсов.

Источники инФорМации, принятые во внимание при экспертизе

1.Патент японии Р 52-32935, кл. G 11 С 19/00, опублик. 1977.

2.Анисимов Б.В. и др. Основы расчета и проектнрования элементов UBR.

М.,"Высшая школа", 1974, с, 263

264, р. 6.18- и 6.19 (прототип).