Цифровой частотный дискриминатор

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцналнстнческнк

Республик

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву (22) Заявлено 1404.78 {21) 2605805/18-09

М Клз с присоединением заявки Но

Н 03 0 13/00

Госудврствеиный комитет

СССР ио делам изобретений н открытий (23) Приоритет

Опубликовано 151,80. Бюллетень Мо 42

1 .(53) УДК 621. 376. . 33 (088. 8) Дата опубликования описания 18.11,80 (72) Авторы изобретения

Д.И. Попов и Л ° А ° Страхова (71) Заявитель

Рязанский радиотехнический институт (54) ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР

Изобретение относится к радиолокации и может использоваться в цифровых, устройствах измерения частоты.

Известен цифровой частотный дискриминатор, выполненный.по двухканальной схеме, каждый канал которой содержит фазовый детектор и сумматор, причем источник опорного сигнала подключен к фазовому детектору од.його из каналов непосредственно, а к фазовому детектору другого канала— через фазовращатель 1) .

Однако известный дискриминатор имеет недостаточную линейность и сравнительно невысокую разрешающую способность.

Целью. изобретения является увеличение линейности и разрешающей способНости.

Для этого в цифровой частотный ,дискриминатор, выполненный по двухканальной схеме, каждый канал которой содержит фазовый детектор и сумматор, причем источник опорного сигнала подключен к фазовому детектору одного из каналов непосредственно, а к фазовому детектору другого канала — через фазовращатель, в оба канала введены последовательно включенные аналого-цифровой преобразо2 ватель, вход кот@рого подключен к выходу фазового детектора, блок памяти и первый перемножитель, блок усреднения сигналов, вход которого соеди5 нен с выходом сумматора, и второй перемножитель, а также общий для обоих каналов решающий блок, входы которого соединены с выходами блоков усреднения сигналов, а выход являет-

16 ся выходом цифрового частотного дискриминатора, при этом вьЖод первого перемножителя каждого канала соединен с первыми входами сумматоров-одноименных каналов, вторые входы которых подключены к выходам вторых перемножителей противоположных каналов, выход аналого-цифрового преобразователя первого канала соединен с вто.рыми входами первых перемножителей, 2g а выход аналого-цифрового преобразователя второго канала соедийен с первыми входами вторых перемножителей, вторые входы которых соединены с выходами блоков памяти одноименных ка25 налов, причем решающий блок содержит последовательно соединенные первое и второе функциональные звенья, блок определения модуля числа, первый сумматор и блок присвоения знака, а

ЗО также первый и второй ключи, запоми780153

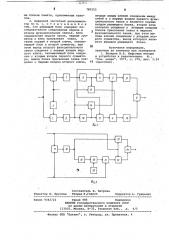

S0 нающий блок и второй сумматор, при этом выход второго функционального звена соединен с первым входом перво-, го ключа, запоминающий блок соединен с вторым входом первого сумматора, выход блока присвоения знака соединен с первым входом второго ключа, вторые входы ключей соединены между собой и с первым входом первого функционального звена и являются первым входом решающего блока, второи вход которого соединен с вторыми входами блоков присвоения знака и первого функционального звена, при этом выходы ключей соединены с входами второго сумматора, выход которого является выходом решающего блока, На фиг. 1 приведена структурная электрическая схема предложенного дискриминатора; на фиг. 2 — структурная электрическая схема решающего блока. 20

Цифровой час!тотный дискриминатор содержит фазовые детекторы 1 и 2, сумматоры 3 и 4, фазовращатель 5, решающий блок 6, аналого-цифровые преобразователи 7 и 8, блоки 9 и 10 памяти, первые перемножители 11 и 12, вторые перемно><ители 13, 14 и блоки

15, 16 усреднения сигналов, при этом решающий блок б содержит первое и второе функциональйые звенья 17 и 18, блок 19 определения модуля числа, первый сумматор 20, блок 21 присвоения знака, первый и второй ключи 22 и 23 соответственно, второй сумматор 24 и запоминающий блок 25.

Цифровой частотный дискриминатор работает следующим образом.

Квадратурные составляющие принимаемого сигнала с выходов фазовых детекторов 1 и 2 поступают в аналогоцифровые преобразователи 7 и 8, где 40 квантуются по времени и амплитуде, в результате чего в каждом элементе разрешения по времени образуется М— разрядное ходовое слово. Поступающие на перемножители 11- 14 текущие и задержанные в блоках 9 и 10 на период повторения сигналы двух соседних зондирований перемножаются, результать перемножения поступают на сумматоры

3 и 4. Выходные сигналы сумматоров

3 и 4, несущие информацию о допплеровской модуляции принимаемого сигнала, поступают в блоки 15 и 16, где осуществляется накопление принятого сигнала с N смежных элементов разре-шения по времени, что позволяет сгладить флюктуации параметров принятого сигнала и снизить влияние собственных шумов приемника. Функциональное звено 17 производит деление сигналов, поступающих с блоков 15 и 16, 60 друг на друга, т.е. определяют их отношение. Функциональное звено 18 позволяет определить усредненный допплеровский набег фазы *ринимаемого сигнала за К-й период повторения и реа- 65 лизует функцию are tg. Блок 19 решающего блока 6 определяет модуль сигнала, поступающего с выхода функционального звена 18. Запоминаюций блок 25 хранит двоичный код величины П. Блок 21 присваивает знак сигнала, поступающего с блока 16, сигналу с выхода первого сумматора 20.

Ключи 22, 23 управляются знаковым

1 разрядом поступающих сигналов, а во втором сумматоре 24 происходит формирование выходного сигнала дискриминатора.

Таким образом, решающий блок б вычисляет усредненный допплеровский набег фазы принимаемого сигнала за

К-й период повторения, а значит и частоту расстройки между входным сигналом и опорным, при этом полярность выходной величины решаюцего блока б указывает на знак расстройки.

Предложенный дискриминатор позволяет увеличить линейный участок дискриминационной характеристики, значительно повысить разрешающую способность по времени и исключает зависимость точности измерения от уровня поступающего сигнала.

Формула изобретения

1. Цифровой частотный дискриминатор, выполненный по двухканальной схеме, каждый канал которой содержит фазовый детектор и сумматор, причем источник опорного сигнала подключен к фазовому детектору одного из каналов непосредственно, а к фазовому детектору другого канала — через фазовращатель, отличающийся тем, что, с целью увеличения линейности и разрешающей способности, в оба канала введены последовательно включенные аналого-цифровой преобразователь, вход которого кодключен к выходу фазового детектора, блок памяти и первый перемножитель, блок усреднения сигналов, вход которого соединен с выходом сумматора, и второй перемножитель, а также обций для обоих каналов решающий блок, входы которого соединены с выходами блоков усредненйя сигналов, а выход является выходом цифрового частотного дискриминатора, при этом выход первого перемножителя каждого канала соединен с первыми входами сумматоров одноименных каналов, вторые входы которых подключены к выходам вторых перемножителей противоположных каналов; выход аналого-цифрового преобразователя первого канала соединен с вторыми входами первых перемножителей, а выход аналого-цифрового преобразователя второго канала соединен с первыми входаМи вторых перемножителей, вторые входы которых соединены с выхода780153

Составитель Е. Петрова

Редактор И. Прусова Техред К,Гаврон Корректор А; Гриценко

Тираж 995 Подпис

ВНИИПИ Государственного комитета CC по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., ное

CP д. 4/5

Заказ 9342/22

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ми блоков памяти, одноименных каналов.

2. Цифровой частотный дискриминатор по п. 1, отличающийся тем, что решающий блок содержит последовательно соединенные первое и второе функциональные звенья, блок определения модуля числа, первый сумматор и блок присвоения знака, а также первый и второй ключи, запоминающий блок и второй сумматор, при этом выход второго функционального звена соединен с первым входом первого ключа, запоминающий блок соединен с вторым входом первого сумматора, выход блока присвоения, знака соединен с первым входом второго ключа, 15 вторые входы ключей соединены между собой и с первым входом первого функ- ционального звена и являются первым входом решающего блока, второй вход которого соединен с вторыми входами блоков присвоения знака и первого функционального звена, при этом выходы ключей соединены с входами второго сумматора, выход которого является выходом решающего блока.

Источники информации, принятые во внимание при экспертизе

1. Лихарев В,А. Цифровые методы и устройства в радиолокации. М., "Сов. радио", 1973, с. 276, рис. 3.24 (прототип) .