Генератор импульсных сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советски»

Социалистических

:Республик н»780165

/

Фг .

Д (61) Дополнительное к авт. сеид-ву

I (22) Заявлено 14.0678 (21) 2627555/18-21 (я)м. кл. с присоединением заявки М (23) Приоритет

Н 03 К 3/28

Государственный комитет

СССР по делам изобретений...н открытий

Опубликовано 15.1180, Бюллетень N9 42 (53) УДК 621 ° 374. .3(088.8) Дата опубликования описания 20.1130 (72) Автор изобретения

В.И. Кафизов (71) Заявитель (54) ГЕНЕРАТОР ИМПУЛЬСНЫХ СИГНАЛОВ

В Л Т Б

Генератор импульсных сигналов к импульсной технике, может быть использован в качестве задающего генератооа в циФровых устройствах.

Известен генератор импульсных 5 сигналов, содержащий два логических элемента НЕ, кварц, резистивный делитель напряжения и формирователь на логическом элементе НЕ (11 .

Известные генераторы импульсных сигналов обладают ограниченными функциональными возможностями генерирова-ния импульсных сигналов по частоте.

В приведенном прототипе для генерирования импульсных сигналов низкрй 15 частоты необходимо увеличить емкость времяэадающего элемента (конденсатора), а для генерирования импульсных сигналов высокой частоты уменьшать емкость конденсатора. Сопротивление 2Q второй половины делителя напряжения и внутреннее сопротивление открытого второго ЛЬгического элемента И-НЕ подключены параллельно. Поэтому, общее сопротивление,„ .на выходе второго 25 логического элемента И-НЕ будет меньше наименьшего. Исходя из того, что постоянная времени в этой цепи

С э„ь . то генерирование импульсных сигналов 30 с низкои частотой или с высокой частотой невозможно. Так как в первом случае увеличение сопротивления второй половины реэистивного делителя напряжения приводит к обратному действию — к уменьшению псстоянной времени 7.,,а во втором случае к шунтированию выхода второго логического элемента И-НЕ.

Непосредственное подключение открытого выхода второго логического элемента И-НЕ к выводу реэистивногс делителя напряжения приводит к искажению формы импульса, которое наблюдается на выходе формирователя в виде излома и возможен срыв генериро" вания импульсных сигналов, .т.е. режим жесткого возбуждения генератора.

Это приводит к уменьшению надежности в работе.

Целью изобретения является расширение функциональных воэможностей.

Для достижения укаэанной цели в генератор импульсных сигналов, содержащий два логических элемента И-НЕ, времяэадающий элемент, подключенный между выходом первого логического элемента И-НЕ и вторым входом второго логического элемента И-НЕ, кото780165 рый также через два последовательно соединенные резистора подключен к общей шине, а выход второго логического:элемента соединен с первым входом первого логического элемента И-HF,, введен диод, анодом соединенный с выходом второго логического элемента

И-НЕ, катодом с общей точкой резисторов делителя и с вторым входом первого элемента И-НЕ.

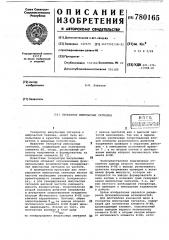

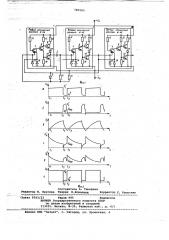

На фиг. 1 изображена принципиальная электрическая схема генератора импульсных сигналов; на фиг.2 гриве дены диаграммы поясняющие работу генератора.

В состав схемы генератора импульсных сигналов входит первый логический элемент И-НЕ 1, второй логический элемент И-НЕ 2, времязадающий элемент — конденсатор 3, резистивный делитель 4 напряжения, диод 5, третий логический элемент И-HE б, многоэмиттерный транзистор 7, одноэмиттерные транзисторы 8-10, резисторы 1114, диоды 15-17.

Предлагаемый генератор импульсных сигналов выполнен на интегральных положительных элементах транзисторно-транзисторной логики (ТТЛ).

Пусть генератор импульсных сигналов отключен сигналом низкого уровня напряжения V на управляющей шине. о

На выходе логического элемента ИНЕ 2 сигнал высокого уровня напряжения V,,так как в нем открыт транзистор 7, а транзистор 8 закрыт,поэтому, открыт транзистор 9, а транзистор 10 закрыт. Через выходное сопротивление Ч",„ закрытого логического элемента Й-НЕ 2 — сопротивление резистора 13, сопротивление открытого транзистора 9 и сопротивление открытого диода 17 — течет ток

Ъ,„ . Этот ток проходит через диод

5 и сопротивление R" второй половины резистивного делителя напряжения 4. С вывода резистивйого делителя напряжения 4 снимается напряжение:

V Э" Р"

+ Выход %М где 0„ „ — пороговый уровень входного напряжения, при котором отпирается логический элемент И-НЕ.

На выходе логического элемента HHE 1 сигнал низкого уровня напряжения 0„, так как в нем уровнями напря а жений 0" и 04 закрыты эмиттерные переходы транзистора 7 и ток через резистор 11, коллекторный переход транзистора 7 течет в базу транзистора 8, поддерживая его открытым, тогда ток через резистор 12, транзистор 8 течет через резистор 14 и базу транзистора

10 и открывает его, при этом, с помощью диода 17 обеспечивается запирание транзистора 9. Ток через конденсатор 3 отсутствует. На выходе логического элемента И-НЕ б сигнал низкого уровня напряжения 0

Поступление на управляющую шину постоянного сигнала с высоким уровнем

4 напряжения U приводит к переключению состояния генератора противоположно исходному. В момент времени t nepe1 пад напряжения к высокому уровню

U„ с выхода логического элемента ИНЕ 1 (фиг. 2а) скачком прокладывается на резистивном делителе напряжения 4 - напряжение 04. > U „ р (фнг. 2r) .

t0

Низкий уровень напряжения U с выхода логического элемента И-НЕ 2

У. (фиг. 26) запирает диод 5. На выходе логического элемента И-НЕ б возникает уровень сигнала Uf, (фиг. 2е) . Со времени t в схеме наступает режим

1М квазиравновесия, при котором. конденсатор 3 заряжается. Ток заряда f,проходит по цепи: конденсатор 3, резистивный делитель напряжения 4, источник питания -Еп + Еп, выходное сопроЯ тивление V,„„ закрытого логического элемента И-HF, 1 — сопротивление резистора 13, сопротивление открытого транзистора 9 и сопротивление открытого диода 17. Постоянная времени цепи заряда: =с(а+ч" )

&ох где С вЂ” емкость конденсатора 3, R — сопротивление резистивного делителя напряжения 4.

Через выходное сопротивление V открытого логического элемента И-НЕ

Вых

2 — сопротивление открытого транзис- тора 10 — проходит входной ток 3 8, логического элемента И-НЕ 1, который течет в нем через входное сопротивление Чэ,„ — резистор 11, базовый и эмиттерный переходы транзистора 7.

С течением времени ток заряда з уменьшается. При этом уменьшается напряжение 04 (фиг. 2r) и увеличивается

40- напряжение Uх на конденсаторе 3 (фиг. 2в). Ко времени t> напряжение

U+v 0„„ и напряжение U c U

4 flOP (фиг. 2г,д). В момент t закрывается

2 логический элемент И-НЕ 2 и, как только нарастание уровня сигнала 0 окажется достаточным для отпирания диода 5, при этом выводе резистивного делителя напряжения 4 возрастает на11 пряжение 04 ) U„ р, открывается логический элемент И-НЕ 1. Перепад напряжения к низкому уровню 0 „ с выхода логического элемента И-HE 1 (фиг.2а) скачком прикладывается на резистивном делителе напряжения 4 - напряжение

0 оР (фиг. 2г). На выходе логичес0" 4 кого элемента И-НЕ б возникает сигнал

0 (фиг. 2е). После переключения генератора импульсных сигналов в новое состояние квазиустойчивого равновесия, со времени t происходит процесс,свя-. ц занный с перезарядом конденсатора 3.

При этом ток разряда конденсатора 3 ,ff

Р Р

=1 +!

:.Ток заряда р проходит по цепи: кон$5 денсатор 3, выходное сопротивление

780165

Н „„„ открытого логического элемента

И-HE 1 — сопротивление открытого транзистора 10 — источник питания—

-Еп и +Еп, выходное сопротивление

V", логического элемента И-НЕ 2, сопротивление Ч;, открытого диода 5, сопротивление R" первой половины резис тивного делителя напряжения 4, подключенного к конденсатору 3. Ток разряда i„" проходит по цепи: конденсатор

3, выходное сопротивление V логи0

Ь61к ческого элемента И-HE 1, источник пи- 10 тания -Еп и +Еп, входное сопротивление.1(„логического элемента И-НЕ. 2 резистор 11, базовой и эмиттерный переходы транзистора 7. Тогда постоянная времени общей цепи разряда.

f = — .

15 ."т

Номинальное значение сопротивле.ния первой половины резистивного де-. лителя напряжения 4

߻ — —.

ЬьП, l

Р С(экЬ Вбп1)

Выбор сопротивления второй половины резистивного делителя напряжения

4 производится в пределах: ч

25 а м Я

Ч

11Щ11 З 1 Tllaxe )0

Bblx B1(Таким образом, в результате блокировки открытого выхода логического элемента И-НЕ 2 конденсатор 3 раэря30 жается через полное сопротивление резистивного делителя напряжения 4

ГАЬ

R = а1+ Q "

35 величину которого можно изменить для получения низкой или высокой частоты генерирования импульсных сигналов.

Это позволяет расширить функциональные возможности генератора импульсных сигналов по частоте.

Формула изобретения

Генератор импульсных сигналов, содержащий два логических элемента И"

НЕ, времязадающий элемент, подключен" ный между выходом первого логическо45 го элемента И-НЕ и вторым входом второго логического элемента И-НЕ, который также через два последовательно соединенные резистора подключен к общей шине, а выход второго логичес50 кого элемента соединен с первым входом первого логического элемента ИНЕ, отличающийся тем, что, с целью расширения функциональных возможностей> в него введен ди- .

55 од, анбдом соединенный - выходом второго логического элемента И-НЕ, катодом с общей точкой резисторов делителя и с вторым входом первого элемента И-HE. бО

Источники информации, принятые во внимание при экспертизе =т;„- —"

3 11 ЧПОР

RV +V V Ч Ч а ьх2 Ь61Х2 Ьх2 э Ьх2

ЭКЬ а + У ФЧ +Ч х

В61ХХ А ВХ2 общее сопротивление цепей подключенных параллельно. С течением времени: ,ток разряда iр уменьшается. При

:этом увеличивается напряжение U ф (фиг. 2r) и уменьшается напряжение 0з (фиг ° 2в) . Ко времени с на; пряжение 0 0„ „(фиг. 2r). Ъ результате, логический элемент И-НЕ 2 закрывается и уровень сигнала U сни2 жается, а также и уровень напряжения 0 4, до уровня U „ap(фиг. 2б,д) .

Логический элемент Й-ЙЕ 1 поддсрживается в открытом состоянии уровнем напряжения 0д. В момент времени

R логический элемент И-HE 2 закрыт

3 (фиг. 2б) и сигнал 02 закрывает диод о

5 и логический элемент И-НЕ 1, на выходе сигнал 0„ (фиг. 2а). На выходе логического элемента И-НЕ 6 возникает сигнал U (фиг. 2е).

Далее, со времени t колебатель3 ный процесс повторяется.

Таким образом, автоматический ввод генератора импульсных сигналов в режим колебаний осуществляется с помощью предварительной подстраховки уровнем напряжения 0", снимаемого с вывода резистивного делителя напряжения 4; с помощью диода 5 регулируется уровень напряжения U для своевременного переключения логического элемента И-НЕ 1 и блокируется открытый выход логического элемента И-НЕ

2 от шунтирования сопротивлением

R .,Bce это повышает надежность в ран боте.

Для предотвращения отрицательных значений импульсных сигналов на входах логических элементах И-НЕ служат диоды 15 и 16.

Длительность времени импульсного сигнала а длительность времени паузы между импульсами

V1

Р11 V

ПОР

Так как уровень сигнала U порядка (2: 3) Unol то, 3 П- Р.

Период повторения импульсных сигналов

1 (7t„+t С(а +ч1 )+С(а +V .

ВЫ 1 ЗКЬ ВЫХ 4.

Частота генерирования импульсных сигналов

1. Информационно-справочный листок

74-0575 (прототип).

780165,.

/ и, 1 Я J 1

Фиг.г

Составитель А ° ТимоФеев . Редактор И. Прусова Техред H,Êoâàëåâà Корректор Г. Решетняк Заказ 9343/23 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж"35, Рауюская наб., д. 4/5

Филиал ППП "Патент", г. ужгород, ул. Проектная, 4