Многоканальный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Соеетскик

Социалистические

Республик

«»780188

К АВТОИ:КОМУ СВИ ВТИЛЬСТ®У (61) Дополнительное к авт, сеид-еу (22) Заявлено 27 ° 06 ° 78 (g1) 2632405/18-21 (5!)М. Кл.з

Н 03 К 13/17 с присоединением эаявки МГосударстаснний IIQMNfct

СССР по дмам нзобрстеннй

N откритнй . (23) Приоритет

Опубликовано 15,1180, бюллетень Й9 42

Дата опубликование олмсаиив 18 ° 11 ° 80 (53) УДК 681 ° 325 (088.8) (72) Авторы изобретение

Э. С. Козлов и В. И. Любченко (71) Завеитель (54) ИНОГОКАНАЛЬНИЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВА1 ЕЛЬ

Изобретение относится к области вычислительной техники и может быть использовано в аналого-цифровых вычислительных комплексах.

Известен многоканальный аналогоцифровой преобразователь, содержащий управляемый генератор импульсов, логический блок управления генератором импульсов, формирующий блок и соединенные последовательно коммутатор, сравнивающий блок, цифро-аналоговый преобразователь, реверсивный счетчик и блок управления, один из входов которого соединен с выходом сравнивающего блока и с входом фор- 1$ мирующего блока, выход которого подключен ко входу логического блока управления генератором импульсов, который имеет двусторонние связи с генератоГом импульсов и блоком уп- 20 равления (1

Недостатком этого многоканального преобразователя являются огр< ни ченные функциональные возможности, заключающиеся в том, что, кроме поад- 2 ресного преобразования сигналов .с выходом каналов, он не позволяет определять аналоговые входные сигналы в заданном диапазоне, экстремальные значения сигналов и не позволя 30 ет производить ускоренный съем информации результата сравнения заданного уровня с входными . сигналами.

Целью изобретения является расши— рение функциональных воэможностей многоканального аналого-цифрового преобразователя.

Поставленная цель достигается т 1, что в многоканальный аналого-цифровой преобразователь, содержащий тактовый генератор импульсов, блок избирания, распределитель, выход которого соединен с первым входом блока управления, выход которого через регистр преобразования соединен со входом цифроаналогового преобразователя, выход которого соединен с первым входом первого блока сравнения, введены блок режимов, элемент 2Й-п ИЛИ, регистр, и-1 блоков сравнения, причем. выход тактового генератора соеди,нен с первым входом блока режимов, второй вход которого соединен . с шиной управляющего входа блока режимов, первый выход соединен с управ ляющим входом регистра, второй выход— с первым блоком избирания, третий выход - co входом распределителя, а четвертый выход - со вторым входом блока управления, третий вход которого со780188 единен с выходом элемента 2И-и ИЛИ,, при этом первый вход первого блока сравнения соединен с первыми входами и-1 блока сравнения, а вторые входы и блоков сравнения соединены с и шинами входных сигналов,при этом выходы и блоков сравнения соединены соответственно со входами регистра, выходы которого соединены соответственно с первыми входами элемента

2И-в ИЛИ, вторые входы которого со единены соответственно с выходами блока избирания, второй вход которого соединен с шиной адреса канала.

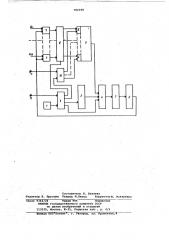

Яа чертеже представлена структурная схема многоканального аналогоцифрового преобразователя.

Преобразователь содержит тактовый генератор 1 импудьсов, блок 2 режимов, распределитель 3, блок 4 упраилення, регистр 5 преобразования, цифроаналоговый преобразователь 6, блоки 7 сравнения, регистр 8, элемент 2И-п ИЛИ 9, блок 10 избирания, шйну ii адреса канала, шину 12 управляющего входа блока+ режимов.

Работа многоканального аналогоцифрОвого преобразователя осуществляется после предварительного занесения в блок режимов кода команды, которая "может соответствовать одному йэ следующих Осиовных режимов работы преобразователя: а) преобразование по заданному адресу1 б) определение максимума;

a) определение минимума;.

r) определение потенциалов заданного диапазона.

В режиме преобразования по заданному адресу на входной регистр блока избирания заносится код адреса избираемого канала, по которому отпира ""ется элемент совпадения 2И - и ИЛИ, соответствующий этому каналу.

В каждом такте по сигналам с блока режимов производится предваритель : ная установка в "0" регистра 8. В ..результате сравнения аналоговых cHI налом U с компенсирующ"м напряжениХ ем U сигналами с блокоа сравнения переключаются в "1" триггеры регист-,: ра 8 тех каналов,для котобых выпол-, няется условие U>y 0<. Элемент 2И-и

ИЛИ пропускает на вход блока 4 управления сигналы с выхода триггера регистра 9 избранного канала. По этим сигналам осуществляется поразрядное уравновешивание измеряемого сигнала -компенсирукюцим напряжением, в результате чего в регистре 5 преобразователя образуется код напряже ния, избранного по заданному адресу . канала.

В режиме определения максимума по сигналу с блока рех<имов блок избира"ния отпирает все и элементы 2И - и

ИЛИ. -По сигналам с блока режимов в к®кдом; такте перед, сравнением произ водится предварительная установка в

"0" регистра 8. При соотношении

0 0„„„„„„,в результате сравнения,все триггерй регистра 8 остаются в нулевом состоянии, на выходе элемента

2И-и ИЛИ остается сигнал "0" и блок управления осуществляет уменьшение напряжения О<. При соотноиении

0 < 0„,„<«,триггерй регистра 8 каналов, для которых выполняется это неравенство, переключаются в "1", на

® выходе элемента 2И-и ИЛИ, появляется сигнал "1" и блок управления по этому сигналу осуществляет увеличение напряжения Ux,.

Таким образом, в процессе преобра33 зования осуществляется уравновешивание компен<сирующим напряжением максимального напряжения, но поскольку веса разрядов уменьшаются по двоичному закону, то компенсирующее нап;щ ряжение будет приближаться к максимальному значению и в регистре преобразователя образуется код максимального напряжения.

В режиме определения минимума по сигналам с блока 2 рех<имов в блоке

4 управления используются инверсные значения сигналов с выхода элемента

2И-п ИЛИ 9, блок избирания отпирает все элементы 2И-и ИЛИ, при этом все триггеры регистра 8 устанавливаются

30 в "1" в каждом такте перед сравнением.

Если в текущем такте поразрядного уравновешивания имеет место неравенство Uxv s ) Uy то все триггеры

35 регистра 8 сигналами "1" с блоков сравнения, поступающими на их счетные входы, переключаются в "0". На выходе элемента 2И-и ИЛИ появляется

"0" и блок управления по инверсным щ значениям этого сигнала производит потактное увеличение компенсирующего напряжения U до тех пор, пока оно не превысит значения О,<„><, При 0 0 „щ„, хотя бы в одном канале, на выходе соответствующего блока сравнения появится сигнал "0", в результате чего на соответствующих триггерах регистра останется

"1" и, следовательно,на выходе 2И-и

ИЛИ будет тоже сигнал "1", по которому блок управления будет осуществлять в данном режиме потактное уменьшение компенсирующего напряжения 0к до тех пор, пока оно не стаI нет меньше напряжения 0< » ° но поскольку веса разрядов уменьшаются по двоичному закону, то компенсирующее напряженне будет приближатЬся к минимальному значению.

Таким образом, в процессе преобразования осуществляется уравновешивание минимального напря><ения, а в регистре 5 преобразователя образуется код минимальногс чапряження.

B режиме определения потенциалов у в заданном диапазоне Uq -0 блокиру780188 ется работа блока управления, блок избирания отпирает все элементы

2И-п ИЛЙ, и все триггеры регистра 8 устанавливаются в "0".

В регистр преобразования заносится код напряжения U<, аналоговый эквивалент этого кода сравнивается блоками сравнения с сигналами каналов.

В результате сравнения в "1" устанавливаются те триггеры регистра

8, для каналов которых выполняется условие 0х ) 0к, Затем в регистр преобразования заносится код напряжения Ug и .напряжение, соответствующее этому коду, сравнивается блоками сравнения с сигналами каналов. В результате сравнения на входы регистра 8 поступают с блоков сравнения сигналы "1" тех каналов,цля которых выполняется условие Uz ) U . Этими сигналами, поступающими на счетные входы триггеров, переключаются в "1" триггеры регистра 8, находившиеся в "0", и переключаются в "0" триггеры регистра 8, ранее установленные в "1". Таким . образом, в "1" остаются триггеры тех каналов, напряжение которых ограничено уровнями U< и U<.

Затем устройство переключается в режим съема информации и поочередным считыванием с триггеров регистра 8 производится съем полученной информации, при котором с регистра 8 блокируется работа блока управления и отпираются элементы 2И-п ИЛИ того канала, адрес которого занесен на входной регистр блока избирания.

Таким образом, при поочередном опросе каналов на выходе элемента

2И-и ИЛИ появляются выходные сигналы триггеров регистра 8 тех каналов,откуда производится их считывание.

Таким образом, использование предлагаемого многоканального аналого-цифрового преобразователя в аналого-цифровых вычислительных комплексах позволит в процессе преобразования информации осуществлять первичную обработку этой информации,В результате этого существенно упрощаются и ускоряются операции определения экстремальных значений функции, нахождения адресов экстремальных значений функции и построения эквипотенциальных линий, что ведет к увеличению производительности укаэанных комплексов.

Формула изобретения

Многоканальный аналого-цифровой преобразователь, содержащий тактовьй генератор импульсов, блок избирания, распределитель, выход которого соединен с первым входом блока управления, выход которого через регистр преобразования соединен со вхо15 дом цифроаналогового преобразователя, выход которого соединен с первым входом первого блока сравнения,о т л и ч а ю шийся тем, что, с целью расширения функциональных воэможностей преобразователя, введены блок режимов, элемент 2И-и ИЛИ,регистр, и-1 блоков сравнения, причем выход тактового генератора соединен с первым входом блока режимов,второй вход которого соединен с шиной управляющего входа блока режимов, первый выход соединен с управляющим входом регистра, второй выход — с первым входом блока избирания, третий выход - co входом распределителя, а четвертый выход — со вторым входом блока управления, третий вход которого соединен с выходом элемента 2H-n HJIH, при этом первый вход первого блока сравнения соединен с первыми входами и-1 блока сравнения, а вторые входы и блоков сравнения соединены с и шинами входных сигналов, при этом выходы и блоков сравнения соединены соответственно со входами рсгистра, 4Q выходы которого соединены соответственно с первыми входами элемента

2И-и ИЛИ, вторые входы которого со единены соответственно с выходами блока избирания, второй вход которо4 го соединен с шиной адреса канала.

Источники информации, принятые so внимание при экспертизе

1. йвторское свидетельство СССР

9 330539, кл. Н 03 К 13/17, 2).07.69.

780188

Составитель Л. Беляева ,-Редактор И. Прусова - Техред М.Петко, Корректор Ю. Макаренко

Закаэ 3 2 Тираж 995 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий. 113035., Москва, Ж»35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная,4