Адаптивный преобразователь частоты в код

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ ""780192

Союз Соаатскнх

Социалистических

Республик

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (6! ) Дополнительное к авт. саид-ву (22) Заявлено 29. 12. 78 - (21) 2703590/18-21 с присоединением заявки H9(23) Приоритет

Опубликоваио1Ы180 Бюллвтемь М 42

Дата опубликований описания 18. 11. 80 рцм, кл.

Н 03 К 13/20

С 01 R 23/10

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621. 317. .76 (088.8) (72) Автор изобретения

В. И. Иаринкин (71) Заявитель

Северо-Западный заочный политехнический институт (54)АДАЛТИВНЫЯ ЛРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД

6 Г Т «=;а ф":: -,.;. „ ;":д «:,,ю". ;:: т р:;*.:г:,"

Изобретение относится к ббласти

1 электроизмерительной техники и может быть использовано при создании прецизионной аппаратуры для измерения изменяющейся во времени частоты элект- S рических колебаний.

Известен интегрирующий частотомер, содержащий счетчик импульсов,генера- тор образцовых тактовых частот, блок управления, динамический оптимизатор !О режима работы, блок датирования изменений и два блока ключей (11

Известен также адаптивный цифровой частотомер с нормированием динамической погрешности, содержащий фор-1с мирующее устройство, вентили счета, основной и динамический счетчики импульсов, генератор калиброванной частоты, счетчик временных баз, матричный дешифратор, подекадные сравни-2р вающие устройства, диодную логическук, ячейку, делители частоты, линию задержки, блок декадных вентилей и переключатели вида запуска и устанонки нормируемого значения абсо- Я5 лютной динамической погрешности(21

Недостатком таких устройств является сложность и низкая точность,поскольку динамическая погрешность за время измерения при быстром измене- ЗО нии частоты может достигать в, них значительной величины.

Наиболее близким к настоящему устройству по технической сущности является цифровой экстраполирующий частотомер, содержащий формирователь импульсов, генератор образцовой частоты, суммирующий, вычитающий и реверсивный счетчики импульсов, блоки перезаписи кода, элемент задержки и двоичный умножитель частоты (3).

Однако в данном устройстве динамическая погрешность за время измерения исключается полностью только при линейном законе изменения изме ряемой частоты,а при более сложном законе изменения входного сигнала оно характеризуется больвюй динамической погрешйостью преобразования.

Другим недостатком данного устройства является то, что оно не осуществляет адаптивно временной дискрети-. зации входного сигнала, что снижает удельную информационную содержательность отсчетов, перегружая каналы связи избыточной информацией йзэа повторяющихся отсчетов. целью изобретения является повышение точности преобразования. и расширение функциональных возможностей.

780192

Указанная цель достигается тем, что а адаптивный преобразователь .частоты в код, содер>хащий формирователь импульсов, генератор образцовой частоты, выход которого подключен к тактовому входу двоичного умножителя частоты, выход которого че-, рез делитель частоты соединен со входом элемента задер>хки, два блока перезаписи кода, три вейтиля, счетчик, выходы разрядов которого соединены О со входами второго блока перезаписи кода, управляющий вход которого подключен к первому выходу элемента задержки, дополнительно введены частотно-импульсный дифференцирующий блок двоичный умножитель частоты, при- IS чем выход формирователя импульсов соединен с тактовым входом дополнительного двоичного умножителя частоты и входом частотно-импульсного дифференцирующего блока, разрядные щ() выходы которого через первый блок перезаписи кода подключены v. управляющим входам обоих двоичных умножителей частоты, выход генератора обра- зцовой частоты соединен с управляющим входом первого блока перезапион кода, зйаковые входы которого подключены к прямому и инверсному выходам знакового разряда частотно-импульсного

Ф дифференцирующего блока и первым входам первого и второго вентилей сост- ЗО ветственно, вторые входы которых соединены со вторым выходом элемента задержки, выходы дополнительного двоичного умножителя частоты и делителя частоты подключены соответственно ко И входу и управляющему входу третьего вентиля, выход которого соединен со счетным входом счетчика, к первому и второму установочным входам которого подключены выходы первого и вто- 40 рого, вентилей, соответственно.

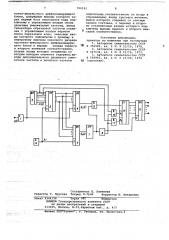

Сущность изобретения поясняется черте>хом, где представлена функциональная схема устройства, на которой

1 — формирователь импульсов, 2 -ча - 4 тотно-импульсный дифференцирующий блок, 3 — первый блок перезаписи кода, 4 — генератор образцовой частоты, 5,6- двоичные умножители частоты, 7делитель частоты, 8 — элемент задер- О х<ки, 9-11 — вентили, 12 — второй блок перезаписи кода, 13 — счетчик.

Формирователь 1 импульсов осуществляет преобразование входного периодического сигнала с изменяющейся частотой f(t) в последовательность стандартных импульсов той же частоты.

Выход формирователя 1 подключен к входу частотно-имйульсного дифференцирующего устройства, который может быть реализован по известной схеме. 40

Блок 2 выдает код, прямопропорциональный скорости изменения f(t) час-. тоты входного сигнала: N(t)2 f(t)/ д „><, где-п - число разрядов выходного ко- да блока 2, 1 „ - максимально-допус- 65 тимая скорость изменения частоты.Разрядные выходы блока 2 через первый блок 3 перезаписи кода, управляющий вход которого соединен с выходом генератора 4 образцовой частоты и тактовым входом двоичного умножителя 5 частоты, подключен к управляющим входам двоичного умножителя 5 частоты и дополнительного умножителя 6 частоты, тактовый вход которого соединен с выходом формирователя 1.Двоичный умножитель б частоты выдает на выходе частоту () = f (t ) /IN (t ) 1 /2" = f (t) l < (< ) I /" „е а двоичный умно>хитель 5 частоты -частоту f (t)= Н(ф" =fyl ()1/ „„, где f частота на выходе генератора 4. Выход двоичного умножителя 5 частоты через делитель 7 частоты подключен к входу элемента 8 задержки и управляющему входу вентиля 9 блокировки если коэффициент деления целите> ля 7 подключен к входу элемента 8 за- . держки и управляющему входу вентиля

9 блокировки. Если коэффициент деления .делителя 7 равен М, то на его в1.".ходе появляется ка><дый М-тый импульс и .пала f (t),который с некоторой задер>хкой появляется затем на первом выходе элемента 8 задер>хки, соединенном с управляющим входом второго блока 12 перезаписи кода, а затем на втором выходе элемента 8 задержки, Разрядные входы блока 12 перезаписи кода подключены к выходам счетчика

13 импульсов, таким образом блок 12 по сигналу от элемента 8 задержки осуществляет передачу кода Мр, содержащегося в счетчике 13, на выходные шины. Второй выход элемента 8 задер><ки через вентили 10 и 11 начальной установки подключен к входам начальной установки счетчика 13, при этом управляющие входы вентилей

10 и 11 связаны с прямым и инверсным выходами знакового разряда блока 2.

Таким образом, при возрастании частоты входного сигнала (f(t)>0) по импульсу начальной установки от элемента 8 задержки в счетчике 13 будет .устанавливаться код N, а при убывании частоты входного сигнала (f(t)

f„ (t-) за время, определяемое часто той f (t).

Работа устройства .происходит следующим образом.

При поступлении на вход формирователя 1 изменя><>щейся во времени частоты f(t) блок 2 выдает код N(t), соответствующий скорости изменения входного сигнала, который через блок перезаписи кода 3 с частотой f .,èìå. ющей тот же порядок, что и входная

780192 частота, переписывается во входйые регистры двоичных умножителей 5 и б частоты. При этом, если f(t) ) О, то ,переписывается прямой код, если

f (t)<О - инверсный код. На выходах двоичных умножителей 5 и б частоты формируются последовательности импульсов с частотами 1., (с ) и f2 (), которые поступают на счетный вход счетчика 13 и на делитель 7 частоты. В момент окончания цикла измерения частоты появляется потенциал на выходе делителя 7, который запирает вентиль 9 и прекращает поступление импульсов на счетный вход счетчика

13 на время, достаточное для считывания кода на выходные шины преобразователя и для начальной установки счетчика 13, С некоторой задержкой во времени, достаточной для окончания переходных процессов в счетчике 13, поступает импульс на управля щий вход блока 12 перезаписи кода,и код, записанный в счетчике,выдается на выходные шины. Затем по импульсу, поступающему с некоторой задержкой на входы вентилей начальной установки в счетчике 13 уст чавливается начальный код N„ N в зависимости от информации, содержащейся н знаковом разряде дифференцирующего блока

2. К этому моменту потенциал на выходе делителя 7 исчезает, вентиль

9 открывается и начинается новый цикл изменения частоты.

Длительность 1 цикла измерения определяется выражением

Г (t)dt=d или (()(й)(Ь =(((„ /(id аким образом длительность цикла измерения уменьшается при увеличении скорости изменения сигнала и наоборот увеличивается при уменьшении скорости изменения входного сигнала,так что данный преобразователь осуществляет адаптивную временную дискретизацию входного сигнала.

Изменение входного сигнала но времени с момента начала цикла измерения определяется выражением

f t)=fo+jf(L) где f> - значение частоты в момент начала цикла.

Число импульсов, поступивших в счетчик 13 эа время цикла, равно

d (1) (Г (t)dt=) (((If(t)ldt+ ,+ lf (t)(() tat)

П скольк ((((tt)(() (Т) 4Ъдй 1 I((((tt)l d f ° ()) где знак "+" соответствуете(с) > О, знак "-" соответствует f()< О,то с учетом (1), (2) и (3) число импуль сов, поступивших в счетчик, равно и (т)=Nf /f„s-, м f /к Nf(y)fÄ+

Таким образом число импульсон,поступивших в счетчик 13 эа время цикла, отличается от точного результата преобразования частоты иа одну и ту же величину A N)H f „/f „ независимо от закона изменеййя частоты в течение цикла, причем отличается »а

-ь((при t(t)> О и на+ай при

f(t) < О. Но так как при начальной установке в начале цикла в счетчике устанавливается код и A М при

f(t) > 0 или N - а N при f(t) < О,то динамическая погрешность в окончательном результате преобразования равна нулю прН любом законе монотонного изменения частоты в течение ци15 кла.Код, выдаваемый на выходные шины преобразователя в момент Т окончания цикла, равен и = ИГ(1) /1

Таким образом, настоящий адаптивный преобразователь частоты н код характеризуется отсутствием динамической погрешности эа время измерения при любом законе монотонного из25 менения частоты и обеспечивает адаптинную дискретизацию входного сигнала но времени, т.е. позволяет повысить точность и удельную информационную содержательность преобразования частоты электрических. сигналов в код.

Использование изобретения в àïïàратуре аналого-цифрового преобразования, широко применяющейся н научных исследованиях и н промышленности, н частности в автоматизированных системах управления технологическими процессами, может способствовать повышению производительности труда в соответствующих отраслях науки и производства.

Формула изобретения

Адаптивный преобразователь часто45 ты в код, содержащий формирователь импульсов, генератор образцовой частоты, выход которого подключен к тактовому входу двоичного умножителя частоты, выход которого через

Щ делитель частоты соединен со входом элемента задержки, два блока перезаписи кода, три вентиля, счетчик,выходы разрядов которого соединены со входами нторого блока перезаписи ко.

55 да упраВляющий Вход которого подключен к первому выходу элемента задержки, отличающийся тем, что, с целью повышения точности преобразования и расширения функ. циональных воэможностей, в него до40 полнительно введены частотно-импульсный дифференцирующий блок и двоичный умножитель частоты, причем выход формирователя импульсов соединен с тактовым нходом дополнительного двоично65 го умножителя частоты и входом час780192

Составитель Л. Плетнева

Редактор Г. Прусова Техред Н. Граб Корректор Ю. Макаренко

Заказ 9344 24 Тираж 9 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,Раушская наб., д. 4/5

Филиал ППП"Патент", г. Ужгород, ул. Проектная, тотно-импульсного дифференцирующего блока, разрядные вйходы которого через первый блок перезаписи кода подключены к управляющим входам обоих . двоичных умножителей частоты, выход генератора образцовой частоты соединен с управляющим входом первого блока перезаписи кода, знаковые входы которого подключены к прямому и инверсному выходам знакового разряда частотно-импульсного дифференцирующего блока и первым входам первого и второго вентилей соответственно, вторые входы которых соединены со вторым выходом элемента задержки,вы ходы дополнительного двоичного умножителя частоты и делителя частоты 15 подключены соответственно ко входу и управляющему входу третьего вентиля, выход которого соединен со счетным входом счетчика, к первому и второму установочным входам которого подключены выходы первого и второго вентилей соответственно.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 356582, кл. G 01 R 23/10, 1970.

2. Авторское свидетельство СССР

Р 447636, кл. G 01 R 23/10, 1972.

3. Авторское свидетельство СССР

М 568903, кл. С 01 R 23/00, 1974 (прототип).