Реверсивный двоично-десятичный счетчик

Иллюстрации

Показать всеРеферат

Сеип Севетскив

Сециалистическик

Республик

О ЙСАНИЕ

ИЗОБРЕТЕНИЯ

<>780205

К АВТОРСКОМУ СВИ ВТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (51)М. Кл

Н 03 К 23/24 (22) Заявлено 121278 (21) 2695237/18-21 с присоедммемием эаявкм l4O

Государстаснный комнтст

СССР но делам нзобрстеннЯ н открытнЯ (23) Приоритет

Опубликовано 151180. 6юллетемь Йо 42

Дата опубликоваммя описания 25. 11. 80 (53) УДК 621.

374 32(088 8) (72) Авторы изобретения

Н. И. Макаренко и В. Н. Буце нко (71) Заявитель (54) РЕВЕРСИВНЫй ДВОИЧНО-ДЕСЯТИЧНЫИ СЧЕТЧИК

Изобретение относится к электронной и вычислительной технике, в частности -к реверсивным двоично-десятич- ным счетчикам и может быть использовано в цифровых системах автоматичес- З кого контроля и управления.

Известен разностный двоичный счетчик, каждый разряд которого содержит триггер, элемент ИЛИ и два элемента

И, первые входы которых соединены 10 соответственно с прямым и инверсным выходами триггера, счетный вход которого соединен .с выходом элемента

ИЛИ, входы которого соединены с вторыми входами элементов И того же раз- )$ ряда и входами сложения и вычитания данного разряда, а выходы первого и второго элементов И соединены соот- ветственно с выходами перекоса и заема данного разряда t1) . 20

Недостатком этого счетчика является невозможность счета в двоичнодесятичном коде.

Известен также реверсивный двоично-десятичный счетчик, содержащий 25 четыре разряда, каждый из которых содержит триггер, элемент ИЛИ и первый и второй элементы И, счетный вход триггера каждого разряда соединен с выходом элемента ИЛИ того же 30 разряда, а входь элемента ИЛИ каждого разряда, крсме первого, соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первые входы которых соединены соответственно с Прямым и инверсным выходами триггера того же разряда, вторые входи первого и второго элементов И ка>хдо1о разряда, кроме. первого и четвертого разрядов, соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первый и второй входы элемента ИЛИ первого разряда соединены соответственно с входами сложения и вычитания реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответственно первого и второго элементов И этого разряда (2) .

Недостатком этого реверсивного двоично-десятичного счетчика является относительно низкая достоверность функционирования, что связано с кратковременным появлением в процессе счета кодовых состояний, не входящих в двоично-десятичный код.

0елью изобретения лвляется повышение достоверности функционирования.

Поставленная цель достигается тем, 7 )205 что в реверсивный двоично-десятичны) счетчик, содержащий четыре разряда, каждый из которых содержит триггер элемент ИЛИ и первый и второй элеФ менты И, счетный вход триггера каждого разряда соединен с выходом элемента ИЛИ того же разряда, а входы элемента ИЛИ каждого разряда, кроме первого, соединены с выходами соответственно первого и второго элементов

И предыдущего разряда, первые входы которых соединены соответственно с 30 прямьы и инверсным выходами триггера того же разряда, вторые входы первого и второго элементов И каждого разряда, кроме первого и четвертого раз— рядов, соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первый и второй входы элемента ИЛИ первого разряда соединены соответственно с входами слсгжения и вычитания реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответственно первого и второго элементов И этого разряда, введен элемент И-НЕ, выход которого соединен с Х входами триггеров второго и третьего разрядов, входы элемента И-НЕ соединены с инверсными выходами триггеров всех разрядов, вход сложения реверсивного двоично-десятичного счетчика соединен с вторым входом первого элемента И чет- 30 вертого разряда, третий вход которого соединен с первым входом первого элемента И первого разряда, третий вход которого соединен с инверсным выхо-. дом триггера четвертого разряда, 33 третий вход элемента ИЛИ соединен с выходом первого элемента И этого разряда и выходом переноса реверсивного двоично-десятичного счетчика, выход заема которого соединен с выходом второго элемента И четвертого разряда, второй вход которого соединен с выходом второго элемента

И третьего разряда.

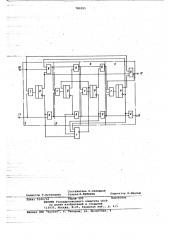

Структурная схема реверсивного двоично-десятичного счетчика показа- 4> на на чертеже.

Реверсивный двоично-десятичный счетчик содержит элемент 1 И-НЕ и четыре разряда 2-5, каждый из которых о содержит триггер 6, элемент ИЛИ 7 и первый 8 и второй 9 элементы И, счетный вход триггера б каждого разряда соединен с выходом элемента ИЛИ

7 того же разряда, а входы элемента

ИЛИ каждого разряда, кроме первого, соединены с выходами соответственно первого 8 и второго 9 элементов И предыдущего разряда, первые входы которых соединены соответственно с прямым и инверсным выходами триггера 60

6 того же разряда, вторые входы первого 8 и второго 9 элементов И каждого разряда, кроме первого 2 и четвертого 5 разрядов, соединены с выходами соответственно первого 8 и второго 9 65 элементов И предыдущего разряда, пер вый и второй входы элемента ИЛИ 7 первого разряда 2 соединены соответственно с входами сложения 10 и вычитания

11 реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответственно первого 8 и второго 9 элементов. И этого разряда, выход элемента И-HE 1 соединен с Х входами триггеров 6 второго 3 и третьего 4 разрядов, входы элемента И-HE 1 соединены с инверсными выходами триггеров б всех разрядов 2, 3, 4 и 5., вход сложения 10 реверсивного двоично-десятичного счетчика соединен с вторым входом первого элемента И 8 четвертого разряда 5, третий вход которого соединен с первым входом первого элемента И 8 первого разряда 2, третий вход которого соединен с инверсным выходом триггера б четвертого разряда 5, третий вход элемента ИЛИ 7 соединен с выходом первого элемента И 8 этого разряда и выходом переноса 12 реверсивного двоично-десятичного счетчика, выход заема 13 которого соединен с выходом второго элемента И 9 четвертого разряда 5, второй вход которого соединен с выходом второго элемента И 9 третьего разряда 4.

Работает устройство следующим образом.

Предположим, в исходном состоянии триггеры 6 находятся в нулевом логическом состоянии, при этом элементы

И 9 открыты, а элементы И 8 закрыты.

На выходе элемента И-НЕ 1 присутствует нулевой логический потенциал, запрещающий переход триггеров б второго и третьего разрядов в единичное логическое состояние.

В режиме сложения первый импульс, поступающий на вход сложения 10, проходит через элемент ИЛИ 7, устанавливает триггер 6 первого разряда в. единичное логическое состояние, которое выдает разрешающий сигнал на элемент И 8 для прохождения последующего импульса. При этом на выходе элемента И-НЕ i появляется логический единичный потенциал, разрешающий переход триггеров 6 второго и третьего разрядов из логического состояния "0" в логическое состояние "1". Второй импульс устанавливает через элемент ИЛИ

7 триггер 6 первого разярда 3 в нулевое логическое состояние, а через открытый элемент И 8 и элемент ИЛИ

7 — триггер б второго разряда в единичное логическое состояние. При дальнейшем поступлении на вход счетчика от третьего до восьмого импульсов, счетчик проходит все состояния, которые соответствуют двоично-десятичному коду 8-4-2-1. После записи Ъ счетчике кода "1000", закрывается элемент И 8 первого разряда сигналом

780205 с инверсного .выхода триггера 6 четнертого разряда.

Девятый импульс устанавливает через элемент ИЛИ 7 триггер 6 первого разряда в единичное логическое состояние, т. е. записывается код

1001, соответствующий цифре 9. После записи в счетчике цифры 9 открывается элемент И 8 четвертого разряда.

Поступающий десятый импульс через элемент ИЛИ 7 первого разряда, И четвертого разряда, ИЛИ 7 четвертого разряда устанавливает триггеры 6 первого и четвертого разрядов в нулевое логическое состояние, а на выходе элемента И 8 четвертого разряда образуется сигнал "перенос". В счетчике записывается код ",0000", что и необходимо для реализации пересчета на десять.

В режиме вычитания, когда все четыре триггера 6 находятся в нулевом состоянии, элементы И 9 открыты, на выходе элемента И 8 четвертого разряда присутствует нулевой логический потенциал, который поступает на вход элемента ИЛИ 7 четвертого разряда и не влияет на работу счетчика при реверсе. На нходах. т триггеров б второго и третьего разрядов держится нулевой логический потенциал, за— прещающий переход их с нулевого логического состояния н единичное

Первый входной импульс, поступающий

«а вход вычитания 11 через элемент

ИЛИ 6 первого разряда, И 9 и ИЛИ 7 четвертого разряда установит триггеры 6 первого и четвертого разрядов в единичное логическое состояние, т. е. запишется код "1001", что соответствует цифре 9. При этом на выходе элемента И 9 четвертого разряда вырабатывается сигнал "заем".

На 1 входах триггеров б второго и третьего разрядов образуется единичный логический сигнал, не влияющий на работу счетчика н режиме вычитания. Очередными импульсами счетчик последовательно установится в состояния, соответствующие 8, 7,...,1,0 как и н обычном вычитающем счетчике.

Таким образом, предлагаемое устройство позволяет повысить надежность работы счетчика в коде 8-4-2-1, поскольку исключаются промежуточные кратковременные состояния "1010" и

"1111", не соответствующие коду 8 4-2-1.

Формула изобретения

Ренерсивный двоично-десятичный счетчик, содержащий четыре разряда, каждый из которых содержит триггер, элемент ИЛИ и первый и второй эле5 менты И, счетный вход триггера каждого разряда соединен с выходом элемента ИЛИ того же разряда, а входы элемента ИЛИ каждого разряда, кроме первого, соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первые входы которых соединены соответственно с прямым и инверсным выходами триггера того же разряда, вторые входы первого и второго элементов И

1 каждого разряда, кроме первого и четвертого разрядов, соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первый и второй входы элемента ИЛИ

20 первого разряда соединены соответственно с входами сложения и вычитания реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответственно первого и

25 второго. элементов И этого разряда, отличающийся тем. что, с целью повышения достоверности фу«кциониронания, в него введен элемент

И-НЕ, ныход которого соединен с т входами триггеров второго и третьего разрядов, входы элемента И-НЕ соединены с инверсными выходами триггеров всех разрядов; вход сложения реверсивного двоично-десятичного счетчика

35 соединен с вторы входом первого элемента И четвертого разряда, третий вход которого соединен с первым входом первого элемента И первого разряда, третий вход которого соединен с инверсным выходом триггера

40 четвертого разряда, третий вход элемента ИЛИ соединен с выходом перво- . го элемента И этого разряда и выходом . переноса реверсивного дноично-десятичного счетчика, выход заема кото45 Рого соединен с выходом второго элемента И четвертого разряда, второй вход которого соединен с выходом второго элемента И третьего разряда.

Источники информации, 0 принятые во внимание при экспертизе

1. Контрольно-измерительная техника. Выпуск 22. Львов, 1977, с.б2, ри е 2 °

2. Авторское свидетельство СССР

9 525251, кл. Н ОЭ К 23/24, 1977 (про 5 тотип).

780205

Корректор М.Шароши

Составитель О.Скворцов

Редактор Т.Кузнецова Техред A.Áàáèíåö

Заказ 93 4 24 Тираж 99 Подписное

ВНИИПИ Гооударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-25, Раушская наб., д. 4/5

Филиал ППП Патент, r. жгород, ул. Проектная,