Цифровой адаптивный корректор межсимвольных искажений в сигналах передачи данных

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

) . ия . тюнр," .в

Союз Советских

Социалист инеских

Республик („)780209 (61) Дополнительное к авт. свнд-ву (22) Заявлено 04.0478 (21) 2599963/18-09 с присоединением заявки ¹ (23) Приоритет

Опубликовано 15.1180, Бюллетень йо 42

Дата опубликования описания 15.11.80 (53)N. Кл. н 04 В 3/04

Государственный комитет

СССР ио делам изобретений и открытий (53) УДК,621. 395. .662(088.8) (72) Авторы изобретения

С.В,Стукалов, Л.Г.Израильсон и A.Ã.Òêà÷åíêî (71) Заявитель (54) ЦИФРОВОЙ АДАПТИВНЫЙ КОРРЕКТОР МЕЖСИМВОЛЬНЫХ:

ИСКАЖЕНИЙ B СИГНАЛАХ ПEPЕДАЧИ ДАННЫХ

Изобретение относится к технике связи и может использоваться в устройствах для адаптивной коррекции межсимвольной интерференции в принимаемых сигналах, переданных методом

5 трехкратной относительной фазовой модуляции (ТОФМ) .

Известен адаптивный корректор межсимвольных искажений в сигналах передачи данных, содержащий блок памяти знака отклонения фаз от номинала и блок памяти фазовых углов, выходы которых подключены ко входам первого сумматора.по модулю два, первый вход второго сумматора по модулю два сое- 15 динен с вторым выходом блока памяти знака отклонения фаэ от номинала, первый вход которого и первый вход блока памяти фазовых углов объединены и соединены с первым выходом блока уп- 20 равления, второй выход которого подключен к управляющему входу гармонического корректора, на второй вход которого подан входной сигнал, третий и четвертый входы которого соеди- 25 нены соответственно с выходами первого,и .второго сумматоров по модулю два, а выход гармонического корректора является выходом адаптивного кор ректора 1). 30

Однако известный адаптивный коррект ор межс им воль ных ис к аже ни и в с и г н алак передачи данных обладает низкой точностью и большим временем коррекции.

Целью изобретения является повышение точности и сокращение времени коррекции.

Для этого в цифровой адаптивный корректор межсимвольных искажений в сигналах передачи данных, содержащий блок памяти знак отклонения амплитудь1 сигнала от номинала и блок памяти полярностей сигнала, выходы которых подключены ко входам первого сумматора по модулю два, первый вход второго сумматора по модулю два соединен с выходом блока памяти знака отклонения амплитуды сигнала от номинала, первый вход которого и первый вход блока памяти полярностей сигнала объединены и соединены с первым выходом блока управления, второй выход которого подключен к управляющему axo— ду цифрового гармонического корректора,на второй вход которого подан входной сигнал, а выход является выходом цифрового адаптивного корректора, и третий и четвертый сумматоры по модулю два, причем первый вход четвертого

780209 сумматора по модулю два соединен с выходом блока памяти полярностей сиг., нала, введены дополнительные первый и второй сумматоры по модулю два, блок памяти знака отклонения амплитуды сигйала от номинала и блок; памяти полярностей сигнала, три коммутатора,,накопитель и блок памяти амплитуды сигнала, при этом первый ныход первого дополнйтельного сумматора по модулю два подключен ко второму входу блока памяти знака отклонения амплиту- iO

,цы сйгнала от номинала, оцйн из sxo" "дов первого дополнительного суммато ра по модулю два соединен со вторым входом блока памяти полярностей сигнаЛа, один из входов второго дополнительного сумматора по модулю два соединен со вторым входом дополнитель.. ного блока памяти полярностей Сигнала, выход которого подключен ко входам третьего и второго сумматоров по ®6 модулю .два, нходы третьего и четвертого сумматоров по модулю дна соедийены с выходом дополнительного бло:ка памяти знака отклонения амплитуды сигнала от номинала, второй вход которогб соединен с выходом второго дополиительйого сумматора по модулю два, выход четвертого и нторого сумматоров IIO модулю два и выход блока памяти амплитуды сигнала подключены "ко входам первого коммутатора, выход 3Q которого подключен к одному из входон второго коммутатора, другой вход которого соединен с третьим выходом блока управления, третий вход

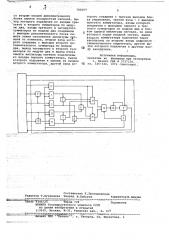

С йыходом третьего коммутатора, 3S входы которого соединены с выходами первого и третьего сумматоров по моЩ лИ -два и блоком памяти амплитуды сигнала; на вход которого подан входной сигнал, выход второго коммутатора подключен через накопитель к второму входу цйфрового гармонического корректора, другой выход которого подключен к другому входу накопителя. на чертеже приведена структураня 45 электрическая схема предложенного устройства. Цифровой адаптивный корректор меж- символьных искажений в сигналах передачи .данных содержит блок йамятй 5() знака отклонения амплитуды сигнала от номийала 1 .áëáê йамяти пблярнбстей сйгнала 2, первый и второй сумматоры пб модулю два 3 и 4, блок управления

5, цифровой гармонический корректор

6, третий и четвертый сумматоры по модулю дна 7 и 8, дойолнительные пернйй и второй сумматоры по модулю два

9 и 10, дополнительные блок, памяти знака отклонения амплитуды сигнала от: номинала 11 и блок памяти полярностей Я) сигнала 12, три коммутатора 13,14 и

15, накопитель 16 и блок памяти амплитуды сигнала 17. устройство работает следующим образом. 65

Алгоритм работы устройства для случая компенсации собственного мешаю цего влияния:

sgn Й „. =в на„Ову а„О+ sgn е„(1)

5+n Ъ „"-зу а @Вязла. ®sgn8 (2)

% для случая компенсации перекрестного мешающего влияния:

«р Ъ„"=з ьа - Озера О+ ре (3)

sqn и" ;. =syn a ® у а @эр е, (4) де sgn ao и

<9 >1 и e q n а — з нак проекции с иг

Т налон, создающих мешающие влияния, на когерентные колебания I и и соответственно; )и е и зс и.е - - знак проекции отклонения ампли туд сигналов, подверженных мешающему влиянию на когерентные колебания Х и соответственно.

Для реализации алгоритма адаптивной коррекции достаточно испольэовать только дна уравнения: либо (1 ) и (3), либо (2) и (4) .

Однако мешающие влияния пропорциональны амплитуде вызынаншего их сигнала. Поэтому при приеме сигналов с

TOCM возможны два случая: амплитуда сйгйала данных, демодулиронанного с помощью синфаэйого (I) когерентного колебания больше, чем с помощью кнад-. ратурного (6) когерентного колебания и амплитуда сигнала, демодулированного с помощью когерентного колебания ц, больше, чем с помощью когерентного колебания I

Тогда в первом случае для анализа необходимо использовать сигналы, входящие в выражения (1) и (3), а во втором - в выражения (2) и (4),так как прй этом знаки сигналов 5 И Ъ,(будут опреде,лены с большей достоверностью, чем при использований сигналов по выражениям (2) и (4) . Соответственно необходимо формировать двоичный сигнал, свидетельствующий об этом неравенстве амплитуд, который должен поступать н соответствующий блок памяти цифрового адаптивного корректора.

Для реализации алгоритмов на нходы дополнительного первого сумматора по модулю два 9 поступают сигналы

780209

gqyla . u u e.-, а на входы. дополнительс f ного второго сумматора по модулю дца

10 поступают сигналы и d и Чр,8 Сигналы с выходов дополнительных первого и второго сумматоров по модулю два 9 и 10 записываются сбответственно в основной и дополнительный блоки памяти знака отклонения амплитуды сигнала от номинала 1 и 11. Кроме того сигналы SQNa

На выходе первого сумматора по t5 модулю два 3 получаем сигнал spy 4; в соответствии с выражением (1), на выходе второго сумматора по модулю два сигнал SQN b ", в соответствии с выражением (4), на выходе третьего щ0 сумматора по модулю два 7 — сигнал

5qn% в соответствии с выражением (3), и, наконец, на выходе четвертого сумматора по модулю два 8 — сигнал 8 и в соответствии с выражением (2).

Сигналы с выходов первого и четвертого сумматоров по модулю два 3 и 8, отображающие направление регулировки в соответствии с выражениями (1) и (2) с целью компенсации синфазного мешающего воздействия, поступают на входы первого коммутатора 13. На вход втброго коммутатора

14 подаются сигналы с выходов второго и третьего сумматорбв по модулю два 4 и 7, отображающие направление регулировки в соответствии с выражениями (3) и (4), с целью компенсации перекрестного мешающего воздействия.

Поскольку целесообразно для фор- 40 мирования сигналов для изменения коэффициента передачи регуляторов отводов испольэовать демодулированные сигналы с большой амплитудой, то необходимые переключения осуществляются первы-45 ми и вторыми коммутаторами 13 и 14 по сигналам, поступающим с выхода блока памяти амплитуды сигнала 17, При этом значительно достовернее формируются сигналы направления изменения коэффициента передачи регуляторов отводов, уменьшается число сложных регули. ровок, что, в свою очередь, позволяет использовать накопитель 16 меньшей емкости. На входы третьего коммутатора 15 поступают сигналы с выходов первого и второго коммутаторов 13 и

14. Управление работой третьего коммутатора 15 осуществляется блоком .управления 5, который подключает на вход накопителя 16 сначала сигнал для $0 поочередной регулировки коэффициентов передачи регуляторов всех отводов по прямым связям, а затем — сигнал регулировки всех отводов по перекрест. ным связям. 65

После интегрирования сигналов о знаке изменения коэффициента передачи регулятора анализируемого отвода в накопителе 16 цифровое число, соответствующее коэффициенту передачи, записывается в цифровом гармоническом корректоре б. На второй вход цифрового гармонического корректоРа б поступают аналоговые сигналы а и а - .

В соответствии с алгоритмом работы

1 блока управления 6 в цифровом гармони ческом корректоре б осуществляется пос"

4едовательно для каждого иэ отводов перемножение цифровых слов кода выбор-. ки и коэффициент передачи. Полученные произведения, т.е. цифровые сигналы отводов последовательно суммируются в результате чего на выходе цифрового гармонического корректора 6 формируются два откорректированных цифровых слова.

Таким образом, использование предложенного устройства повышает точность коррекции и уменьшает время нартройки, что выгодно отли гает его от прототипа.

Формула изобретения

Цифровой адаптивный корректор межсимвольных искажений в сигналах передачи, данных, содержащий блок памяти знака отклонения,амплитуды сигнала от номинала и блок памяти полярностей сигнала, выходы которых подключены ко входам первого сумматора по модулю два, первый вход второго сумматора по модулю два соединен с выходом блока памяти знака отклонения амплитуды сигнала от номинала, первый вход которого и первый вход блока памяти полярностей сигнала объединены и соединены с первым выходом блока управления, второй выход которого подключен к управляющему. входу цифровОго гармонического корректора, на второй вход которого подан входной сигнал, а выход является выходом цифрового адаптивного корректора, и третий и четвертый сумматоры по модулю два, причем первый вход четвертого сумматора по модулю два соединен с выходом блока памяти полярностей сигнала, о т л и ч а ю— шийся тем, что, с целью повышения точности и сокращения времени коррекции, введены дополнительные первый и второй сумматоры по модулю два, блок памяти знака отклонения амплитуды сигнала от номинала и блок памяти полярностей сигнала, три коммутатора, накопитель и блок памяти амплитуды сигнала, при этом первый выход первого дополнительного сумматора по модулю два подключен ко второму входу блока памяти знака отклонения амплитуды, сигнала от номинала, один их входов первого дополнительного сумматора по модулю два соединен со вторым входом блока памяти полярностей сигнала, один из входов второго дополнительного сумматора по модулю два соединен

Ф..

780209

Составитель E. Прозоровская . Редактор Т.Кузнецова Техред Н-.Бабурка Корректор М. Демчик заказ 9346/25 Тираж 729 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

О

;.. е, М. ". — l

Филйал ППП Патент, г. Ужгород, ул, Проектная, 4 со вторым входом дополнительного блока памяти полярноСтей сигнала, вы,, ход которого подключен ко входам тре тьего и второго сумматоров по модулю два, входы третьего и четвертoro сумматоров по модулю два соединены с выходом дополнительного блока памяти знака отклонения амплитуды сигнала от.номинала, второй вход которого соединен с выходом второго дополнительного сумматора по модулю два, выход четвертого и второго сумматоров по модулю два и выход блока памяти амплитуды сигнала подключены ко входам первого коммутатора, выход которого подключен к одному из входов второго коммутатора, другой вход коФ торого,соединен с третьим выходом блока управления, третий вход - с выходом третьего коммутатора, входы которого соединены с выходами первого и третьего сумматоров по модулю два и блоком памятй амплитуды сигнала, на вход которого подан входной сигнал, выход второго коммутатора подключен через накопитель ко второму входу цифрового гармонического корректора, другой выход которого подключен к другому входу накопителя.

Источники информации, принятые во внимание при экспертизе

1. Патент США Р 3727136, 1 кл, 325-320, 1974 (прототип) .