Устройство для управления вводом-выводом информации

Иллюстрации

Показать всеРеферат

О П И С А Н И Е « 780694

ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕ ТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 22.05.79 (21) 2771342!18-24 (51) М.Кл.з G 06 F 3/04 с присоединением заявки— (23) Приоритет— (43) Опубликовано 23.01.82. Бюллетень № 3 (45) Дата опубликования описания 23.01.82

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681.327.11 (088,8)

I (72) Авторы изобретения

А. И. Сороколетов, В. В. Герасимов и А. Г. Пьянков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ

ВВОДОМ-ВЫВОДОМ И НФОРМАЦИ И

Изобретение относится к вычислителькой технике и может быть использовано при обмене информационными массивами данных в цифровых устройствах.

Известно устройство, содержащее элементы И, коммутаторы, в котором при ошибках управления или интерфейса каналов осуществляется запись в оперативную память зкачений контролируемых элементов (1).

Недостатками устройства являются сложное оборудование и большое число связей от контролируемых элементов, что приводит к понижению надежности.

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее первую и вторую группу элементов И, коммутаторы какала и информации, регистр адреса канала, дешифратор и регистр информации оперативной памяти, причем выходы контролируемых элементов соединены с входами первой группы элементов

И, выход которой соединен с входом коммутатора канала, выход коммутатора канала соединен со входами второй группы элементов И, другие входы которой соединены с выходом дешифратора, вход де шифратора соединен с выходом регистра адреса канала, выход второй группы элес ментов И соединен с выходом коммутатора информации, выход которого соединен с входом регистра информации оперативной памяти (21.

Недостатками устройства также являются сложность оборудования и большое число связей от контролируемых элементов, что приводит к понижению надежности.

Цель изобретения — упрощение устройства и повышение надежности его работы, Это достигается тем, что в устройство, содержащее регистр, счетчик тактов, распределитель синхроимпульсов и первый дешифратор, введены блок мультиплексоров, второй и третий дешифраторы, блок триггеров, счетчик байтов, блок управления, причем первый вход блока мультиплексоров является первым входом устройства, второй вход блока мультиплексоров соединен с первым входом второто дешифратора, первым входом блока управления и выходом счетчика тактов, вход счетчика тактов соедикен с первым выходом распределителя синхроимпульсов, второй выход которого соединен со входом третьего дешифратор а, вход распределителя синхроимпульсов соединен с шиной синхроимпульсов, выход третьего дешифратора соединен со вторым входом блока управления и вторым входом второго дешиф780694 ратора, выход которого соединен со вторым входом блока триггеров, первый вход которого соединен с выходом блока мультиплексоров, выход блока триггеров соединен с первым входом регистра, второй вход которого соединен с выходом первого дешифратора, вход которого соединен с выходом счетчика байтов, вход которого соединен с первым выходом блока управления, второй выход которого является первым выходом устройства, третий выход которого является вторым выходом устройства, третий вход блока управления является вторым входом устройства, а также тем, что блок управления содержит триггер и семь элементов И, причем входы первого и второго элементов И соединены с первым входом блока управления, первый, второй и третий входы первого и второго элементов И соединены соответственно с первым, вторым и третьим входами пятого и седьмого элементов И, первый вход четвертого элемента И, первый и четвертый входы соответственно шестого и седьмого элементов И, четвертый вход пятого элемента И соединен со вторым входом блока управления, второй вход четвертого элемента И и нулевой вход триггера соединены и являются вторым входом устройства, выход первого элемента И соединен с первым входом третьего элемента И и со вторым входом шестого элемента И, выход второго элемента И соединен со вторым входом третьего элемента И, выход которого соединен с третьим входом четвертого элемента И, выход четвертого элемента И соединен с D- и Гвходами триггера, выход которого соединен с пятыми входами пятого и седьмого элементов И и с третьим входом шестого элемента И, выход пятого элемента И соединен с первым выходом блока управления, выход шестого элемента И является первым выходом устройства, выход седьмого элемента И является вторым выходом устройства.

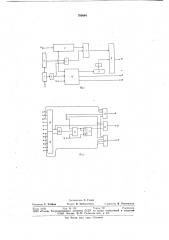

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — схема блока управления.

Устройство содержит распределитель синхроимпульсов 1, счетчик тактов 2, блок мультиплексоров 3, третий дешифратор 4, второй дешифратор 5, первый дешифратор

6, блок триггеров 7, регистр 8, счетчик байтов 9, блок управления 10, первый вход устройства 11, шину синхроимпульсов 12, информационную шину 13, второй вход устройства 14, первый выход устройства 15, второй выход устройства 16, триггер 17, первый элемент И 18, второй элемент И 19, третий элемент И 20, четвертый элемент И

21, пятый элемент И 22, шестой элемент И

23, седьмой элемент И 24.

Устройство ра ботает следующим о бр азом.!

45 случае, когда информация в регистре 8 является последней, поступает на второй вы50

25 зо

35 о

Данные о состоянии элементов устройстза поступают на первый вход блока мультиплексоров 3, где под управлением сигналов от счетчика тактов 2 происходит преобразование состояния контролируемых элементов в последовательный код. Преобразование осуществляется с помощью мультиплексоров, которые разделены на несколько уровней, при этом на мультиплексоры каждого уровня поступают определенные управляющие сигналы от счетчика тактов 2. На информационные входы мультиплексоров первого уровня поступают сигналы от контролируемых элементов.

Выходы мультиплексоров «нижнего» уровня поступают на информационные входы следующего, более «высокого» уровня.

С выхода мультиплексора последнего уровня поступает весь информационный массив в последовательном виде на первь:е входы (D-входы) блока триггеров 7, па вторые входы (V-входы) которого поступают сигналы от второго дешифратора

5. 11а первый вход второго дешифратора 5 пост;пают управляющие сигналы первого уровня от счетчика тактов 2, а на второй вход второго дешифратора поступает временная метка от третьего дешифратора 4.

Таким образом, в блоке триггеров 7 происходит преобразование последовательного кода в параллельный код по байтам, который поступает на первые информационные входы регистра 8.

С поступлением в блок управления 10 по второму входу устройства 14 сигнала начала работы в блоке вырабатываются три сигнала. Первый сигнал изменяет состояние счетчика байтов 9, который с помощью первого дешифратора 6 управляет занесением в регистр 8 байтовой информации. Второй сигнал вырабатывается после заполнения информацией всего регистра 8 и поступает на первый выход устройства

15. Третий сигнал вырабатывается в том ход устройства 16 и по времени совпадает со вторым сигналом, С поступлением сигнала начала работы по второму входу устройства 14 снимается обнуляющий потенциал с триггера

17 и подается разрешающий потенциал на второй вход четвертого элемента И 21.

Триггер 17 устанавливается в единичкое состояние при поступлении самой поздней временной метки от третьего дешифратора

4 и при единичных значениях на входах первого 18 и второго 19 элементов И, что непосредственно предшествует исходному нулевому состоянию счетчика тактов 2, когда начинается преобразование состояния контролируемых элементов в последовательный код. С выхода триггера 17 разрешающий потенциал подается на входы пятого 22, шестого 23 и седьмого 24 эле45

50 ментов И. С выхода пятого элемента И 22, который является первым выходом блока управления, поступает сигнал по необходимой временной метке каждый раз, когда на блоке триггеров 7 сформирован очередной байт. С выхода шестого элемента И

23, который является первым выходом устройства, поступает сигнал по соответствующей временной метке при сформировании на регистре 8 двойного слова в 8 байт. При сформировании последнего двойного слова одновременно с ситналом с выхода шестого элемента И 23 по той же временной метке поступает сигнал с выхода седьмого элемента И 24, который является вторым выходом устройства. Счет двойных слов осуществляется путем дешифрации на седьмом элементе И 24 кода с входов второго элемента И 19.

Формула изобретения

1. Устройство для управления вводомвыводом информации, содержащее регистр, соединенный с информационной шиной, первый дешифратор, распределитель синхроимпульсов и счетчик тактов, о т л ич а ю щ е е с я тем, что, с целью упрощения и повышения надежности устройства, в него введены блок мультиплексоров, второй и третий дешифраторы, блок триггеров, счетчик байтов, блок управления, причем первый вход блока мультиплексоров является первым входом устройства, второй вход блока мультиплексоров соединен с первым входом второго дешифратора, первым входом блока управления и выходом счетчика тактов, вход которого соединен с первым выходом распределителя синхроимпульсов, второй выход которого соединен со входом третьего дешифратора, вход распределителя синхроимпульсов соединен с шиной синхроимпульсов, выход третьего дешифратора соединен со вторым входом блока управления и вторым входом второго дешифратора, выход которого соединен со вторым входом блока триггеров, первый вход которого соединен с выходом блока мультиплексоров, выход блока триггеров соединен с первым входом регистра, 5

10 !

40 второй вход которого соединен с выходом первого дешифратора, вход которого соединен с выходом счетчика байтов, вход которого соединен с первым выходом блока управления, второй выход которого является первым выходом устройства, третий выход которого является вторым выходом устройства, третий вход блока управления является вторым входом устройства.

2. Устройство по п. 1, отл и ч а ю ще ес я тем, что блок управления содержит триггер и семь элементов И, причем входы первого и второго элементов И соединены с первым входом блока управления, первый, второй и третий входы первого и второго элементов И соединены соответственно с первым, вторым и третьим входами пятого и седьмого элементов И, первый вход четвертого элемента И, первый и четвертый входы соответственно шестого и седьмого элементов И, четвертый вход пятого элемента И соединен со вторым входом блока управления, второй вход четвертого элемента И и нулевой вход триггера соединены и являются вторым входом устройства, выход первого элемента И соединен с первым входом третьего элемента И и со вторым входом шестого элемента И, выход второго элемента И соединен со вторым входом третьего элемента И, выход которого соединен с третьим входом четвертого элемента И, выход четвертого элемента И соединен с 0- и V-входами триггера, выход которого соединен с пятыми входами пятого и седьмого элементов И и с третьим входом шестого элемента И, выход пятого элемента И соединен с первым выходом блока управления, выход шестого элемента И является первым выходом устройства, выход седьмого элемента И является вторым выходом устройства.

Источники информации, принятые во внимание при экспертизе:

1; Электронная вычислительная машина ЕС-1050. Под ред. А. М. Ларионова, N,, «Статистика», 1976, с, 113 — 114.

2. Электронная вычислительная машина ЕС-1030. Под ред, А. М. Ларионова, М,, «Статистика», 1977, с. 207 †2 (прототип).

780694

Составитель С. Галин

Техред И. Заболотнова

1;оррсктор И. Осиповская

Редактор Е. Хейфиц

Тип. Харьк. фил. пред. «Патент»

Заказ 18/29 Изд. № 100 Тирагк 731 Подписное.

НПО «Поиск» Государственного комитета СССР по делам изобретений н открытий

1 13035. Москва. Ж-35. Раун>ская наб., д. 4/5