Преобразователь сдвига фаз в цифровой код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

< >781708 (61) Дополнительное к авт. свид-ву (22) Заявлено 14.12.78 (21) 2695245/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 23,11,80. Бюллетень ¹ 43

Дата опубликования описания 251180 (51)M. Кл.

G 01 R 25/08//

Н 03 К 13/20

Государственный комитет

СССР по делам изобретений н открытий (53) УДК 621. 317. . 77 (088. 8) (72) Авторы изобретения и

Ф й

А.Б. Иоаннисиан и В.А. Фольц (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ СДВИГА ФАЗ

В ЦИФРОВОЙ КОД.Изобретение относится к цифровой измерительной технике и может быть использовано в автоматизированных контрольно-испытательных системах для измерения сдвига фаз в цепях радиоэлектронных устройств и систем автоматики.

Известен цифровой фаэометр, содержащий формирующие устройства, логические элементы, счетчики, генератор квантующих импульсов, делители частоты и блок управления. Фазометр обеспечивает одновременное измерение периода и временного сдвига исследуе" мых колебаний с последующим автома- 15 тическим преобразованием этих двух измерений в непосредственный отсчет измеряемого фазового сдвига и градусах с помощью двоичных умножителей частоты f1). 20

Недостатками устройства являются сложность схемной реализации и дополнительная погрешность измерений, обусловленная погрешностью работы двоичных умножителей частоты, реальное время измерения существенно превышает период исследуемых колебаний.

Известно также цифровое устройство для измерения сдвига фаз, содержа«. щее формирователи импульсов опорного 30 и фазоманипулированного сигналов, два счетчика, три логических элемента И, логический элемент ИЛИ, генератор образцовой частоты, схему задержки, блок управления, делитель частоты, два управляемых делителя частоты и две вентильные группы, причем генератор образцовой частоты через первый и второй логические элементы И соединен с двумя управляемыми делителями частоты и одновременно через делитель частоты и первый счетчик — с первыми входами вентильных групп, выход каждой иэ которых соединен с управляемым делителем частоты, выходы делителей подключены через последовательно соединенные логический элемент ИЛИ и третий логический элемент И, второй вход которого через схему задержки подключен к выходам формирователей импульсов, ко второму счетчику, а блок управления соединен с формирова- телем импульсов опорного сигнала, со вторыми входами вентильных групп, входами управляемых делителей частоты, с первым и вторым логическими элементами И и с двумя счетчиками (2).

Недостатками устройства являются сравнительно большое реальное время измерения, составляющее до двух пе781708! 4 риодов исследуемого напряжения, и сложность схемной реализации, обусловленная двухтактным режимом рабо-„ ты устройства и необходимостью применения широкополосной схемы задержки. Кроме того, устройство имеет дополнительную погрешность преобразования, зависящую от параметров схемы задержки, частоты исследуемого напряжения и величины сдвига фаз.

Цель изобретения — повышение кочности измерения и быстродействия.

Цель достигается тем, что в преобразователь сдвига фаэ в цифровой код, содержащий два формирователя ... импульсов, первый из которых соединен с первым входом блока управления, ри логических элемента И, генератор об раэцовой частоты, выход которого через делитель частоты и первый счетчик соединен с первым входом вентильной группы, соединенной по входу с управляемым делителем частоты, и второй счетчик, вход которого подключен к выходу одного из логических элементов И, связанного по входу с выходом блока управления, введены реверсивный счетчик и выходной регистр, причем первый выход первого формирователя импульсов подключен к управляющим входам первого счетчика и реверсивного счетчика, второй выход первого формирбвателя импульсов подключен ко второму входу вентильной группы и к управляющему входу второго счетчика, первый и второй выходы второго формирователя импульсов соединены соот ветственно с третьим и четвертым входами блока управления, первый и второй выходы которого подключены к первым входам второго и третьего логических элементов И, соединенных вторыми своими входами с выходом делителя частоты, а выходами — со входами прямого и обратного счета реверсивного счетчика, выход которого под ключен ко второму входу первого логического элемента И, третий вход ко" торого соединен через управляемый де-литель частоты с выходом генератора образцовой частоты, четвертый и.пятый выходы блока управления"подключены ко входам выходного регистра, соединенного с выходом второго счетчика.

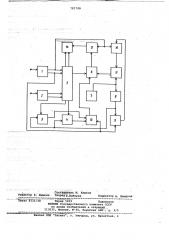

На чертеже приведена функциональная схема преобразователя.

Преобразователь сдвига фаз в цифровоЯ код содержит первый формирователтФ 1 импульсов, второй формирователь 2 импульсов, блок 3 управления, логические элементы 4-6 И,-генератор 7 образцовой частоты, делитель 8 частоты, первый счетчик 9, вентильную группу 10, управляемый делитель

11 частоты, второй счетчик 12, реверсивный счетчик 13 и выходной регистр 14.

Преобразователь работает следующим образом.

Опорное напряжение 0 подается на вход формирователя 1, на первом выходе которого формируется последовательность А коротких импульсов, соответствующих моментам положительных переходов напряжения Uo„ через ноль, на втором выходе — последовательность

В коротких импульсов, соответствующих моментам отрицательных переходов напряжения Uo„ через ноль. Исследуемое напряжение U фазовый сдвиг У„

1О которого измеряется, подается на вход формирователя 2, на первом и втором выходах которого формируются соответственно последовательности С и D коротких импульсов, аналогичные по15 следовательностям A и В.

Каждый импульс последовательности А сбрасывает в ноль счетчик 9, который подсчитывает число импульсов частоты счета Е„ за интервал времени, щ Равный пеРиоду Т „ опорного напряжения. Одновременно импульс последовательности А сбрасывает в ноль реверсивный счетчик 13, который подсчитывает число импульсов частоты счета Е„ за интервал времени ск, пропорциональный фаэовому сдвигу Ю„ . Частота счета f в и раз меньше образцовой часто1 ты f генератора 7 (и — коэффициент

О деления делителя 8 частоты}. В ин.тервале между очередными импульсами последовательностей А и В на первом выходе блока 3 управления формируется управляющий импульс, длительность которого равна t . Этот импульс разк решает прохождение через логический

З5 элемент И импульсов частоты счета на вход прямого счета реверсивного счетчика 13, при нулевом содержании которого на первый вход логического элемента И 6 поступает сигнал запре4Q та.

Таким образом, в течение положительного полупериода U<> счетчик 9 подсчитывает число импульсов й„ частоты f а реверсивный .счетчик 13—

4 число импульсов М той же частоты, пропорциональное Ч„ . С приходом очередного импульса йоследовательности В содержимое второго счетчика 12 переносится в выходной регистр 14.

Одновременно через вентильную группу 10 в управляемом делителе 11 устанавливается коэффициент деления равный N„, а со второго и третьего выходов блока 3 на логические элементы 5 и б И поступают разрешающие сигналы. При этом на вход второго счетчика 12 проходят импульсы частоты счета Е = f /N<, а на вход обратноо го счета реверсивного счетчика 13 проходят импульсы частоты счета

Щ Логический элемент б И закрывается при достижении реверсивным счетчиком 13 нулевого состояния, т.е. когда на вход обратного счета этого счетчика поступает число импульсов

65 частоты счета Е„ равное М . Посколь781708 ку обратный счет осуществляется в реверсивном счетчике 13 с той же частотой f„, что и прямой счет, то состояние счетчика от и до нуля изме2. няется за время t . Поэтому число имX. пульсов, подсчитанное счетчиком 12, пропорционально фазовому сдвигу Ч и не зависит от частоты исследуемых напряжений, 30

to 2n

2п

Ъ N То„x, x

При коэффициенте деления делителя

8 n=180 число импульсов и, подсчитанное счетчиком 12, соответствует фазовому сдвигу исследуемых напряжений в градусах. 15

Информация о знаке фазового сдвига поступает в выходной регистр с четвертого и пятого выходов блока 3.

Реальное время преобразования сдвига фаз в цифровой код не превышает одного периода опорного напряжения, а дополнительная погрешность преобразования, обусловленная задержкой импульса, длительность которого пропорциональна сдвигу фаз, отсутствует.

Схемная реализация преобразователя существенно упрощается благодаря ис,ключению сложной схемы задержки и управляемого делителя с вентильной группой, содержащих около половины Общего числа элементов.

Введение новых элементов — реверсивного счетчика и выходного регистра, и новых связей выгодно отличает предлагаемый преобразователь сдвига фаэ в цифровой код от известного уст- З5 ройства, так как позволяет вдвое увеличить быстродействие преобразователя, уменьшить погрешность измерения и, примерно в два раза, снизить стоимость преобразователя, благодаря уп- Щ рощению его схемной реализации. Кроме того, в предлагаемом преобразова, теле код фазового сдвига при каждом измерении хранится в выходном регистре в течение периода опоРного наПРЯ- .45 жения, что позволяет существенно улучшйть процесс вывода информации.

Предлагаемый преобразователь используется как при создании высокоточных цифровых фазометров, так и в составе автоматизированных испытательных сис-, тем для контроля и исследования фазовых характеристик сложных радиоэлектронных устройств и систем автоматики при существенном непостоянстве перйо да исследуемых напряжений.

Формула изобретения

Преобразователь сдвига фаз в цифровой код, содержащий два формирователя импульсов, первый из которых соединен с первым входом блока управления,три логических элемента И, генератор образцовой частоты, выход которого через делитель частоты и первый счетчик соединен с первым входом- —вентильной группы, соединенной по входу с управляемым делителем частоты, и второй счетчик, вход которого подключен к выходу одного из логических элементов И, связанного по входу с выходом блока управления, о т л ич а ю шийся тем, что, с целью повышения точности измерения и быстродействия, в него введены реверсивный счетчик и выходной регистр, причем первый выход первого формирователя импульсов подключен к управляющим входам первого счетчика и реверсивного счетчика, второй выход первого формирователя импульсов подключен ко второму входу вентильной группы и к управляющему входу второго счетчика, первый и второй выходы второго формирователя импульсов соединены соответственно с третьим и четвертым входами блока управления, первый и второй выходы которого подключены к первым входам второго и третьего логических элементов И, соединенных вторыми своими входами с выходом делителя частоты, а. выходами — со входами прямого и обратного счета реверсивного счетчика, выход которого подключен ко второму входу первого логического элемента И, третий вход которого соединен через управляемый делитель частоты с выходом генератора образцовой частоты, четвертый и пятый выходы блока управления подключены ко входам выходного регистра, соединенного с выходом второго счетчика.

Источники информации, принятые во внимание при экспертизе

Яетальников В.В. и др. Быстродействующий цифровой фазометр. — "Автометрия", 1971, Р 4 с. 116-121.

2 ° Авторское свидетельство СССР

В 532059, кл. С 01 R 25/08, 1974.

781708

Составитель. М. Клыков

Редактор Е; Шишкин техреад йа.Бабурина

Корректор Н. Швыдкая аакаа 8121/48 Тираж 1819 Подписное

BHHHOH Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 кааа44аа4ка

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4