Арифметическое устройство

Иллюстрации

Показать всеРеферат

О И С А Н И Е („)781808

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свнд-ву (51) M. Кл.

G 06 F 7/38 (22) Заявлено 14.12.78 (21) 2734114/18-24 с рисоединенном заявки ¹

Государственный комнтет (28) Приоритет по делам нзобретеннй н открытнй

Опубликовано 23.11.80. Бюллетень ¹43

Дата опубликования описания 23.11.80 (53) УДК681.325 (088.8) (72) Авторы изобретения

Е. В. Власова и Э. С. Каташков (71) Заявитель

Всесоюзный научно-исследовательский и конструкторский институт научного приборостроения (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах, в системах регистрации, обработки и хранения цифровых данных, в частности, в системах для научных исследований.

Известны арифметические устройства, содержащие блок управления, входной и оперативный регистры, выходы которых соединены через переключатели и сумматоры со входами (Ej

Однако в этих устройствах для нахождения наименьшего общего кратного двух чисел необходимо проводить серию пробных делений или хранить в ЗУ таблицы простых чисел„что сильно усложняет аппаратуру.

Наиболее близким к предлагаемому является арифметическое устройство, содержащее

15 блок управления, входной и оперативные регистры, сумматор, выходы которых через пере- ключатели соединены со входами сумматоравычитателя (2) .

Однако устройство для нахождения наименьшего общего кратного двух чисел должно иметь в ЗУ таблицу простых чисел или проводить серию пробных делений.

Цель изобретения — повышение быстродействия преимущественно в операциях нахождения наименьшего общего кратного.

Поставленная цель достигается тем, что в арифметическое устройство, содержащее блок управления, выходы которого соединены со входами входного регистра и выходом сумматора-вычитателя, первый и второй оперативные регистры, сумматор, первый, второй, третий, четвертый переключатели и линию задержки, причем вход первого оперативного регистра подключен к подвижному контакту второго переключателя, а выход подключен к первому и через элемент задержки — ко второму входам сумматора, выход которого соединен с замыкающим контактом второго переключателя, размыкающий контакт которого подключен к выходу сумматора-вьтчнтателя и раэмыкающему контакту третьего переключателя, подвижный контакт которого соединен со входом второго оперативного регистра, выход которого соединен с подвижным контактом четвертого переключателя, размыкающий контакт которого соединен с замыкающим контак3 78 том третьего переключателя, а замыкающий контакт четвертого переключателя соединен с замыкающим контактом первого переключателя. размыкающий контакт которого подключен к выходу входного регистра, а подвижный кон такт подключен к первому входу сумматоравычитателя, введены счетный регистр, буферный регистр, пятый и шестой переключатели, причем вход счетного регистра соединен с выходом сумматора-вычитателя, а выход подключен к подвижному контакту пятого переключателя, замыкающий контакт которого соединен с входом буферного регистра, выход которого соединен с замыкающим контактом четвертого переключателя, размыкающий контакт пятого переключателя соединен с размыкающим контактом шестого переключателя, замыкающий контакт которого соединен с выходом сумматора, а подвижный контакт шестого переключателя подключен ко второму входу сумматора- вычитателя.

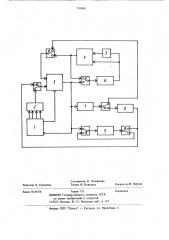

На чертеже приведена блок-схема устройства.

Устройство содержит блок 1 управления, входной регистр 2, сумматор-вычитатель 3, сумматор 4, линию задержки 5, первый оперативный регистр 6, счетный регистр 7, буферный регистр 8, второй оперативный регистр 9 и переключатели 10 — 15, причем выход сумматора

4 подключен ко второму входу сумматоравычитателя 3 и через переключатель — к первому оперативному регистру 6, выход которого связан с первым входом сумматора 4 и через линию 5 задержки — со вторым входом сумматора 4, выход второго оперативного регистра

9 через переключатели связан с выходом сумматора-вычитателя 3, а выход через два последовательно соединенных переключателя соединен с первым входом сумматора-вычитателя 3, выход сумматора-вычитателя 3 подключен ко входу счетного регистра 7, выход которого соединен через переключатель с входом буферного регистра 8, выход которого подключен через переключатель к первому входу сумма; тора-вычитателя 3, второй вход сумматоравычитателя 3 через два последовательно соединенных переключателя связан с выходом счетного регистра 7.

Устройство работает следующим образом.

В режиме определения периода разложения обратной величины числа первое число записывается в оперативном регистре 9. Находится ближайшее значение 2, большее заданного числа.

Для этого в младшем разряде входного регистра 2 устанавливается "Г, которая через переключатели 10 и 12 и сумматор-вычитатель 3 передается в оперативный регистр 6 и через цепочку, состоящую иэ линии 5 задержки,, сумматора 4 и переключателя 11, поступает на первый вход сумматора-вычитателя 3. На вто20

Ю

55 ных регистров 6 и 9. Если разность отрицательна, происходит двоичный сдвиг числа в оперативном регистре б через цепочку 4-12-6-5 (умножение на 2 и на выход подается сигнал

"0"). Положительная разность через второй контакт переключателя 12 записывается в оперативный регистр 6. На выходе сигнал "1".

Разность умножается на 2 (цепочка 5 — 4) и снова подается на вход сумматора-вычитателя 3.

Данный цикл заканчивается, когда разность на выходе сумматора-вычитателя 3 станет равна 1, Число операции на сумматоре-вычитателе 3 фиксируется на счетном регистре 7 и определяет период разложения обратной величины числа (ПРОВ) .

Когда процесс разложения обратной величины числа заканчивается, содержимое счетного регистра 7 через переключатель 14 переписывается в буферный регистр 8. Таким образом в буферном регистре 8 запоминается период разложения обратной величины первого числа.

В таком же порядке происходит определение периода разложения обратной величины второго числа. Результат остается в счетном регистре 7.

В режиме определения периода разложения наименьшего общего кратного двух чисел происходит сравнение содержимого буферного регистра 8 и счетного регистра 7. Если периоды разложения обратных величин чисел кратны, то период разложения наименьшего общего кратного равен большему периоду разложения, если кратности нет — определяется обратная величина дополнительного множителя.

Сравнение производится в сумматоре-вычитателе 3. На первый вход сумматора-вычитателя 3 подается период разложения обратной величины второго числа со счетного регистра 7 через переключатели 14 и 11, На второй вход с буферного регистра 8 через переключатель 10 подается период разложения обратной величины первого числа. Если разность периодов положительна, то период разложения обратной величины первого числа с буферного регистра 8 через переключатель 10, сумматор-вычитатель 3 и переключатель 13 переписывается в оперативный регистр 9, а период разложения обратной величины второго числа со счетного регистра 7 через переключатели 14 и 11, сумматор-вычитатель 3 и переключатель 12 переписывается в оперативный регистр 6. Если разность периодов разложения обратных величин отрицательна, то период разложения обратной величины первого числа с буферного регистра 8 через переключатель 10, сумматор-вычитатель 3 и пере1808 рой вход сумматора вычитателя 3 через переключатели 10 и 15 поступает число из опера- тивного регистра 9. В сумматоре-вычитателе 3 происходит сравнение содержимого оператив781808 ключатель 12 переписывается в оперативный регистр 6, а период разложения обратной величины второго числа со счетного регистра 7 через переключатели 14 и 11, сумматор-вычитатель 3 и переключатель 10 переписывается в оперативный регистр 9.

В сумматоре-вычитателе 3 происходит последовательное вычитание меньшего периода разложения обратной величины числа, записанного в оперативном регистре 9, из большого, запи- IÎ санного в оперативном регистре 6. Если разность равна нулю, периоды разложения обратных величин чисел кратны и период разложения обратной величины наименьшего общего кратного равен большему периоду разложения. Если раз- 13 ность отрицательная, то дальнейшая работа схемы аналогична режиму определения периода разложения обратной величины числа, с тем отличием, что сравнение разницы на выходе сумматора-вычитателя 3 происходит не с "1", эп а с начальной разностью, На выходе схемы можно получить период разложения обратной величины дополнительного множителя для большего периода разложения обратной величины.

Технико-экономические преимущества пред- 2с лагаемого устройства состоят в том, что дополнение арифметического устройства счетным регистром 7, буферным регистром 8 и двумя переключателями 11 и 14 позволяет выполнять подготовительные операции, необходимые для вычисления наименьшего общего кратного двух или последовательных пар чисел, не производя серий делений, и не требует памяти простых чисел, а следовательно, облегчает реализацию этих операций во встроенных микропроцессо- 3 рах систем для обработки экспериментальных данных. Так, например, при работе с 8-разрядными десятичными числами необходимо хранить в ЗУ 6 10 простых чисел, для чего необ6 ходима память 10 + 20 Мб, а объем одного < пакета магнитных дисков ЕС вЂ” 5052 равен

7,25 Мб.

Формула изобретения

IS

Арифметическое устройство, содержащее блок управления, выходы которого соединены со входами входного регистра и выходом сумматора-вычитателя, первый и второй оперативные регистры, сумматор, первый, второй, третий, четвертый переключатели и линию задержки, причем вход первого оперативного регистра подключен к подвижному контакту второго переключателя, а выход подключен к первому и через элемент задержки — ко второму входам сумматора, выход которого соединен с замыкающим контактом второго переключателя, размыкающий контакт которого подключен к выходу сумматора-вычитателя и размыкающему контакту третьего переключателя, подвижный контакт которого соединен со входом второго оперативного регистра, выход которого соединен с подвижным контактом четвертого переключателя, размыкающий контакт которого соединен с замыкающим контактом третьего переключателя, а замыкающий контакт четвертого переключателя соединен с замыкающим контактом первого переключателя, размыкающий контакт которого подключен к выходу входного регистра, а подвижный контакт подключен к первому входу сумматора-вычитателя, о тличающее ся тем, что, с целью ловышения быстродействия, в него введены счетный регистр, буферный регистр, пятый и шестой переключатели, причем вход счетного регистра соединен с выходом сумматора-вычитателя, а

/ выход подключен к подвижному контакту пятого переключателя, замыкающий контакт которого соединен с входом буферного регистра, выход которого соединен с замыкающим контактом четвертого переключателя, размыкающий контакт пятого переключателя соединен с раэмыкающим контактом шестого переключателя, замыкающий контакт которого соединен с выходом сумматора, а подвижный контакт шестого переключателя подключен ко второму вхоДу сумматора-вычитателя.

Источники информации, принятые во внимание при экспертизе

1. Патент США N 3739162, кл. 235 †1, 1971.

2. Авторское свидетельство СССР Р 416692, кл. 6 06 F 7/38, 1974 (прототип).

781808

Составитель Н. Измайлова

Техред Н. Ковалева

Корректор М. Вигула

Редактор В. Еремеева

Подписное

Тираж 751

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д, 4/5

Заказ 813б/54

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4