Устройство для поиска кратных неисправностей в однотипных логических блоках

Иллюстрации

Показать всеРеферат

Союз Советских

Социопистическнк

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< >781816

1

l (61) Дополнительное к авт. свил-ву

3 (51) М. Кл.

G 06 F 11/22 (22) Заявлено 24.04,78 (21) 2629010/18 — 24 с присоелииенкем заявки М (23) Приоритет

Государственный комитет но делам изобретений и открытий (5З) УЛ К681.326.7 (088.8) Опубликовано 23.11,80. Бюллетень A 43

Дата опубликования описания 23.11.80 (72) Авторы изобретения

В. А. Киэуб, А. В. Моэгалевскнй и С. Н, Никифоров

1 а2

1.

Ленинградский ордена Ленина электротехнлческик институт,,...„1 им. В. И. Ульянова (Ленина) (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ ПОИСКА КРАТНЫХ НЕИСПРАВНОСТЕЙ

В ОД11ОТИПНЫХ ЛОГИЧЕСКИХ БЛОКАХ

Изобретение относится к контролю устроиств вычислительной техники и может быть использовано для нахождения кратных неисправностей в однотипных логических блоках ЦВМ.

Известны устройства поиска кратных неисправностей в однотипных логических блоках, в которых обнаружение кратных неисправностей основано на том, что процедура поиска осуществляется, как правило, для одного объекта и прекращается после обнаружения первой неисправности. Возобновляется процедура .после уст- тв ранения обнаруженной неисправности, так как в противном случае возможен эффект компенсации неисправностей. Это ведет, в свою очередь, к неоднозначности диагноза, т.е. Устаиов пению места предполагаемого дефекта (1) и (21 °

Наиболее близким техническим решением к предлагаемому является устройство поиска кратных неисправностей в логических блоках, которое позволяет отыскивать кратные неисцрав. ности одновременно в М объектах, что повы, шает производительность труда и сокращает аппаратурные затраты. Устройство содержит ге2 ператор импульсов, связанный с первым входом элемента И непосредственно, со входом элемента ИЛИ и с шинами сброса генератора тестов, счетчика импульсов и триггера последнего разряда счетчика импульсов — через нормально разомкнутые контакты кнопки

"Сброс", а с единичным входом триггера останова, нулевой вход которого подключен к выходу элемента ИЛИ вЂ” через нормально разомкнутые контакты кнопки "Пуск", элемент

И, второй вход которого связан с единичным выходом триггера останова, а выход подключен ко входам счетчика импульсов, выходы которого соединены с цифровым индикатором, и генератор тестов, выходы которого связаны с идентичными входами проверяемых блоков, индикатор исправности, вход которого соединен со входом цифрового индикатора и с единичным выходом триггера последнего разряда, счетчика импульсов, нулевой выход которого подключен к третьему входу элемента И, элементы несовпадения, входы которых подсоединены к идентичным выходам проверяе. мых блоков, а выходы связаны со входами

3 . 781816 элемента ИЛИ и индикаторами несовпадения, кроме того двухвходовой элемент несовпадения входы которого свободны, а выход подключен к индикатору несовпадения и ко входу элемента ИЛИ (3J

20

30

Однако это устройство имеет недостаток, заключающийся в том, что после обнаружения неисправности в одном иэ проверяемых блоков йоиск прекращается, обнаруженная неисправность устраняется, после чего процедура повторяется, что увеличивает суммарное время поиска всех неисправностей во всех проверяемых блоках.

Цель изобретения — повышение производительности труда при поиске кратных неисправностей в N объектах за счет сокращения суммарного времени поиска, Поставленная цель достигается тем, что в устройство для поиска кратных неисправностей в одйотйлных логических блоках, Содержащее блок управления, счетчик, генератор тестов, блок индикации, и коммутаторов и и схем сравнения, причем тактовый выход блока управления соединен со счетными входами счетчика и генератора тестов, командный выход блока управления соединен с установленными входами счетчика и генератора тестов, йнформа. ционные выходы которого соединены с одноименными входами проверяемых блоков, выходы каждого проверяемого блока соединены со входами соответствующего коммутатора, одноименные выходы каждого коммутатора соединены с соответствующими входами соответствующей схемы сравнения, выходы всех схем сравнения образуют группу входов блока управления, информационные выходы счетчика соединены с первой группой входов блока индикации, вторая группа входов которого сое- диНена с выходами коммутаторов, выход переполнения счетчика соединен с первым входом блока управления, введен пульт управления, . каждый выход которого соединен с соответствующим управляющим входом всех схем сравйения.

Устройство реализует процедуру поиска неисправностей, при которой останов теста и повтор сначала производится не после обнаружения и устранения первой неисправности в каком-либо из проверяемых блоков, а после обнаружения и устранения по одной неисправности в каждом из N проверяемых блоков.

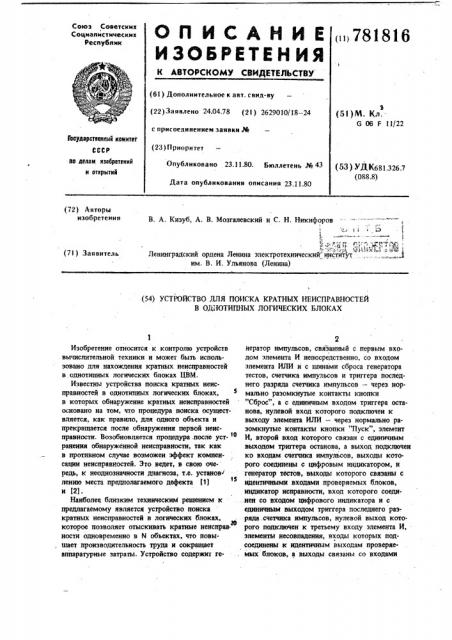

На фиг. 1, 2 и 3 схематически представлено функционирование элементов неравнозначности йульта управления, принцип работы йредлагаемого устройства и его схема.

На фиг. 1 N проверяемых блоков 1 соединейы "своими одноименными входами и подключены к выходам генератора 2 тестов. Счетный вход генератора 2 тестов соединен со счетным лФЮФ4 входом счетчика 3 импульсов и подключен к тактовому выходу блока 4 управления. Аналогично управляющий вход генератора 2 тестов соединен с управляющим входом счетчика

3 и управляющим выходом блока 4 управления. Выходы разрядов счетчика 3 подсоединены ко входам блока 5 индикации, причем выход переполнения счетчика 3, кроме того, подключен к первому входу блока 4 управления.

Входы N входовых схем 6 сравнения подключены ко входам блока 5 индикации и через коммутаторы 7 — к одноименным выходам проверяемых блоков 1, а выходы — ко входам блока 4 управления. Управляющие входы схем

6 сравнения объединены и подключены к выходам пульта 8 управления.

Устройство работает следующим образом, По команде оператора блок 4 управления вырабатывает на командном выходе сигнал, по которому устанавливаются в нулевое состояние генератор 2 тестов и счетчик 3 импульсов.

Затем по команде оператора блок 4 управления начинает на тактовом выходе вырабатывать тактовые импульсы, поступающие на счетные входы счетчика 3 и генератора 2 тестов, который выдает проверяющие воздействия на входы проверяемых блоков 1. В случае исправности всех проверяемых блоков 1 сигналы на одноименных выходах этих блоков совпадают между собой и через коммутаторы 7 подаются на схемы 6 сравнения, которые не вырабатывают импульсов на своих выходах, Блок 4 управления прекращает подачу тактовых им- . пульсов только по сигналу переполнения счетчика 3, который достигает максимального числа, соответствующего длине теста. Это число фиксируется блоком 5 индикации. Если на каком-либо к-ом выходе любого из проверяемых блоков 1 на i-ом такте появляется сигнал, не совпадающий с сигналами на к-ых выходах остальных проверяемых блоков 1, то срабатывает к-ая схема 6 сравнения. Выходной сигнал к-ой схемы 6 сравнения прекра щает поступление тактовых импульсов из блока 4 управления в узлы устройства. При этом блок 5 индикации фиксирует номер такта, на котором впервые зарегистрировано несовпадение выходных сигналов проверяемых блоков 1, что соответствует позиции неисправного элемента в одном из проверяемых блоi ков 1. Определение проверяемого блока 1, неисправность которого обнаружена, производится с помощью блока 5 индикации, Так как схема всего устройства зафиксирована в момент несовпадения выходных сигналов проверяемых блоков 1, то на выходах проверяемых блоков 1 сохраняются логические сигналы ("0" или "1"), характеризующие состоянйе каждого иэ проверяемых блоков 1.

781816 6 блоков 1. обнаруживается за меньшее время.

Следовательно, производительность труда при в поиске неисправностей с использованием предлагаемого устройства выше.

Эти сигналы представляются оператору в виде и и-мерных двоичных кодов блока 5 индикации, где N -- число проверяемых блоко

1, а и — число из выходов. Сравнивая эти коды между собой, оператор устанавливает код, а следовательно, и проверяемый блок 1, который отличен QT других. При этом процесс определения неисправного проверяемого блока 1 может быть основан либо на использовании эталонного проверяемого блока 1, либо на мажоритарном принципе. Определив таким образом неисправный проверяемый блок 1, оператор отключает его с помощью пульта 8 управления,выполненного на ключах 9, предварительно зафиксировав номер неисправного элемента 1 по показанию блока 5 индикации. Отключение

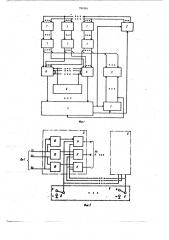

j-го проверяемого блока 1 представляет собой перестроение всех N-входовых схем 6 сравнения путем подачи на их управляющие входы отрицательного потенциала в (N — 1) -входовые схемы 6 сравнения. Этот процесс иллюстрируется на фиг, 2 для трехвходовых схем 6 сравнения, состоящих из сумматоров 10 по модулю два и элементов И 11.

Затем, не производя первоначальной установки в "0" узлов устройства, оператор осуществляет повторной пуск. Поступление тактовых импульсов из блока 4 управления в генератор 2 тестов и счетчик 3 импульсов приводит к продолжению подачи тестовых воздействий на оставшиеся N — 1 проверяемые блоки 1.

При обнаружении первой неисправности в одном из И вЂ” 1 оставшихся проверяемых блоков 1 процедура повторяется. И так до обнаружения по одной неисправности в каждом из N проверяемых блоков 1, После этого все обнаруженные неисправности устраняются.

После этого все схемы 6 сравнения снова перестраиваются пультом 8 управления в

N-входовые и цикл повторяется, Так продолжается до обнаружения и устранения всех неисправностей в проверяемых блоках 1.

Таким образом, в предлагаемом устройстве то же число неисправностей N проверяемых

Формула изобретения

Устройство для поиска кратных неисправностей в однотипных логических блоках, содер1 жащее блок управления, счетчик, генератор тестов, блок индикации, и коммутаторов и и схем сравнения, причем тактовый выход блока управления соединен со счетными входами счетчика и генератора тестов, командный выход

/ блока управления соединен с установленными входами счетчика и генератора тестов, информационные выходы которого соединены с одноименными входами проверяемых блоков, выходы каждого проверяемого блока соединены со входами соответствующего коммутатора, одноименные выходы каждого коммутатора соединены с соответствующими входами соответствующей схемы сравнения, выходы всех схем сравнения. соединены со входами блока управления, информационные выходы счетчика соединены с первой группой входов блока индикации, вторая группа входов которого соединена с выходами коммутаторов, выход переполнения счетчика соединен с сигнальным входом блока управления, о т л и ч а ю щ ее с я тем, что, с целью повышения производительности, в устройство введен пульт управления, каждый выход которого соединен с соответствующим управляющим входом всех схем сравнения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельогво СССР N 238236, кл. G 06 F 15/46, 1967.

2. Авторское свидетельство СССР Н 538894, кл. G 01 R 31/28, 1976, 3. Авторское свидетельство СССР по заявке

Р 2365586/24, кл. G 06 F 11/04; 1976 (прототип) .

7818)б

Составитель И. Сигналов

Техред Н. Ковалева

Тираж 751

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Корректор М. Вигула

Редактор И. Николайчук

Подписное

Заказ 813б/54

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4