Узловой элемент сеточной модели

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<ц781842

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 190279 (21) 2745089/18-24 (51)М. Кл. с присоединением заявки М

G G 7/46

Государственный комитет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 2 1 80, Бюллетень М9 4З (5Ç) УЛК 681. ззз (088. 8) Дата опубликования описания 251180

Г.Н. Азаров, В.М. Андриевский, В.В. Гармаш и В.Е. Прокофьев (72) Авторы изобретения

Харьковский ордена Ленина политехнический институт им. В.И. Ленина (71) Заявитель ) 1» ( — 1 (54) УЗЛОВОЙ ЭЛЕМЕНТ СЕТОЧНОЙ МОДЕЛИ - ы;т 1.,!

Изобретение относится к аналоговой и гибридной вычислительной технике и может быть использовано при построении автоматизированных сеточных интеграторов для моделирования урав- 5 нений математической физики и для решения задач управления объектами с распределенными параметрами.

Известно устройство для моделирования функционального сопротивления, f0 содержащее арифметический блок, преобразователь напряжение-Код, блок синхронизации, преобразователь кодсопротивление, выполненные в виде последовательно соединенных резисторов, 15 параллельно которым подключены ключи, регистр памяти, блок памяти, блок разрешения записи 11 .

Недостаток устройства — обязательное применение большого количества 20 прецизионных резисторов для получении достаточной точностй задания величины сопротивления при малой дискретности. В связи с этим возрастает сложность схем управления резисторами, 25 снижается технологичность, увеличивается стоимость и габариты узлового элемента.

Наиболее близким техническим решением к предлагаемому является узлорой элемент сеточной модели, содержащий блок проводимости, входы кото- рого соединены с выходами блока управления, первый вход которого подключен к выходу программного блока, блок аналоговой памяти, ключи блока слежения и блок развязки (2).

Однако для получения малой дискрет1 ности величины проводимости в требуемом диапазоне необходимо большое количество цепочек, состоящих из прецизионного резистора и ключа. В связи с чем усложняется схема управления ключами, возрастают габариты и стоимость узлового элемента, что имеет решающее значение при построении многомерных сеточных моделей с большим числом узлов. Для поддержания постоянной разности потенциалов между источком и затвором МОП-ключа, в целях исклЮчения зависимости сопротивления открытого канала полевого транзистора от потенциала узла, требуется сложная схема управления, включающая четыре взаимосвязанных блока. Сопротивление открытого канала транзистора зависит от величины проходящего тока, что отрицательно сказывается на точности. Аналоговая память сложна в технической реализации и не обес781842 печивает высокой стабильности хранимого параметра, поэтому наличие блока аналоговой памяти не только усложняет схему узлового элемента, но и снижает его точность.

Цель изобретения — упрощение схемы и повышение точности- узлового элемента.

Указанная цель достигается тем, что в узловой элемент сеточной модели, содержащий блок проводимости, вхо-(g ды которого соединены с выходами блока управления, первый вход которого подключен к выходу программного блока, введены блок формирования относительной длительности импульса, сглаживающая емкость и блок линеаризации, включающий два усилителя, выходы которых соединены с крайними выводами делителя напряжения, средний вывод которого подключен ко второму входу блока управления, третий вход которого соеди- 2О нен с выходом блока формирования относительной длительности импульса, первый и второй выходы блока проводимости подключены соответственно ко входам первого и второго усилителей бло- Я ка Линеаризации, одна обкладка сглаживающей емкости соединена с первым выходом блока проводимости, другая обкладка сглаживающей емкости подключена к шине нулевого потенциала. A так- ЗО же тем, что блок управления содержит полевой транзистор, резистор обратной связи, выходной резистор и ограничительный диод, анод которого через вы-. ходной резистор соединен с истоком полевого транзистора и с одним выводом резистора обратной связи, другой вывод которого подключен к затвору полевого транзистора, сток которого является вторым входом блока управления, катод ограничительного диода является 40 третьим входом блока управления, дру гой вывод резистора обратной связи является первым входом блока управления, анод ограничительного диода является выходом блока управления. 45

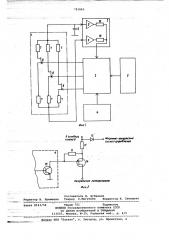

На фиг. 1,изображена функциональная схема узлового элемента, на фиг.2структура блока управленйя.

Узловой элемент состоит из блока 1 проводимости, блока 2 линеариэации, р блока 3 управления, программного блока 4, блока 5 формирования относительной длительности импульса и сглаживающей емкости б. БЛок 1 проводимости состоит иэ параллельных цепочек содеял жащих последовательно включенные резисторы 7, между которыми включеи ключ 8 на полевом транзисторе c уаравляющим Р-П-переходом. Вход и выход блока 1 проводимости соединены со входами блока 2 лвнеаризацни, состоя- 40 цего иэ двух усилителей 9, между выйодами которых включен делитель 10 напряжения на резисторах. Средний вывод делителя напряжения соединен со входом блока 3 управления. Два других выхода блока 3 управления соединены с выходом программного блока 4 и выходом блока 5 формирования относительной длительности импульса, соответственно. Выходы блока 3 управления соединены с затворами транзисторов ключей 8. К выходу блока 1 проводимости подключена сглаживающая емкость б.

Блок 3 управления состоит из нескольких одинаковых схем управления, число которых соответствует количеству параллельно соединенных цепочек в блоке 1 проводимости. Каждая схема управления выполнена на двух резисторах 11 и 12, полевом транзисторе

14 и диоде 13 (15 — выходной транзистор логики программного блока 4).

Устройство работает следующим образом.

В программном блоке 4, в цифровом коде записывается номер и одной из параллельных цепочек блока 1 проводимости. С его выхода на блок 3 управления подается сигнал, разрешающий работу только одного выбранного ключа 8. На другой вход блока 3 управления с блока 5 формирования относительной длительности импульса поступает широтно-импульсный управляющий сигнал. Блок 3 управления вырабатывает сигнал, синхронный с сигналом ф который управляет ключом 8 на полевом транзисторе. Средняя за период величина проводимости складывается из двух ее дискретных значений 6„ — в момент, когда ключ 8 замкнут и Π— когда ключ 8 разомкнут. На емкости б пульсации напряжения, вызванные импульсной модуляцйей проводимости, сглаживаются. В результате чего среднее значение проводимости за период определяется формулой =Ж 8 — средняя эа период проводимость, соответствующая

<=1,2,3

— величина постоянной проводимости, соответствующая—

М-ому разряду.

Средняя эа период проводимость оказывается пропорциональна относительной длительности импульса широтноtU импульсного сигнала = где

Т Ю цлительность импульса; Т вЂ” период квантования, и величине постоянной проводимости 6В °

Кроме того, сглаживающая емкость б может быть. использована для моделиро.вания дйнамических Свойств объекта с распределенйыми параметрами при решении нестационарных задач. Для стабилизации сопротивления открытого канала полевого транзистора, при изменении входного и выходного потенциала блока 1 проводимости, применяется блок 2 линеаризации. Потенциалы входа и выхода блока 1 проводимости через усилители 9,.служащие для развязки, по781842 ступают на реэистивный делитель напряжения на резисторах 10, с которого снимается полуразность поданных напряжений. Из теории полевых транзисторов известно, что стабилизация сопротивления канала или линеариэация возю можна при подаче на затвор половины разности напряжений стока и йстока.

Если учесть, что величина сопротивления резисторов 7 каждой иэ цепочек блока 1 проводимости одинакова, а следовательно, одинаковы и падения напряжения на них, то на выходе делителя блока 2 линеаризации выделяется только полуразность напряжений между сгоком и истоком транзистора, так как равные падения напряжения на резисторах 7 компенсируются. Напряжение линеаризации с помощью блока 3 управления подается на затвор выбранного транзистора в моменты отпирания ключа. 20

Блок управления работает следующим образом.

При сигнале "Логическая 1" с выхода соответствующей схемы программного блока 4 закрывается выходной транзистор 15.логики. Исток и затвор транзистора 14 оказываются связанными через резистор 11 и транзистор открывается, при этом на истоке его присутствует напряжение линеаризации.

При подаче запирающего значения широтно-импульсного управляющего сигнала с блока 5 формирования относительной длительности импульса диод

13 открывается и на затвор ключа 8 подается низкий запирающий.потенциал.

При отпирающем значении широтноимпульсного сигнала диод 13 закрыт и на затвор ключа 8 через транзистор

14 и резистор 12 подается напряжение линеаризации. 40

При сигнале "Логический 0" на выходе блока 4 на затвор транзистора 14 подается нулевой потенциал. Транзистор 14 и резистор 11 представляют собой генератор тока малой величины, поскольку резистор 11 выбирается высокоомным, включенный между источником напряжения линеариэации и шиной нулевого потенциала. Омическое сопротивление канала транзистора 14 практически равно дифференциальному . сопротивлению стабилизатора тока. Поэтому напряжение линеаризации оказывается практически отключенным от затвора ключа 8. На резисторе 11 выделяется напряжение, примерно равное напряжению отсечки транзистора 14 и которое закрывает ключ 8.

Предлагаемые блоки и связи между ними повышают точность и упрощают схему узлового элемента сеточной модели.

Формула изобретения

1. узловой элемент сеточной модели, содержащий блок проводимости, входы которого соединены с ныходами блока управления, первый вход которого подключен к выходу программного блока, отличающийся тем, что, с целью упрощения и повышения точности, в него введены блок формирования относительной длительности импульса, сглаживающая емкость и блок линеаризации, нключающий два усилителя, выходы которых соединены с крайними выводами делителя напряжения, средний вывод которого подключен ко второму входу блока управления, третий вход которого соединен с выходом блока формирования относительной длительности импульса, первый и второй выходы блока проводимости подключены соответственно ко входам первого и второго усилителей блока линеаризации, одна обкладка сглаживающей емкости соединена с первым выходом блока проводимости, другая обкладка сглаживающей емкости подключена к шине нулевого потенциала.

2. Узловой элемент по п. 1, о т л и ч а ю шийся тем, что блок управления содержит полевой транзистор, резистор обратной связи, выходной резистор и ограничительный диод, анод которого через выходной резистор соединен с истоком полевого транзистора и с одним выводом резистора обратной связи, другой вывод которого подключен к затвору полевого транзистора, сток которого янляется вторым входом блока управления, катод ограничительного диода является третьим входом блока упранления, другой вывод резистора обратной связи является первым входом блока управления, анод ограничительного диода является выходом блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 417803,G 06 6 7/48, 1972.

2. Авторское свидетельство СССР

9 547790, G 06 G 7/46, 1975 (прототип).

781842

Фиг.1

Яиратнф-цмщлвсныи сигнал уирабления

Составитель И. Дубинина

Редактор В. Еремеева Техред С.Мигунова Корректор В. Синицкая

Заказ 8143/56 Тираж 751 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и бткфятий

113035, Москва, Ж-35, Раушская наб., д. 4/5

«й,hi » «ЙЫМЫый з»

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

3éé ="